CMPE 212

Back

Materials to Review for Quiz 1:

Materials included here do not belong to me, any request to take down and I will do so

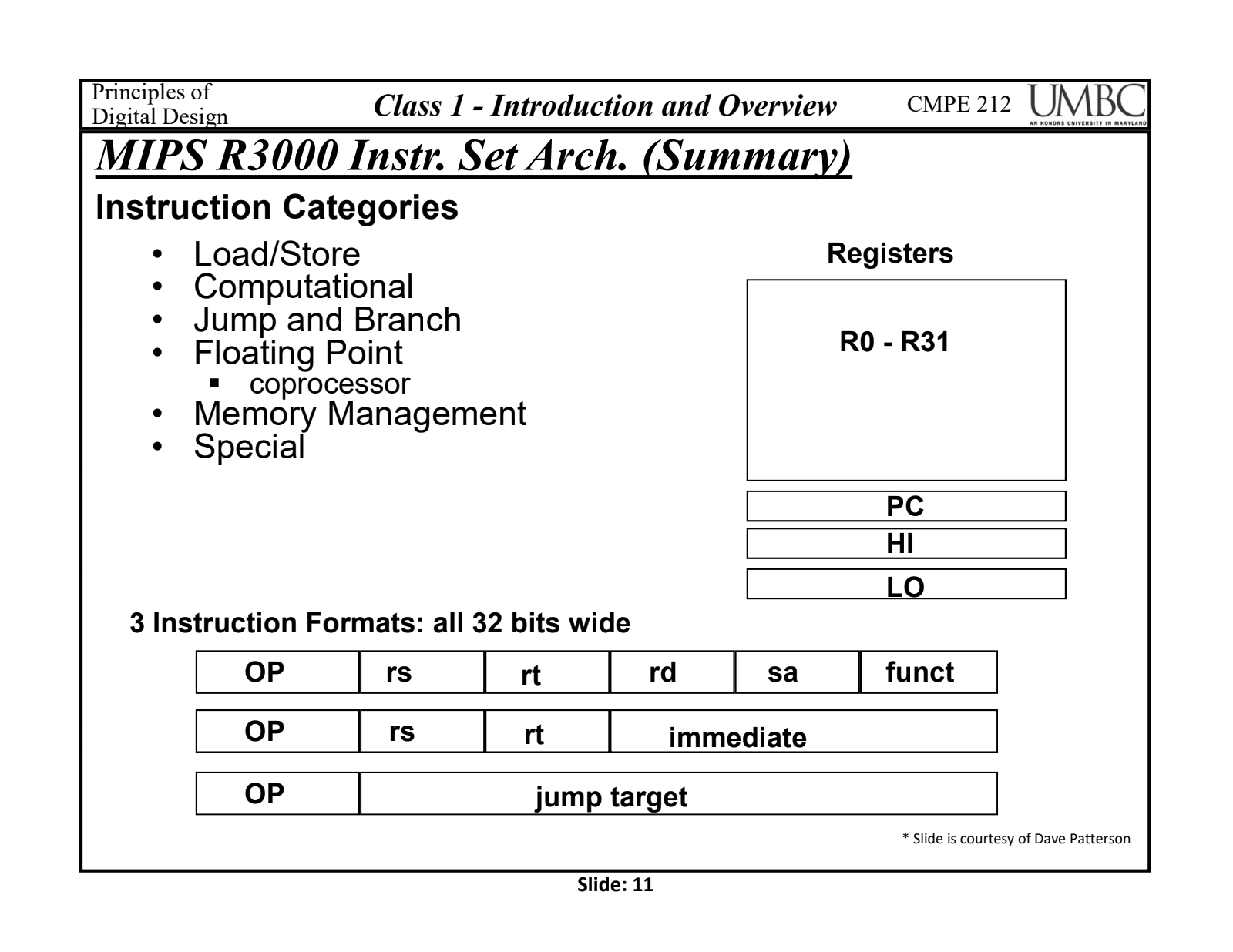

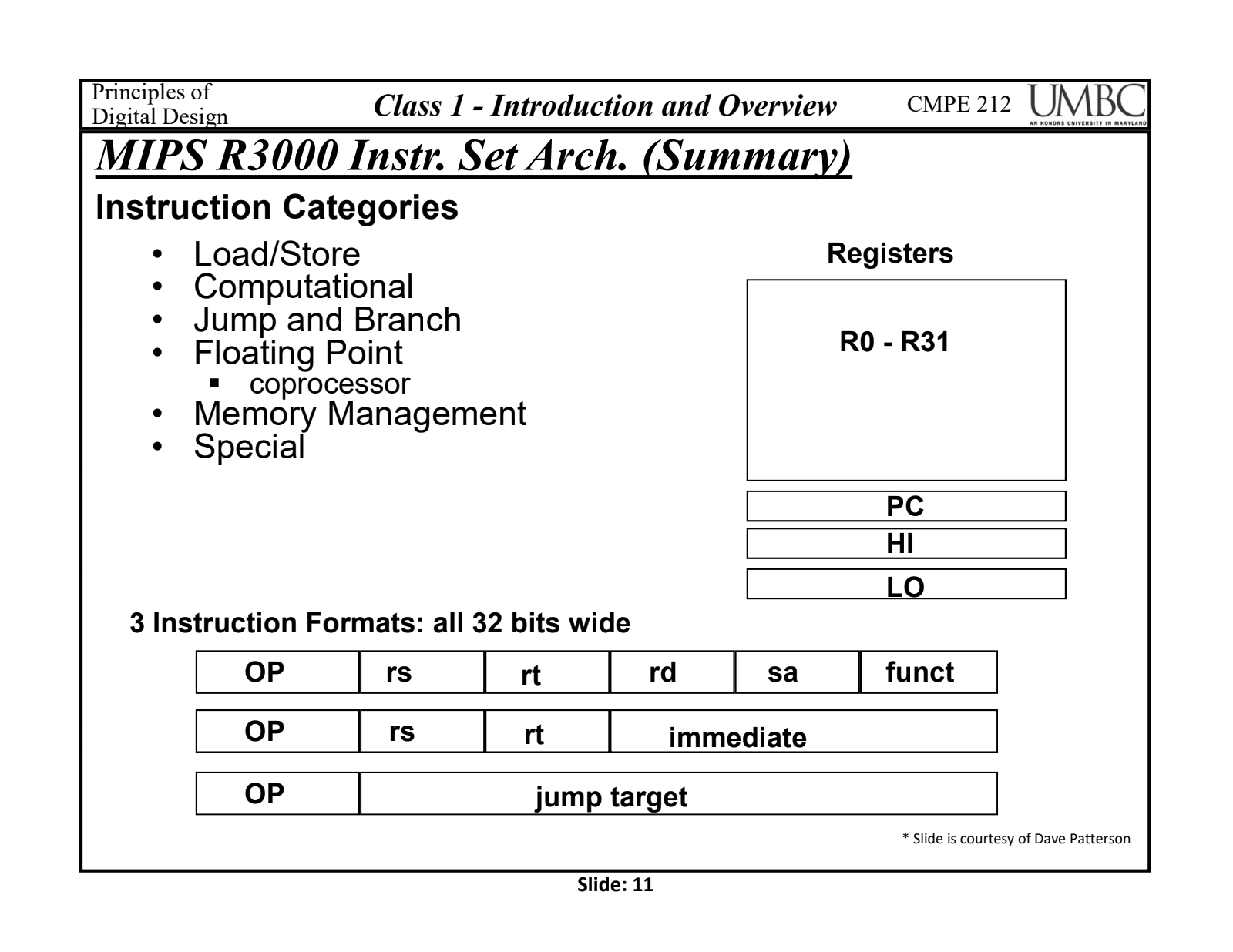

Class: 1, slide: 11 → General Computer Organization

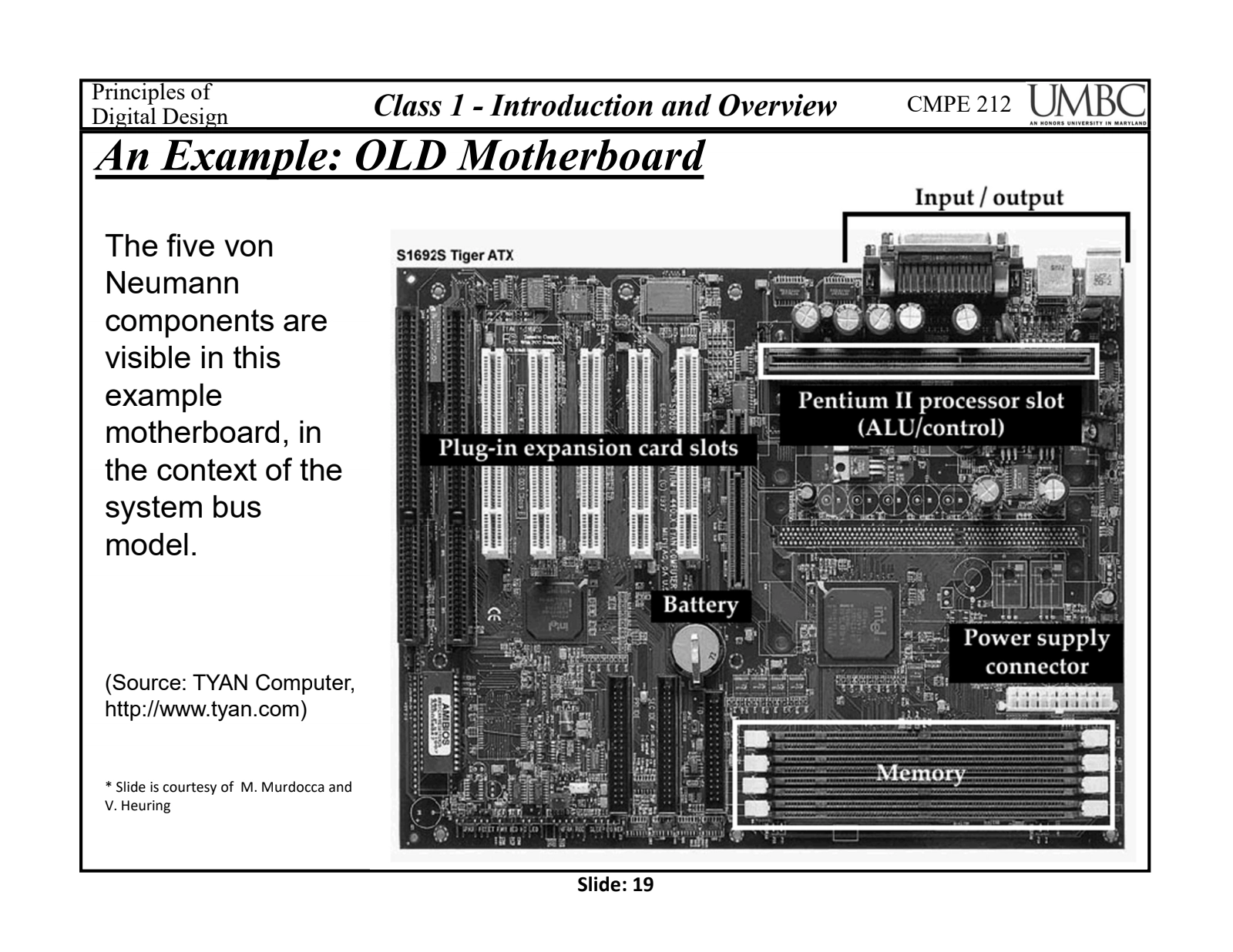

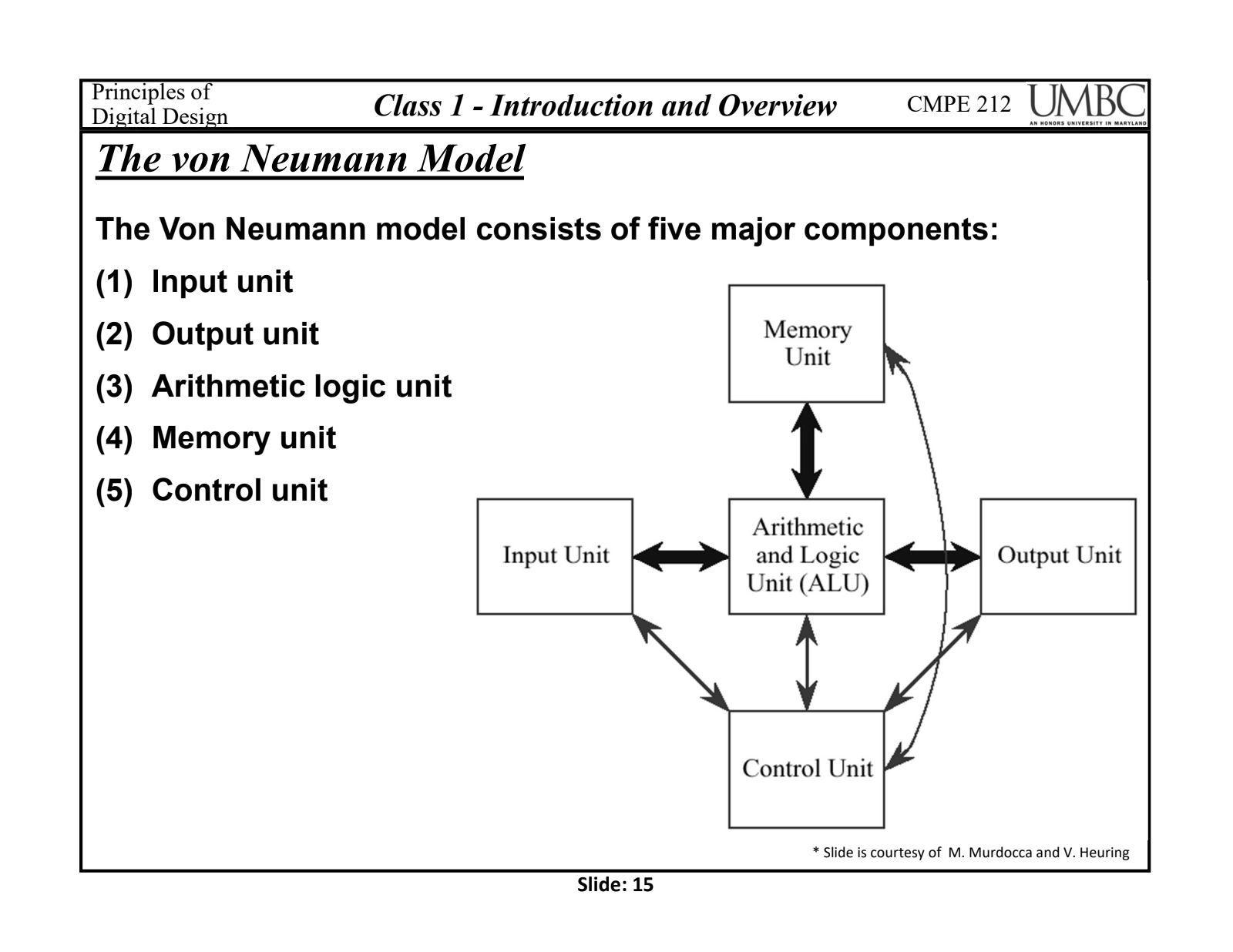

Class: 1, slide: 15 → System Bus Model

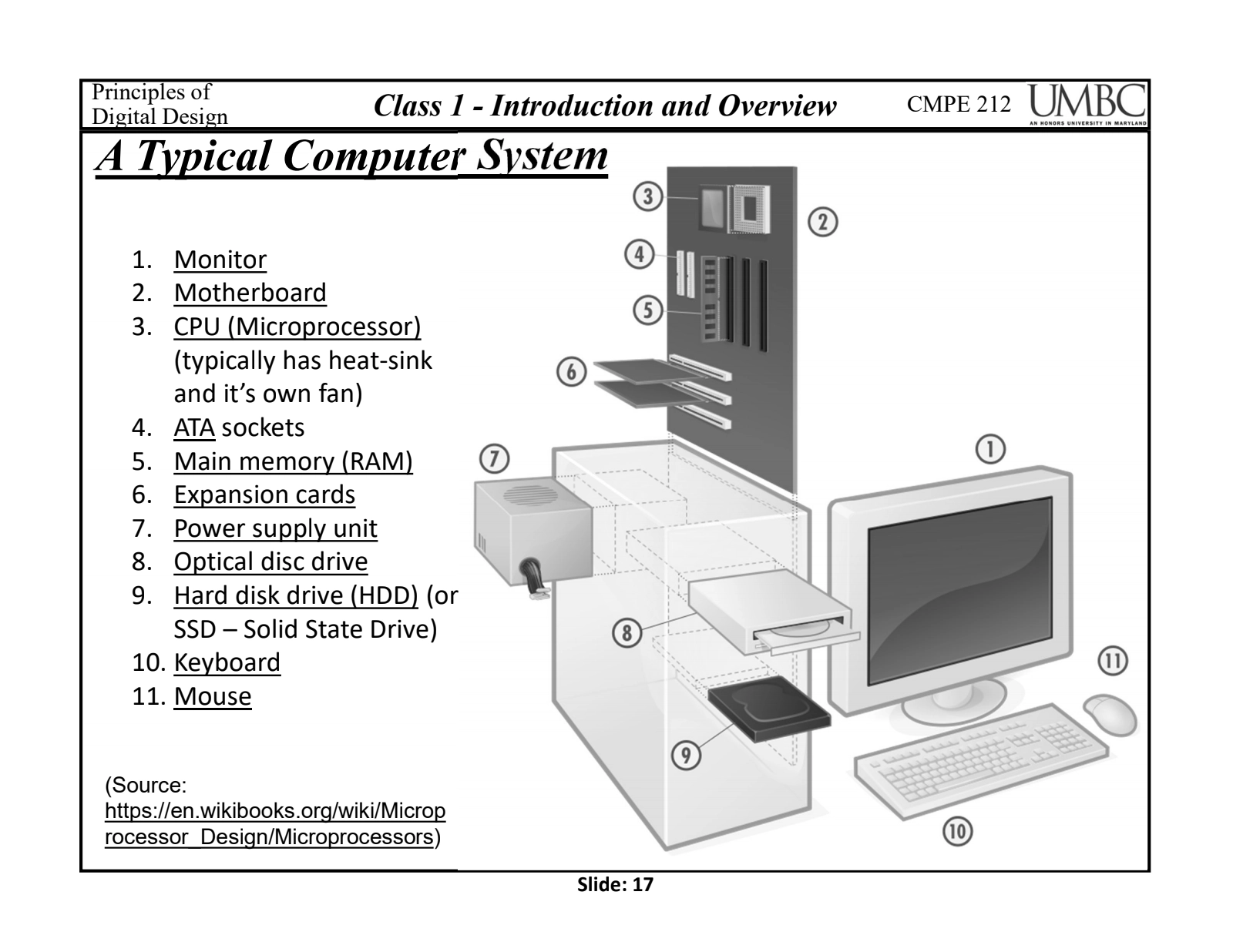

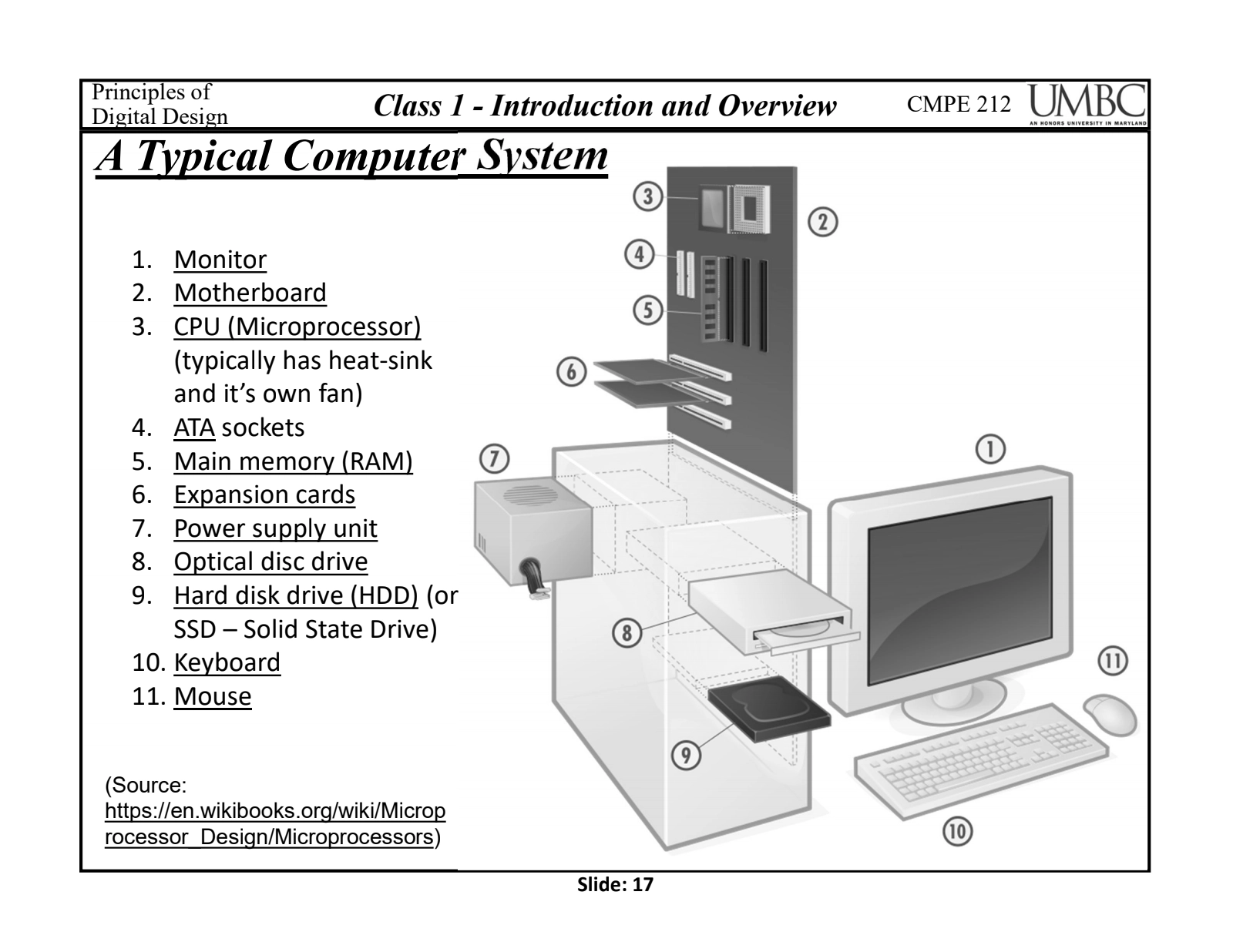

Class: 1, slide: 17 → An Example Motherboard

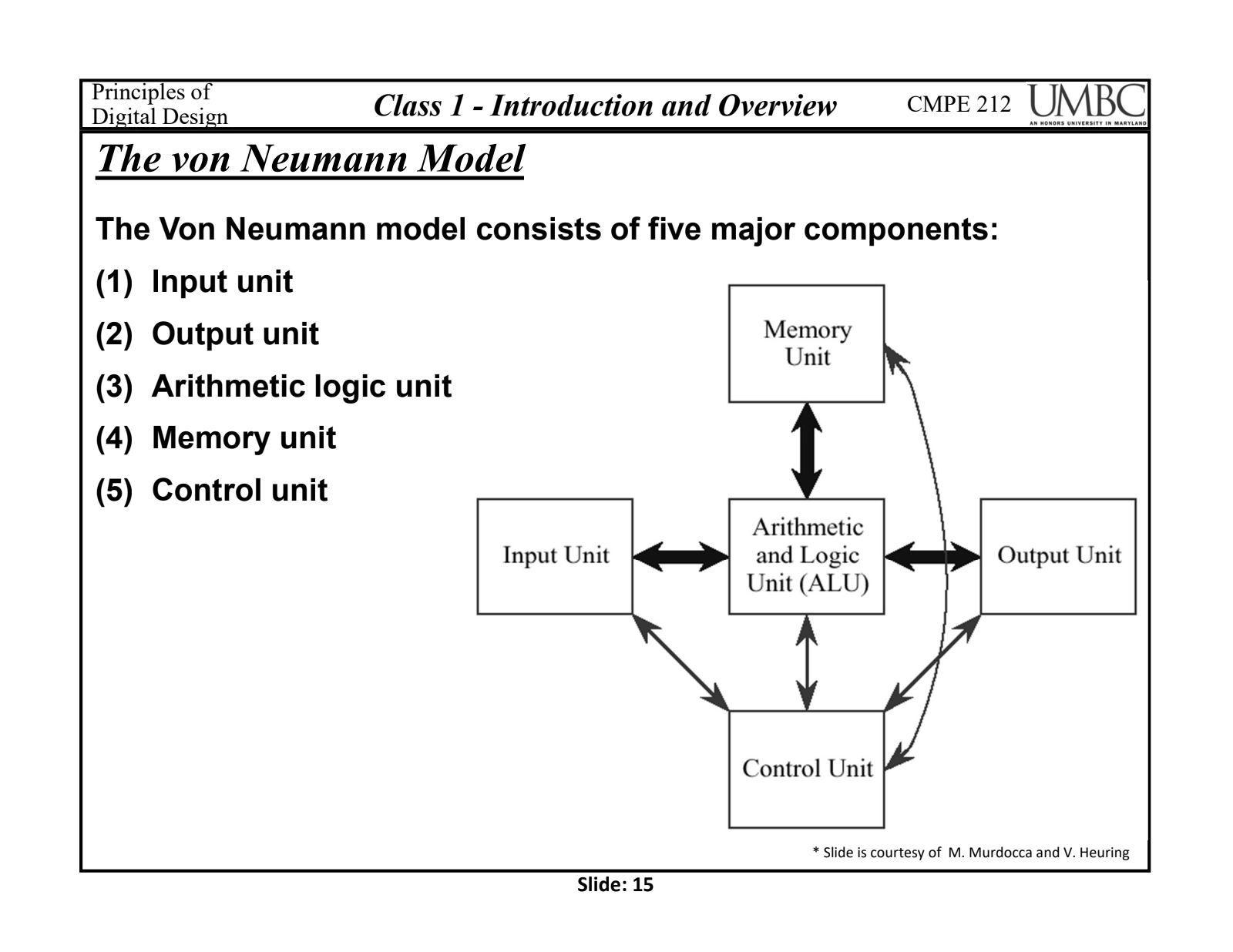

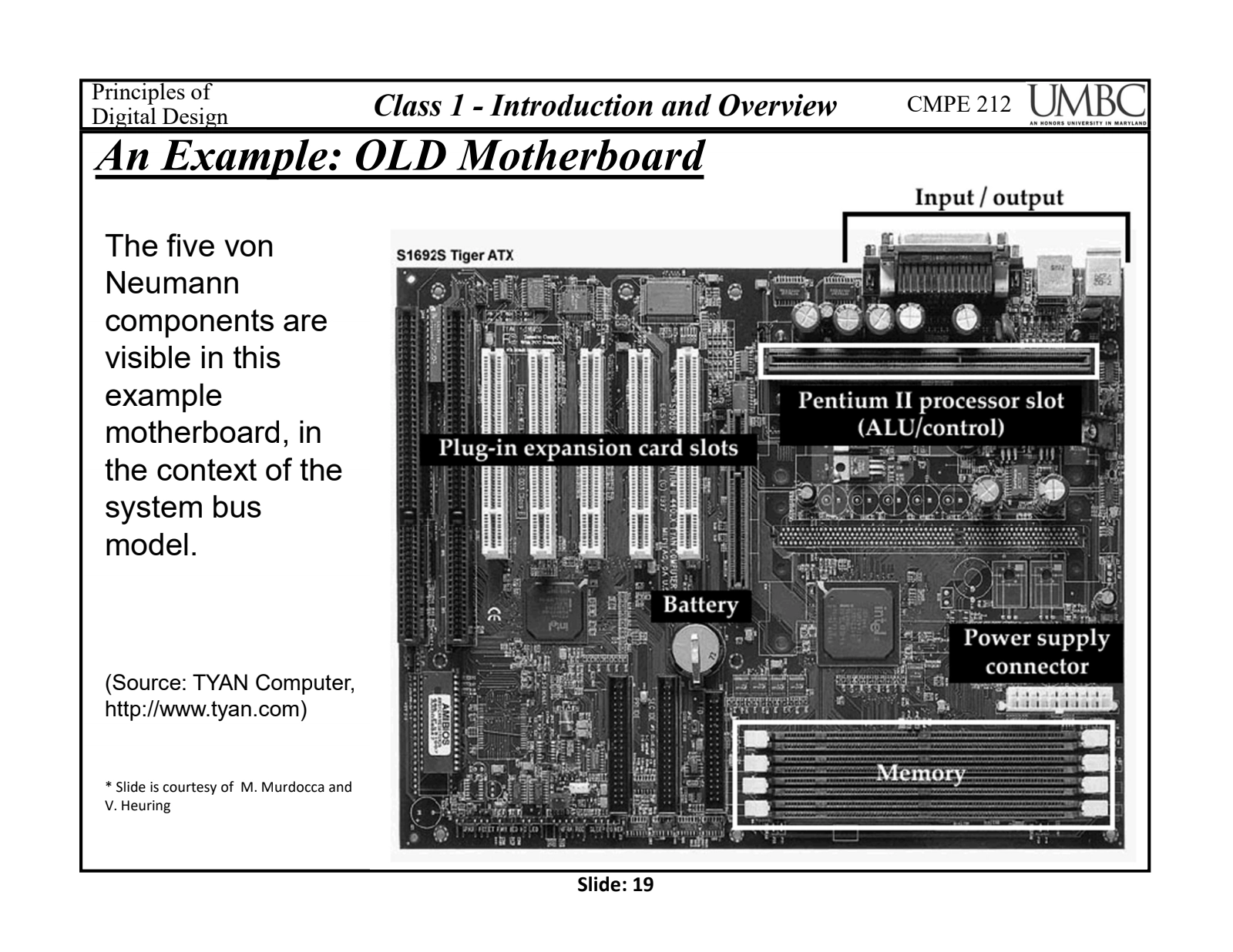

Class: 1, slide: 19 → Execution Cycle - Von Neuman Model

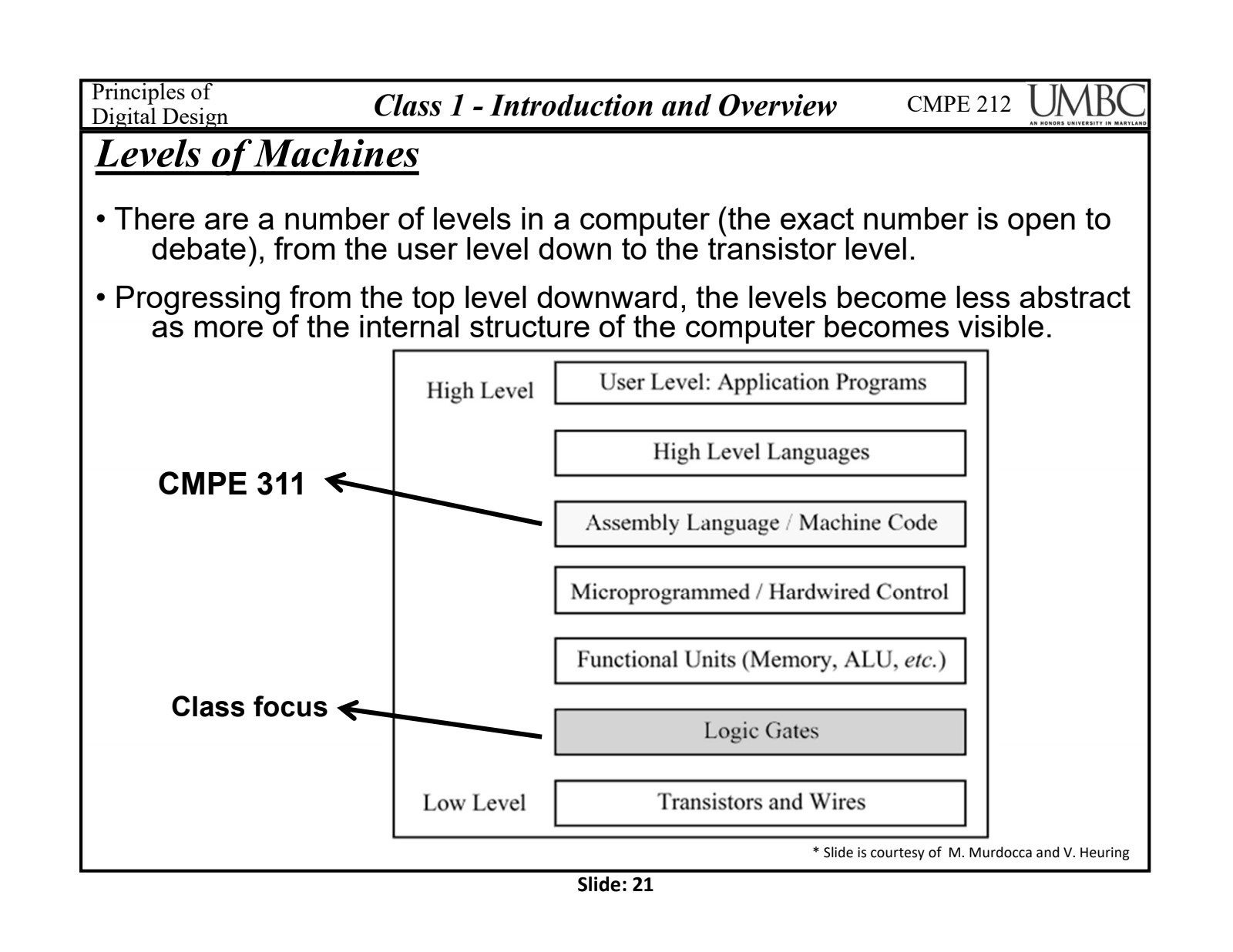

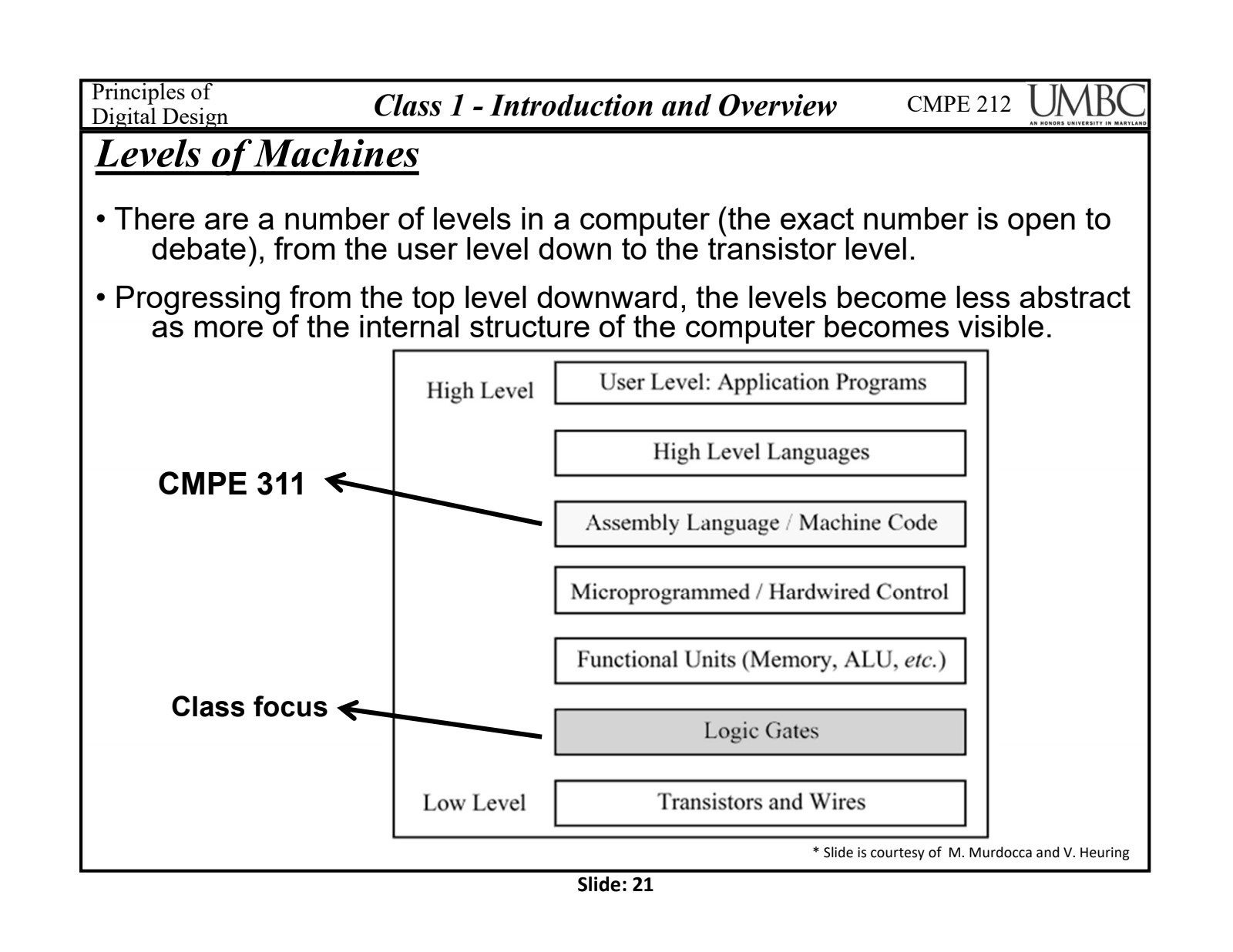

Class: 1, slide: 21 → Levels of Abstraction

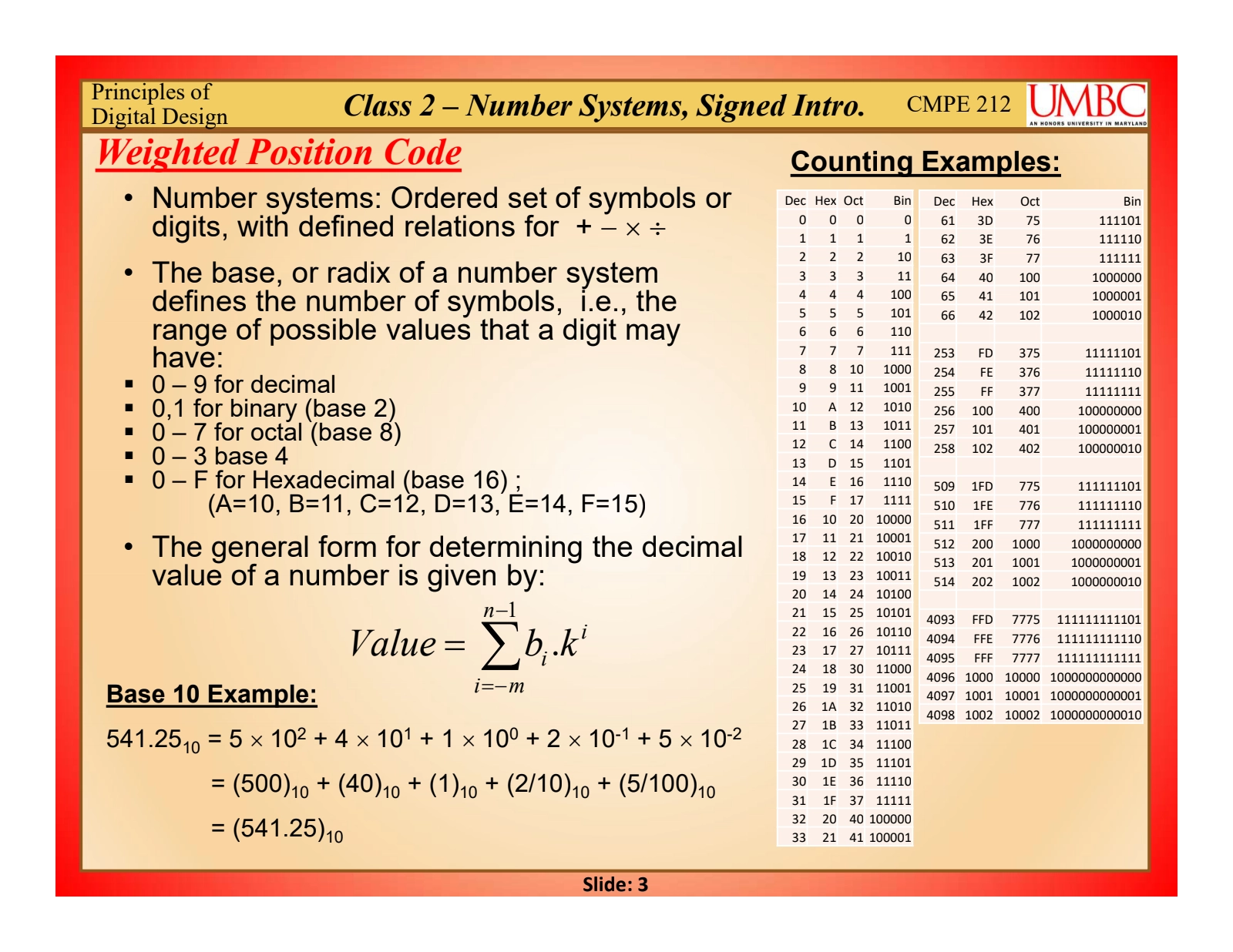

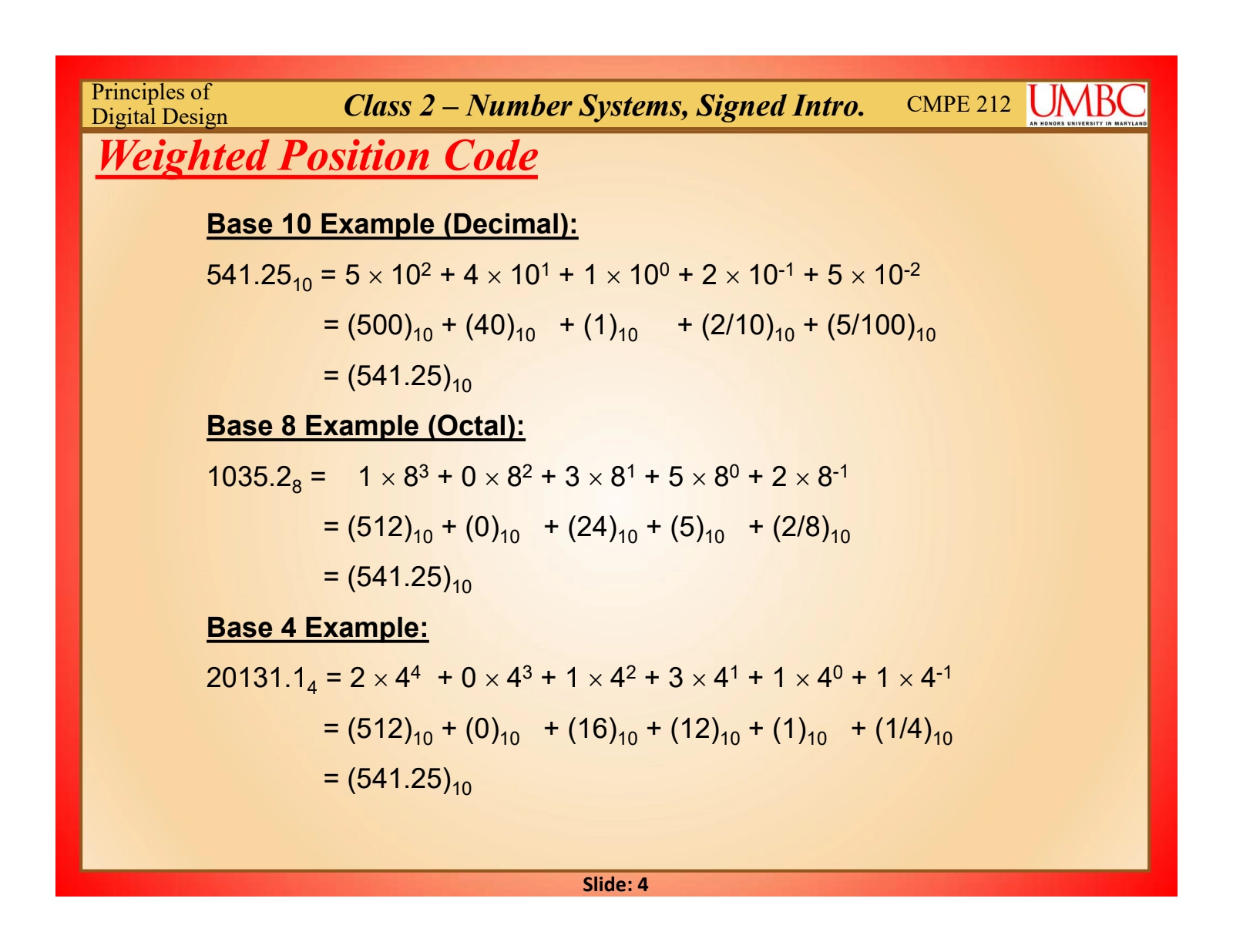

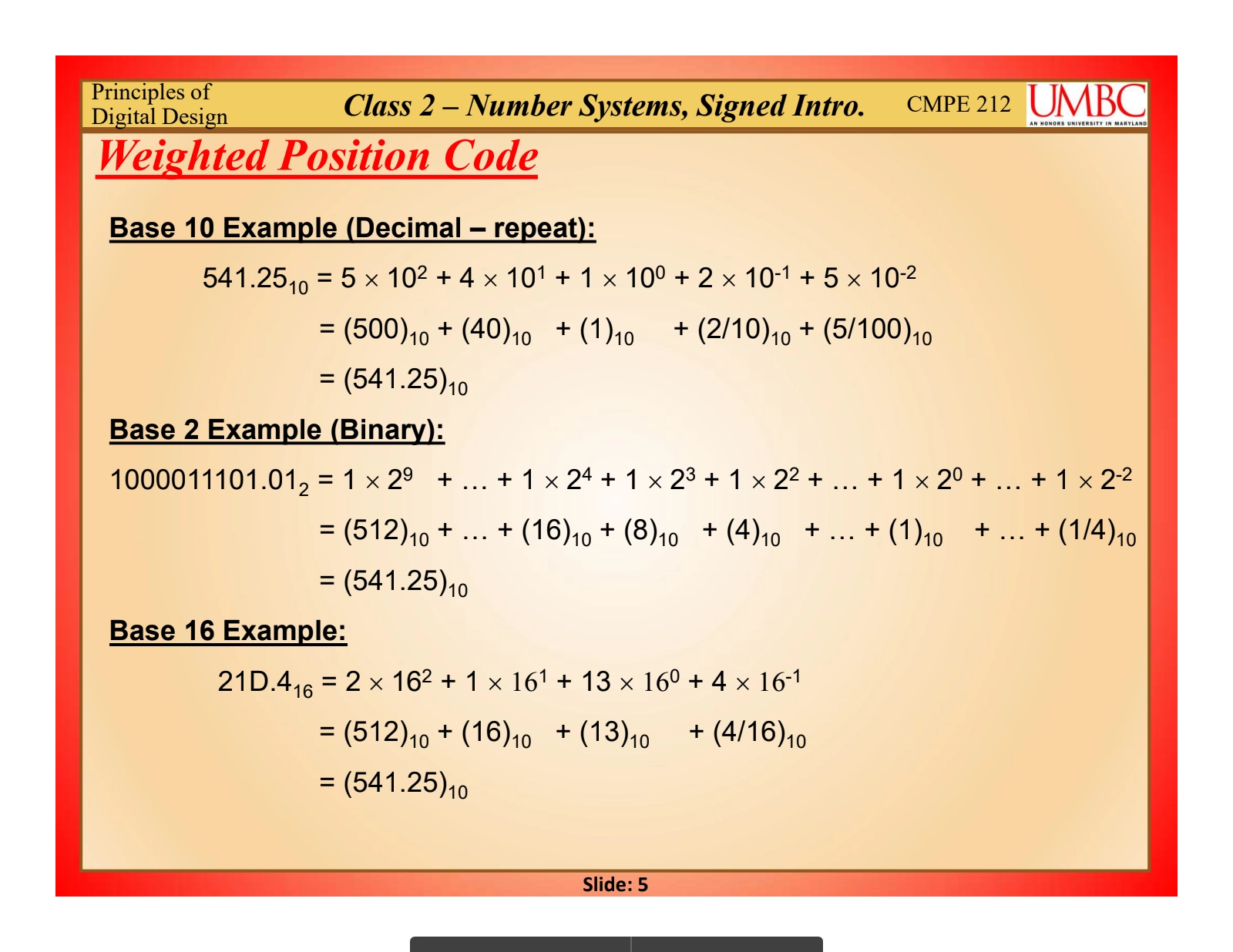

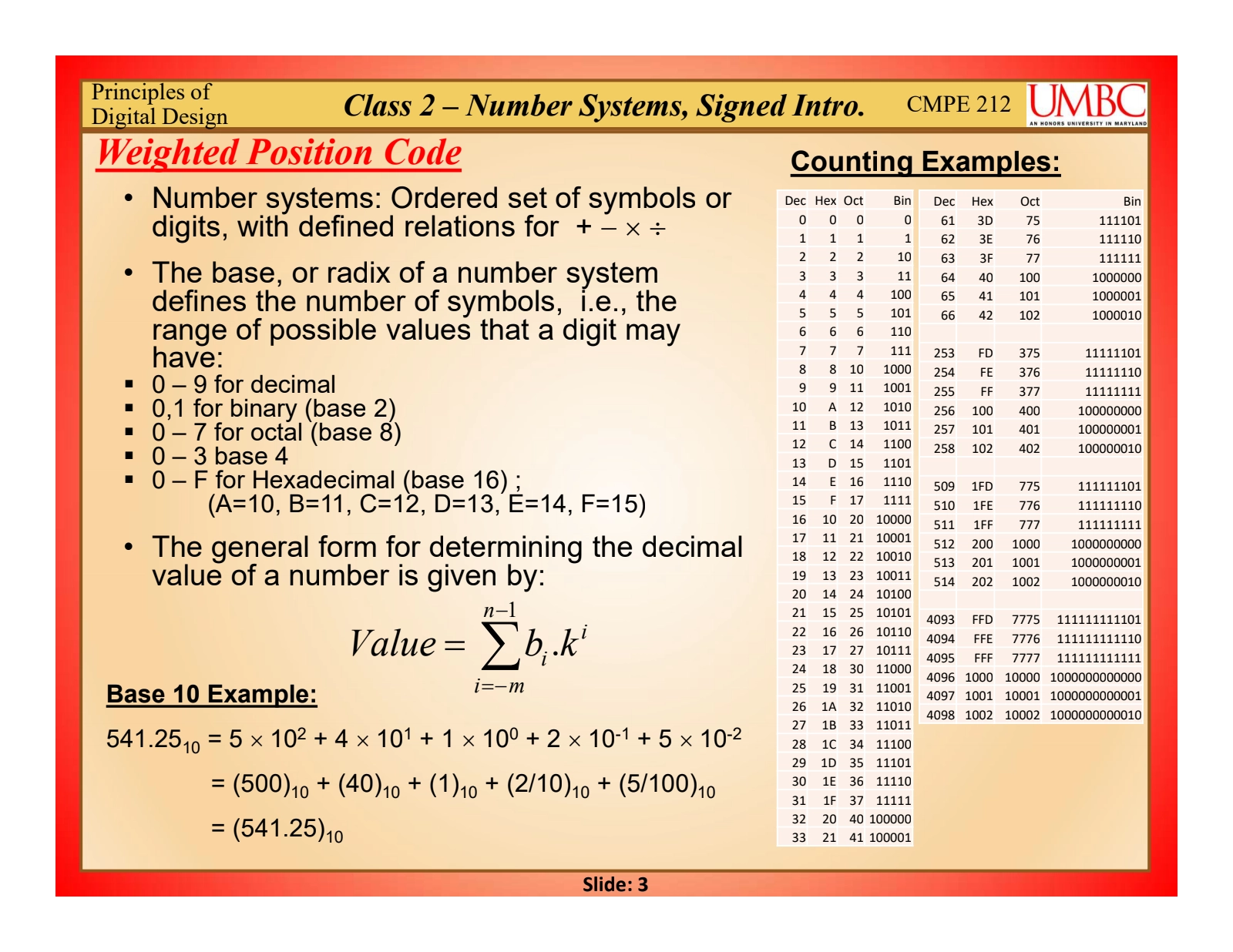

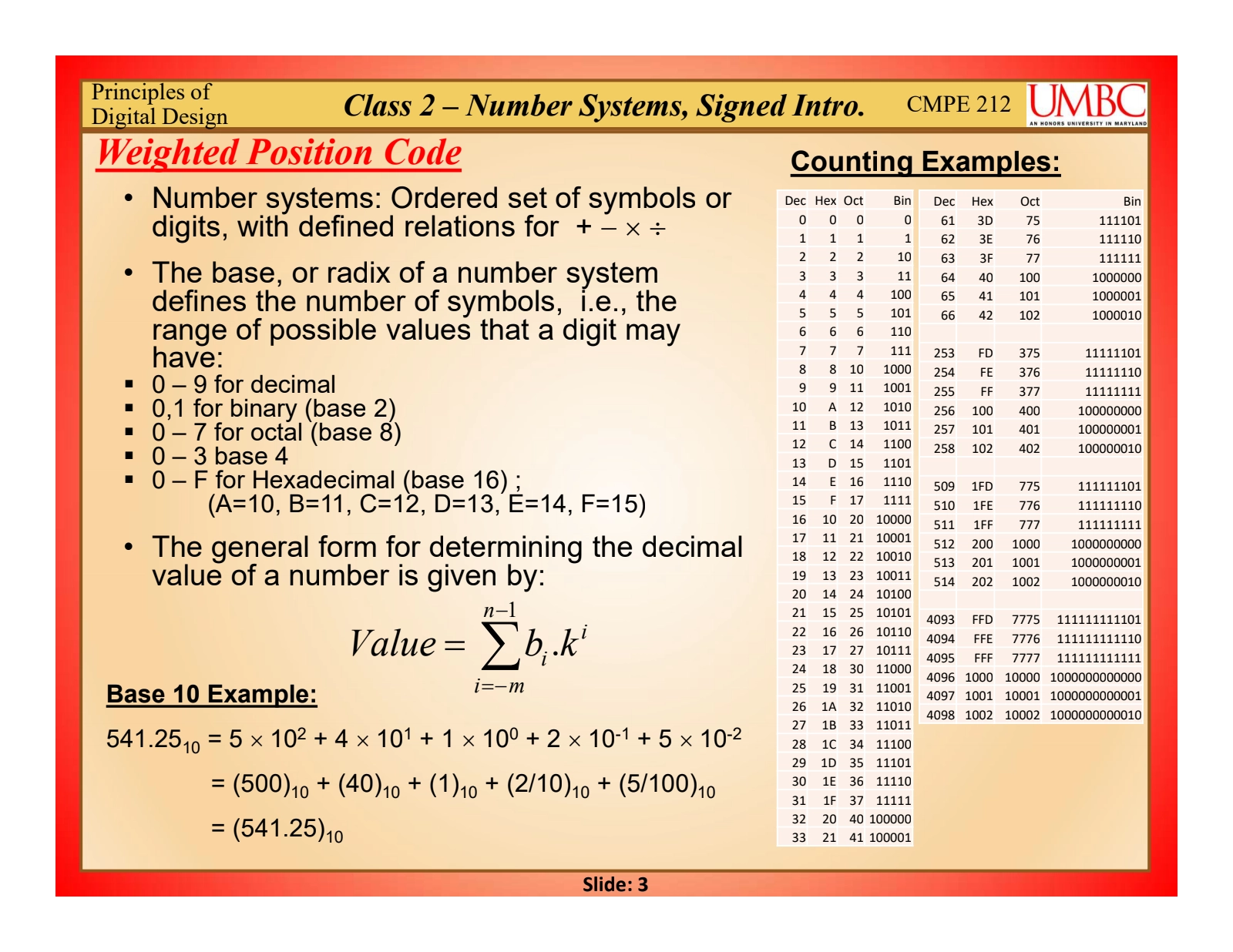

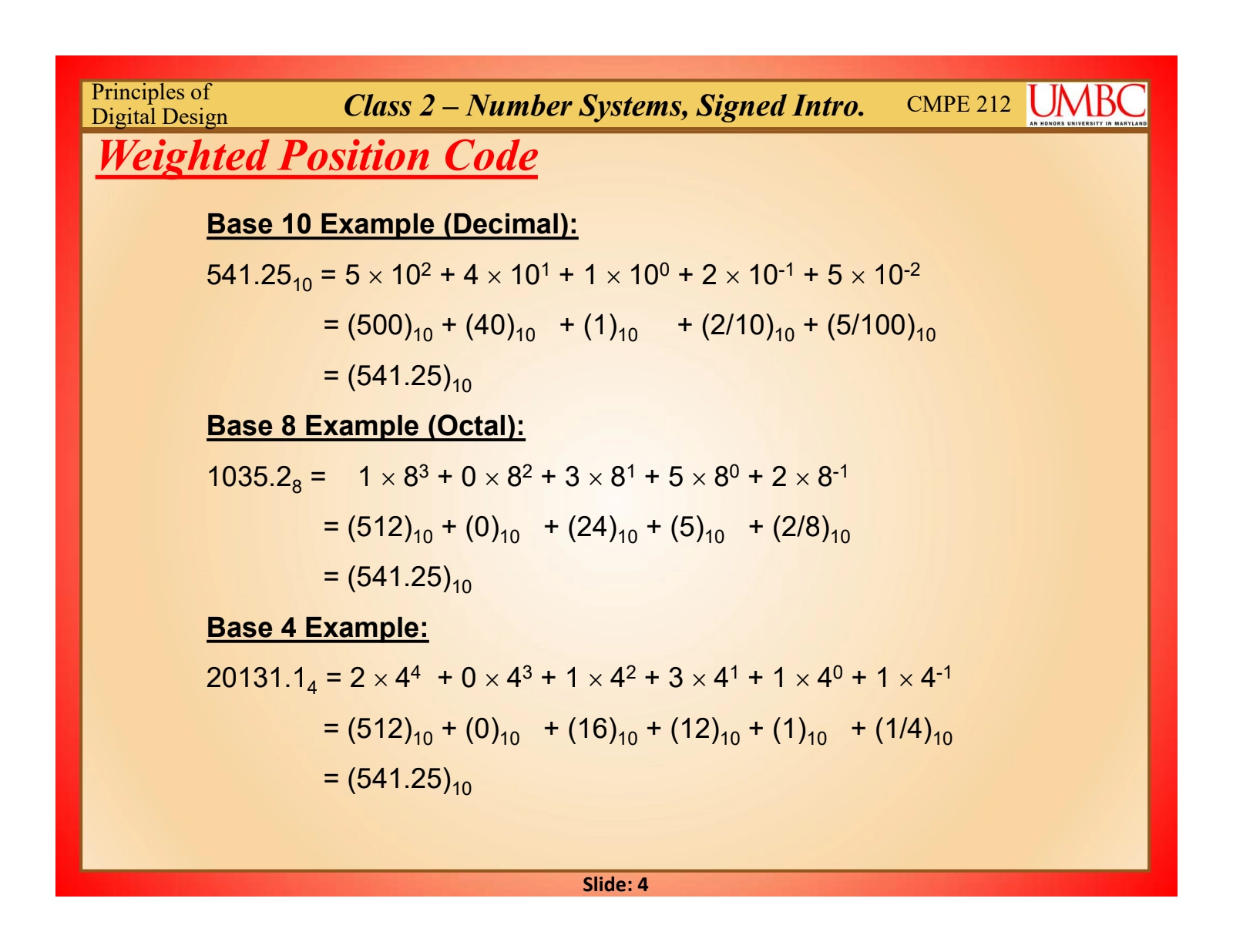

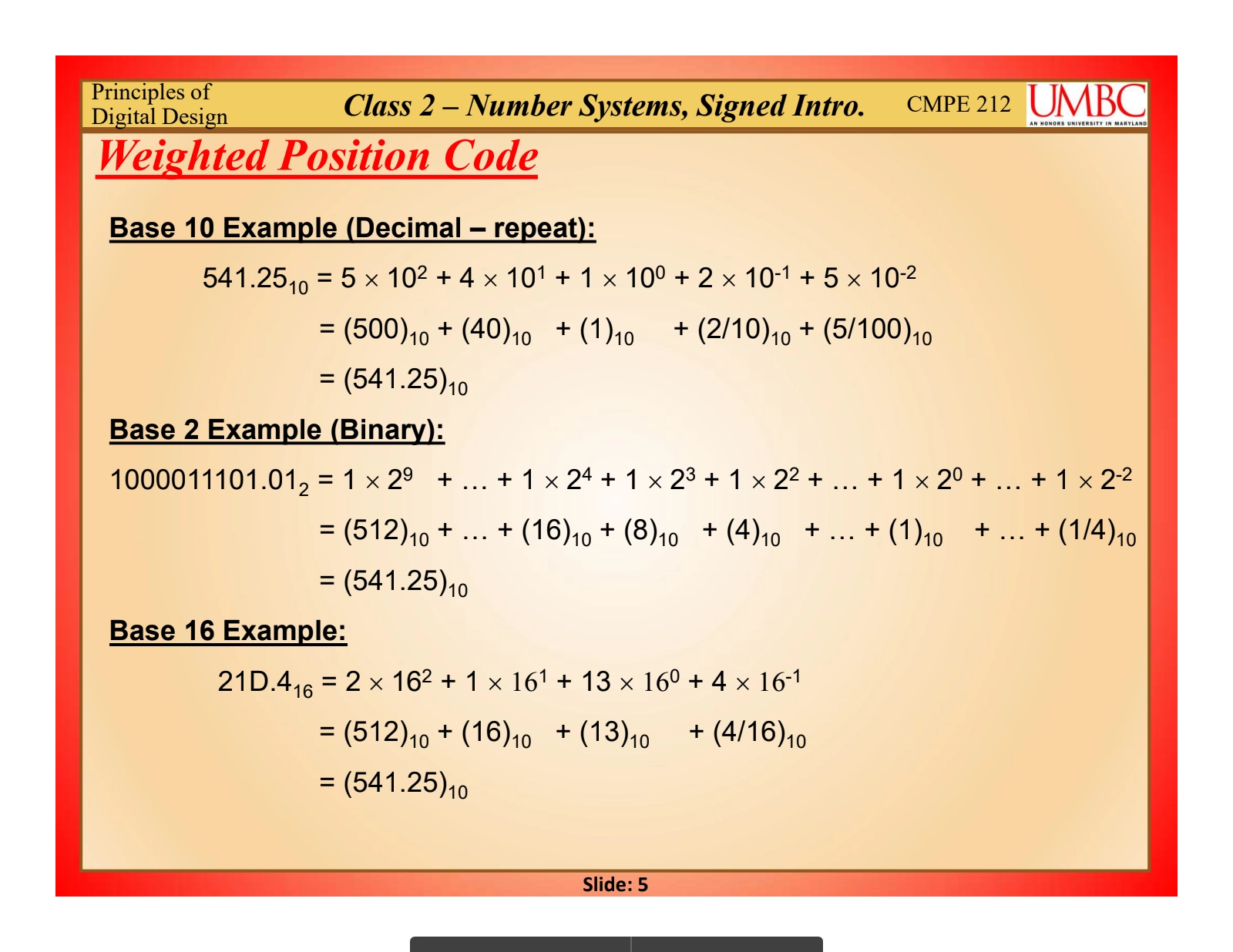

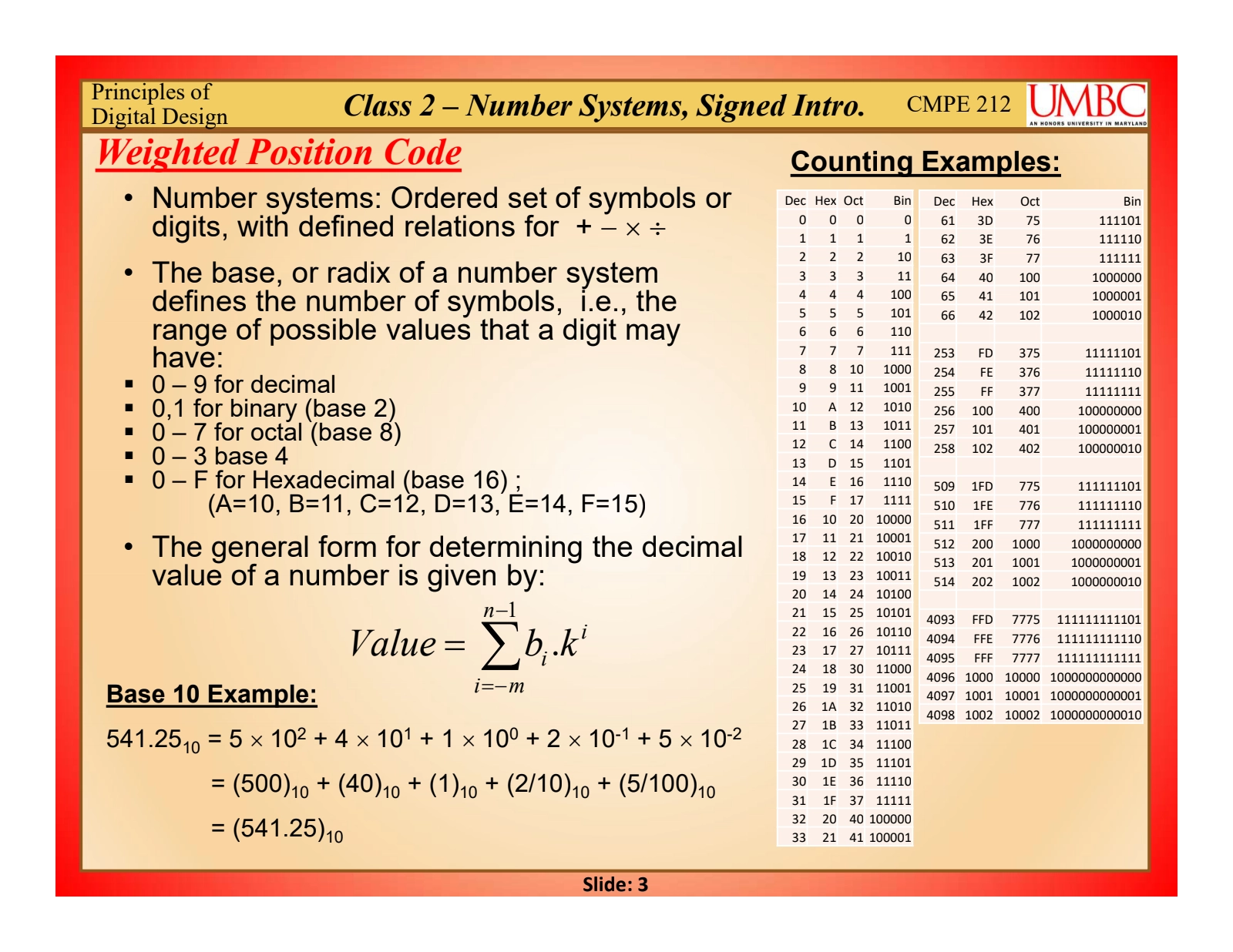

Class: 2, slide: 3,5 → Converting Base 2 to Base 10

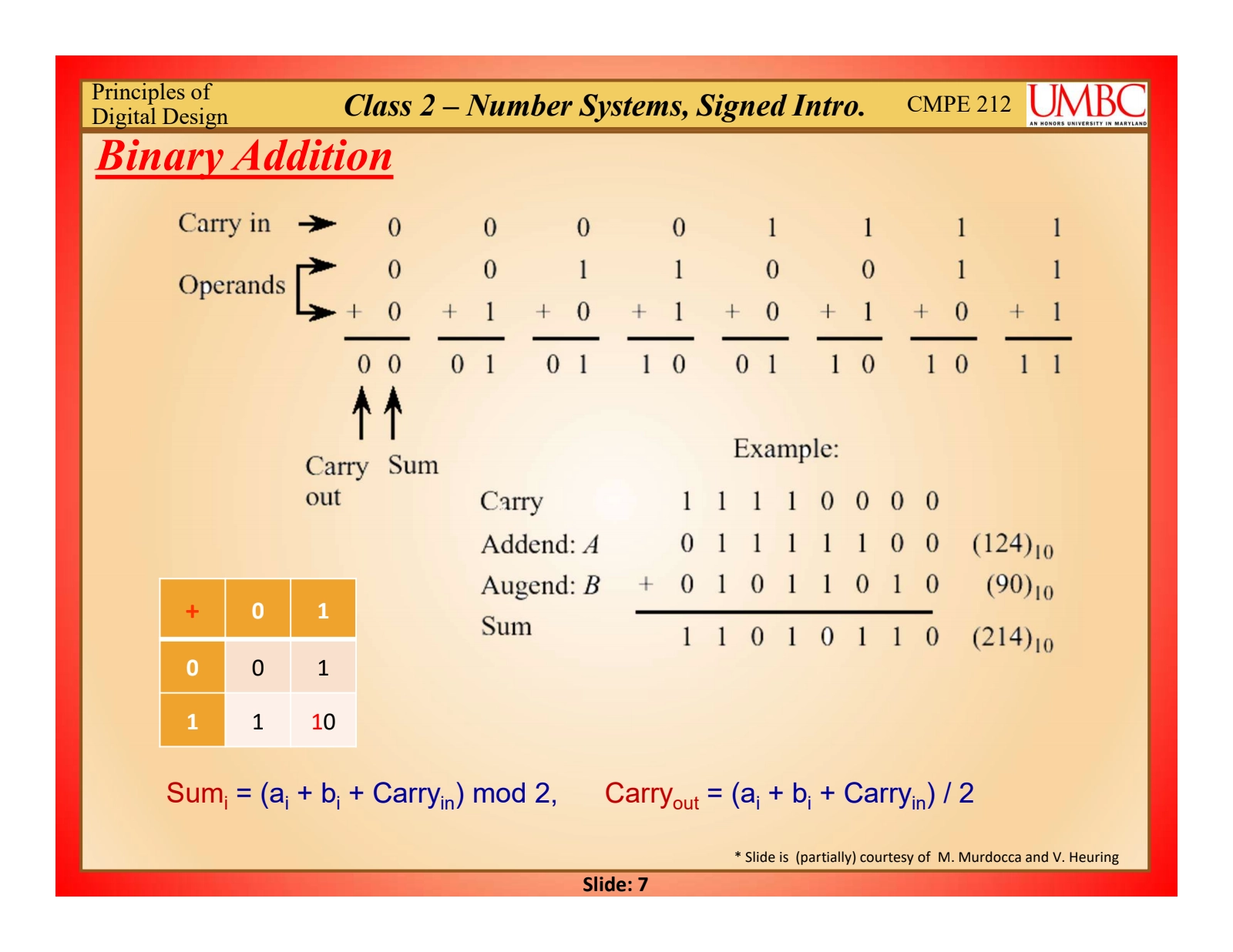

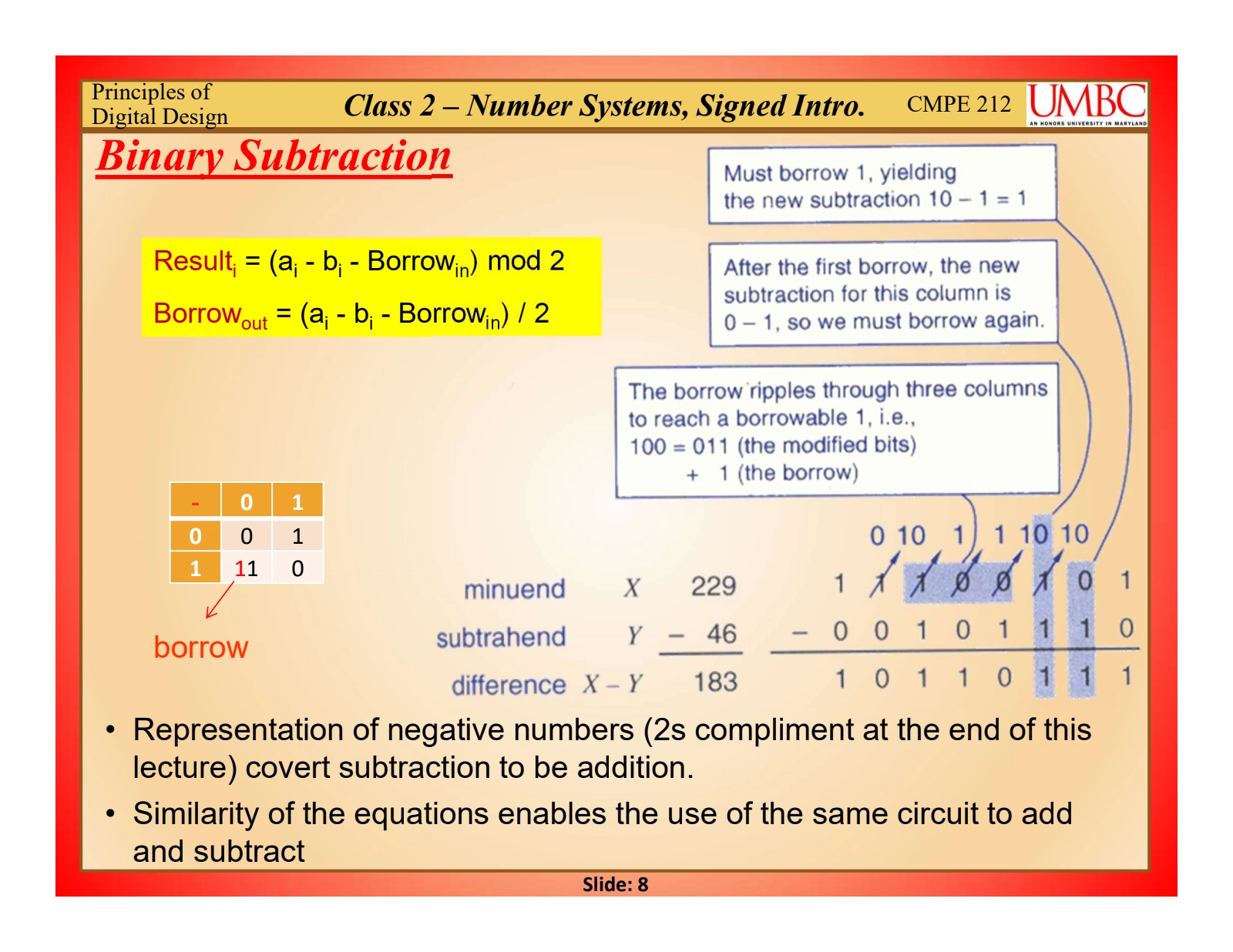

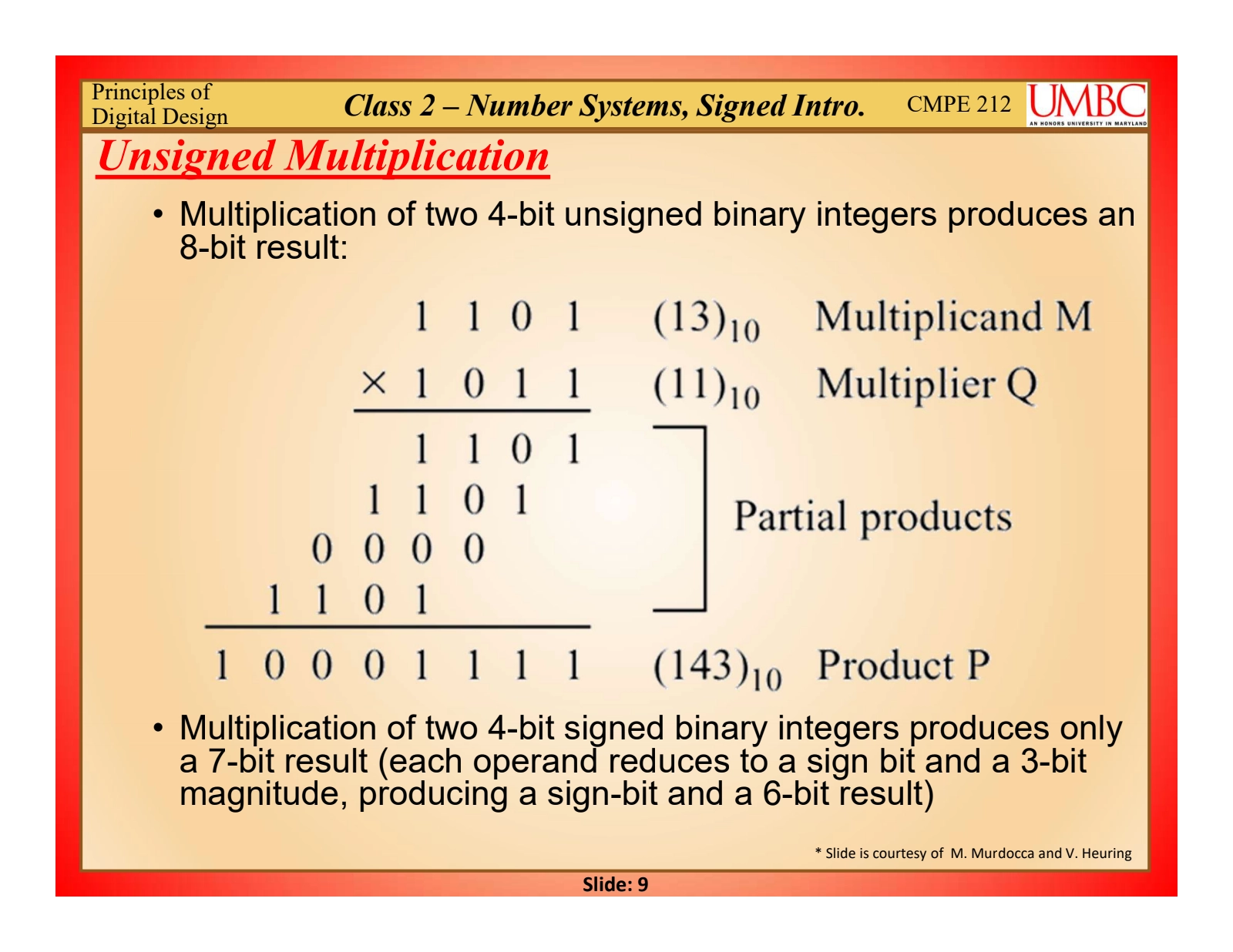

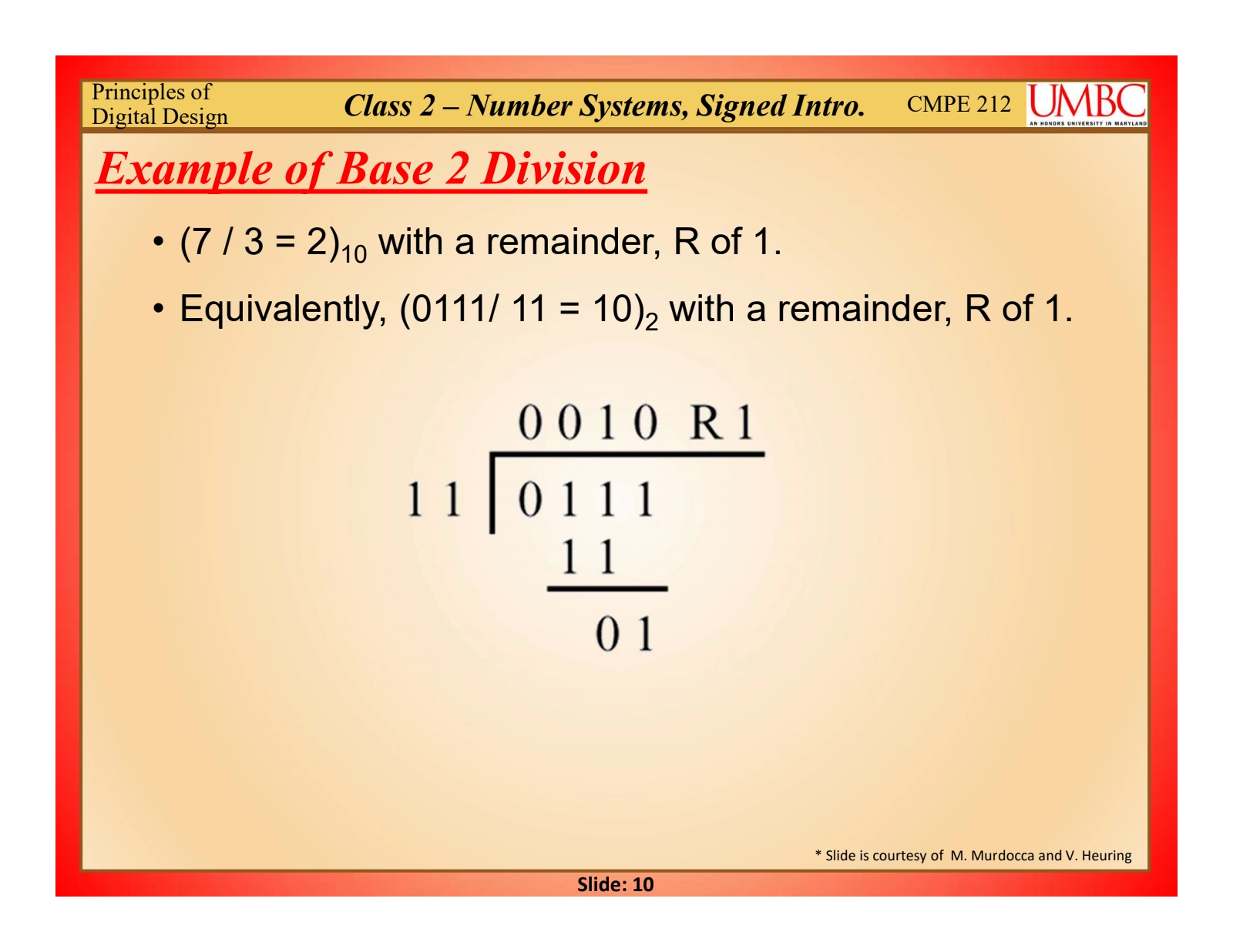

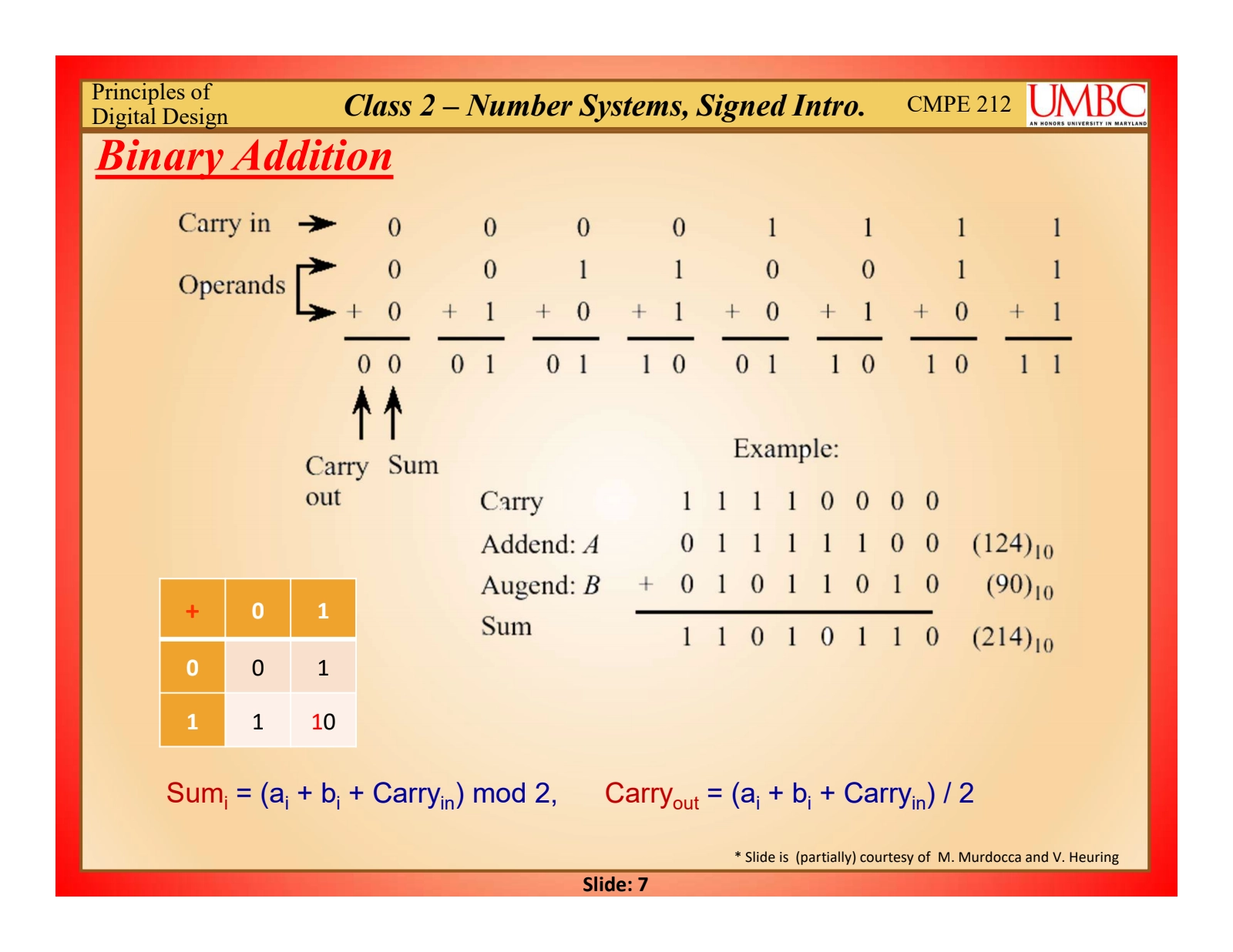

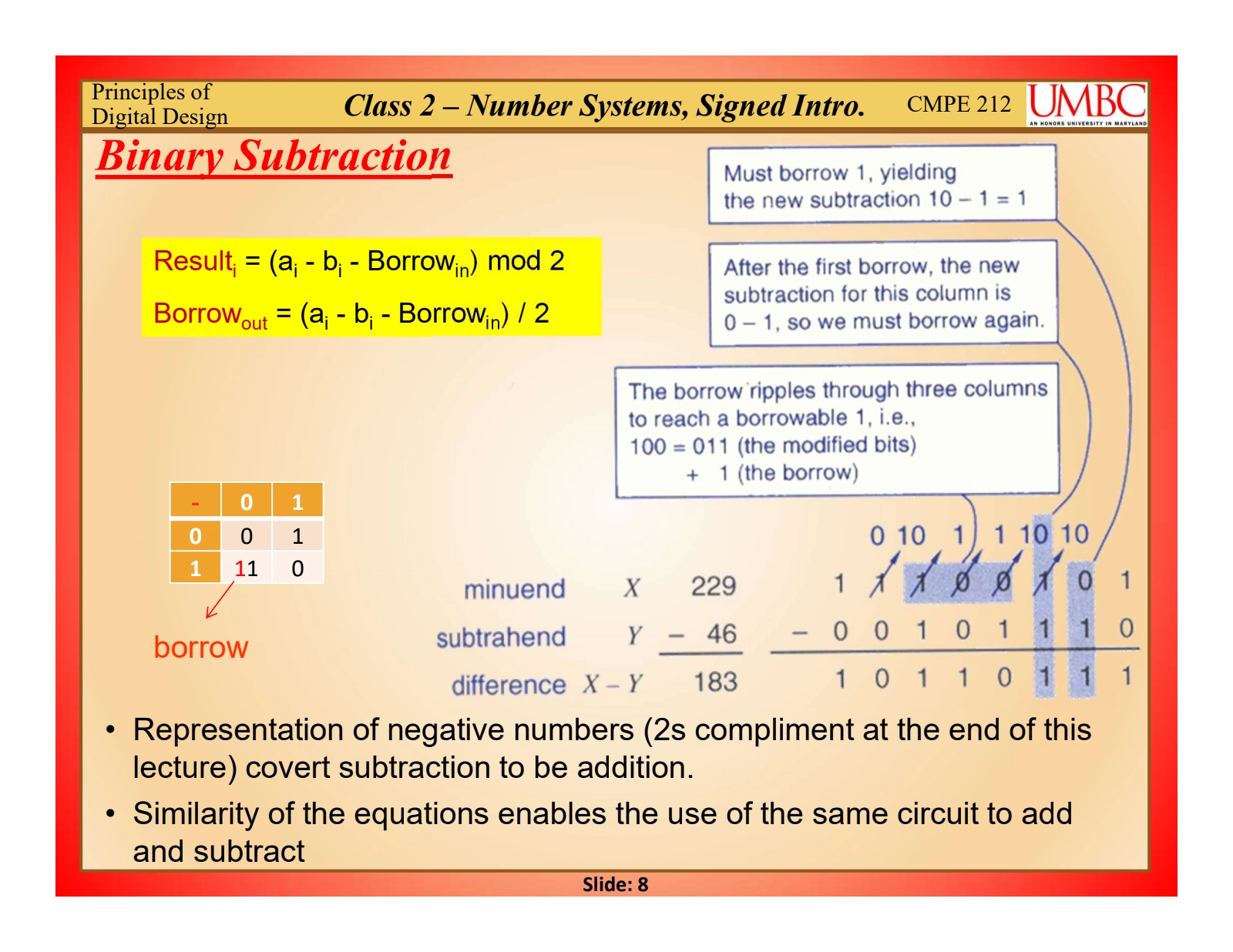

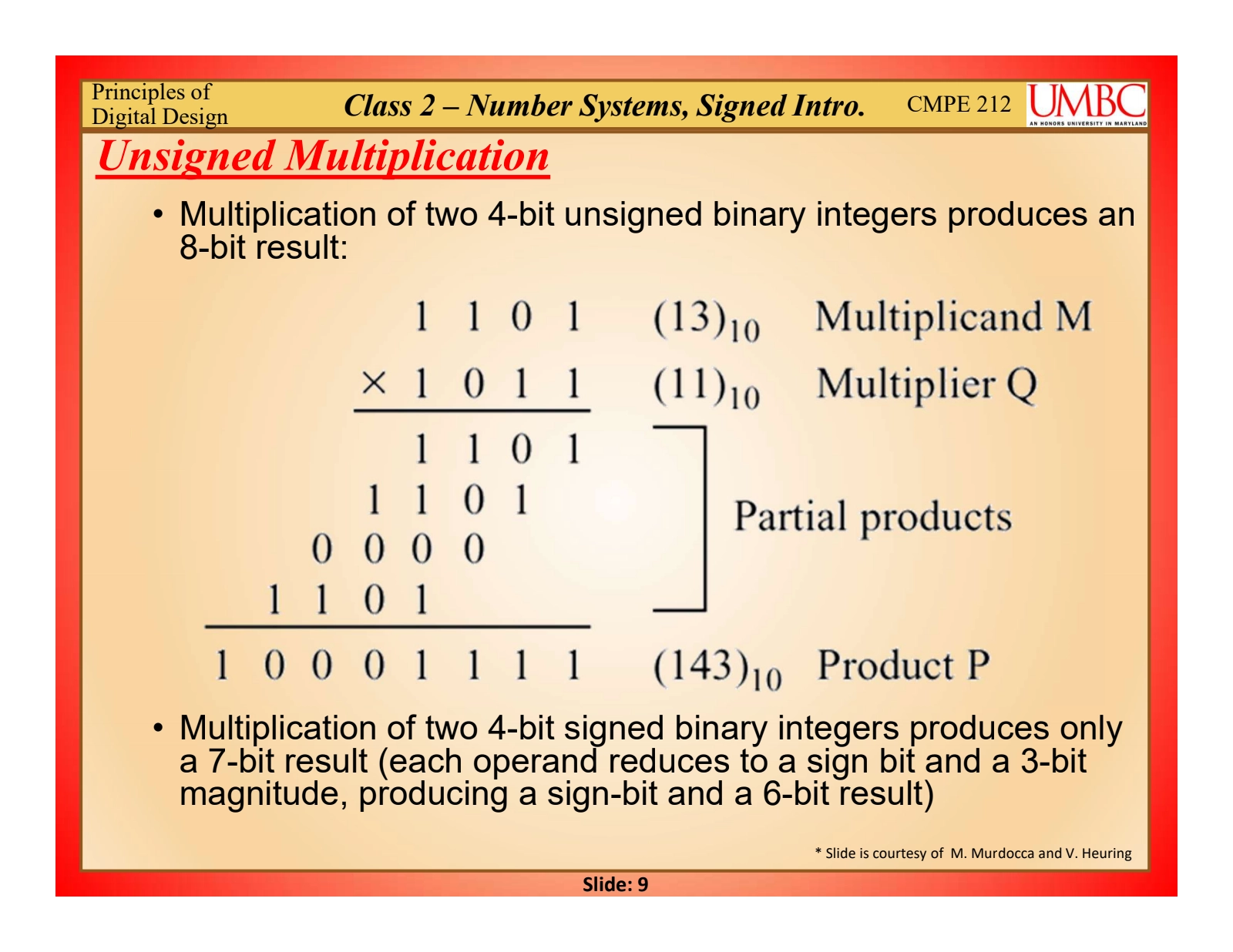

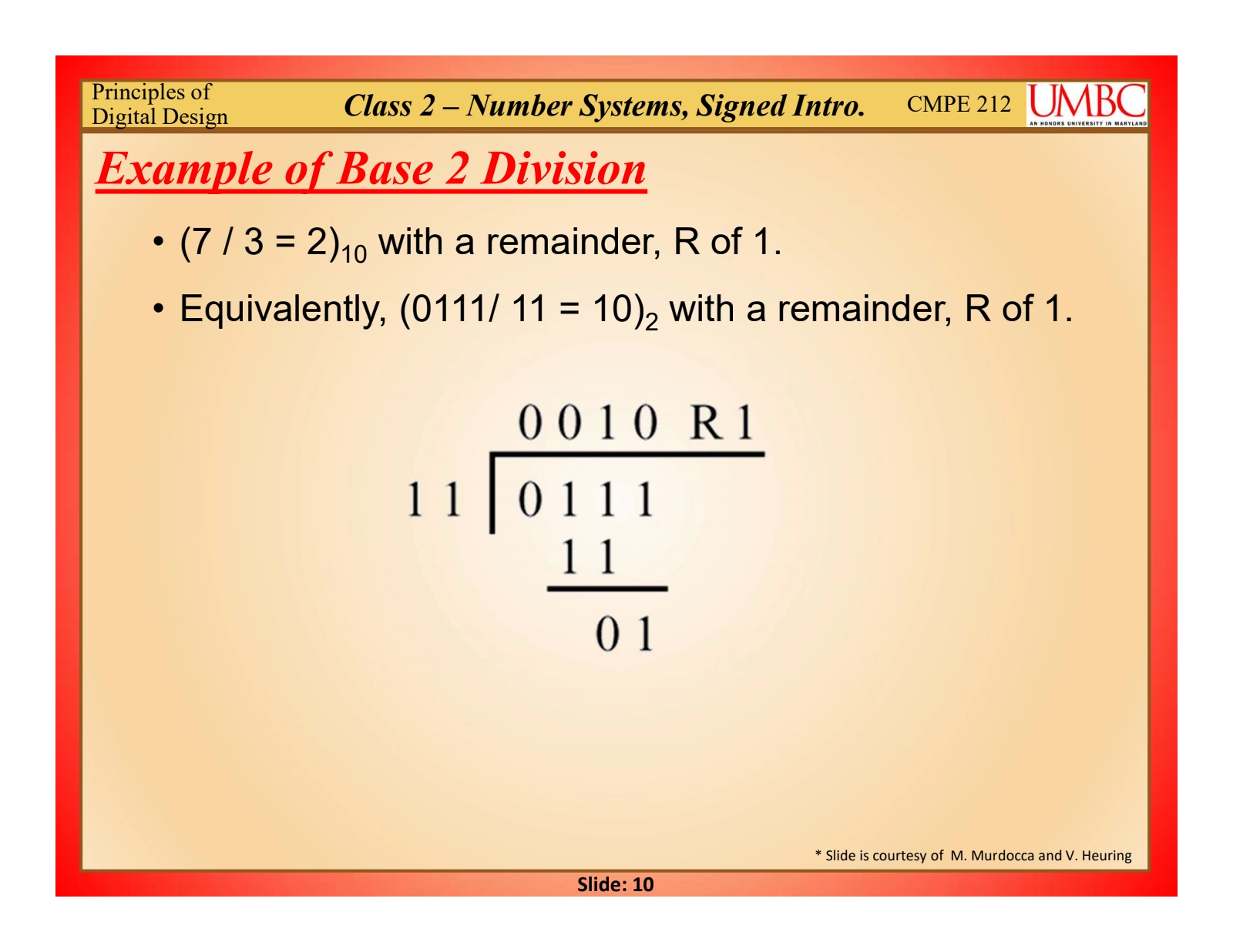

Class: 2, slide: 7-10 → Add, Sub, Mult & Divide Base 2

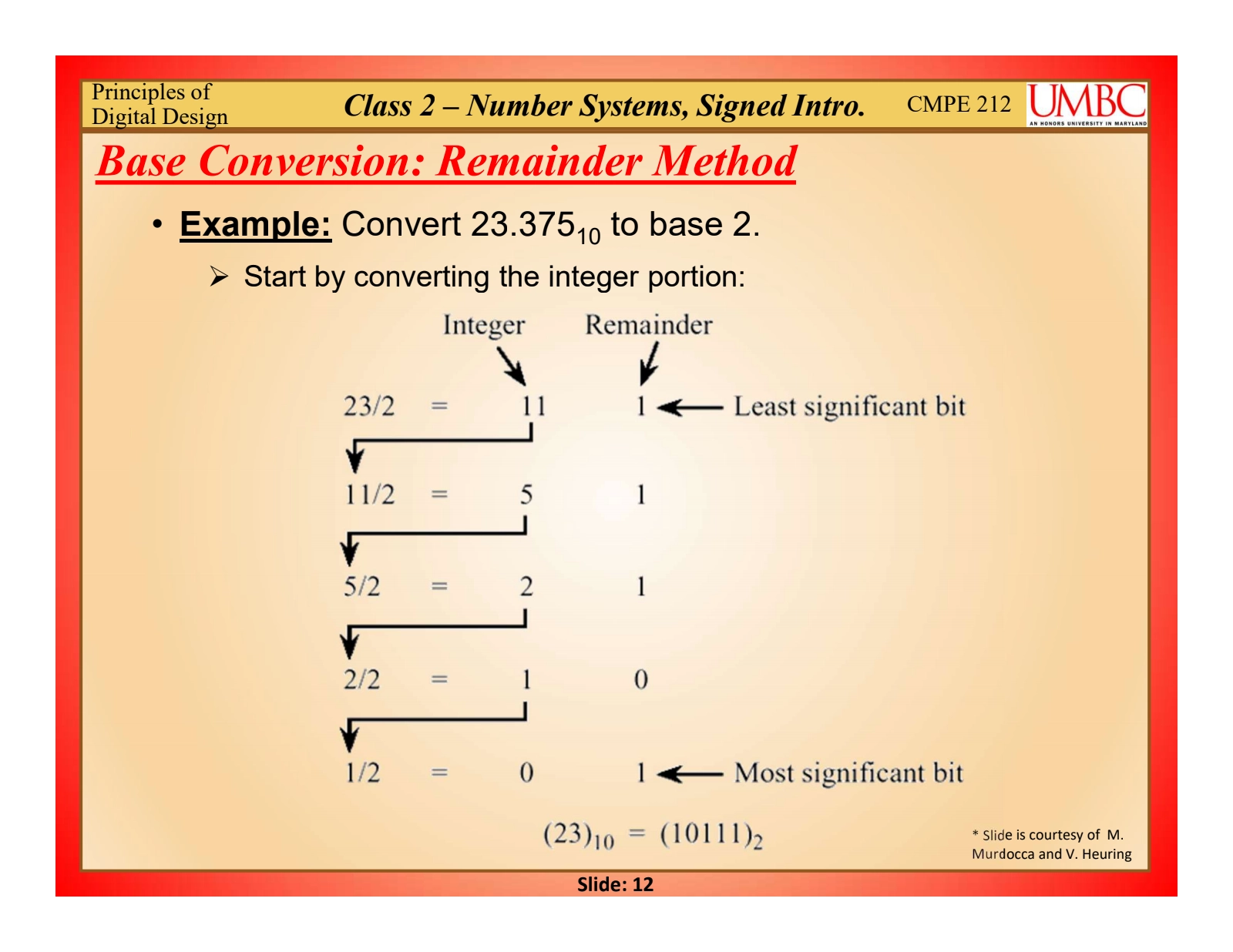

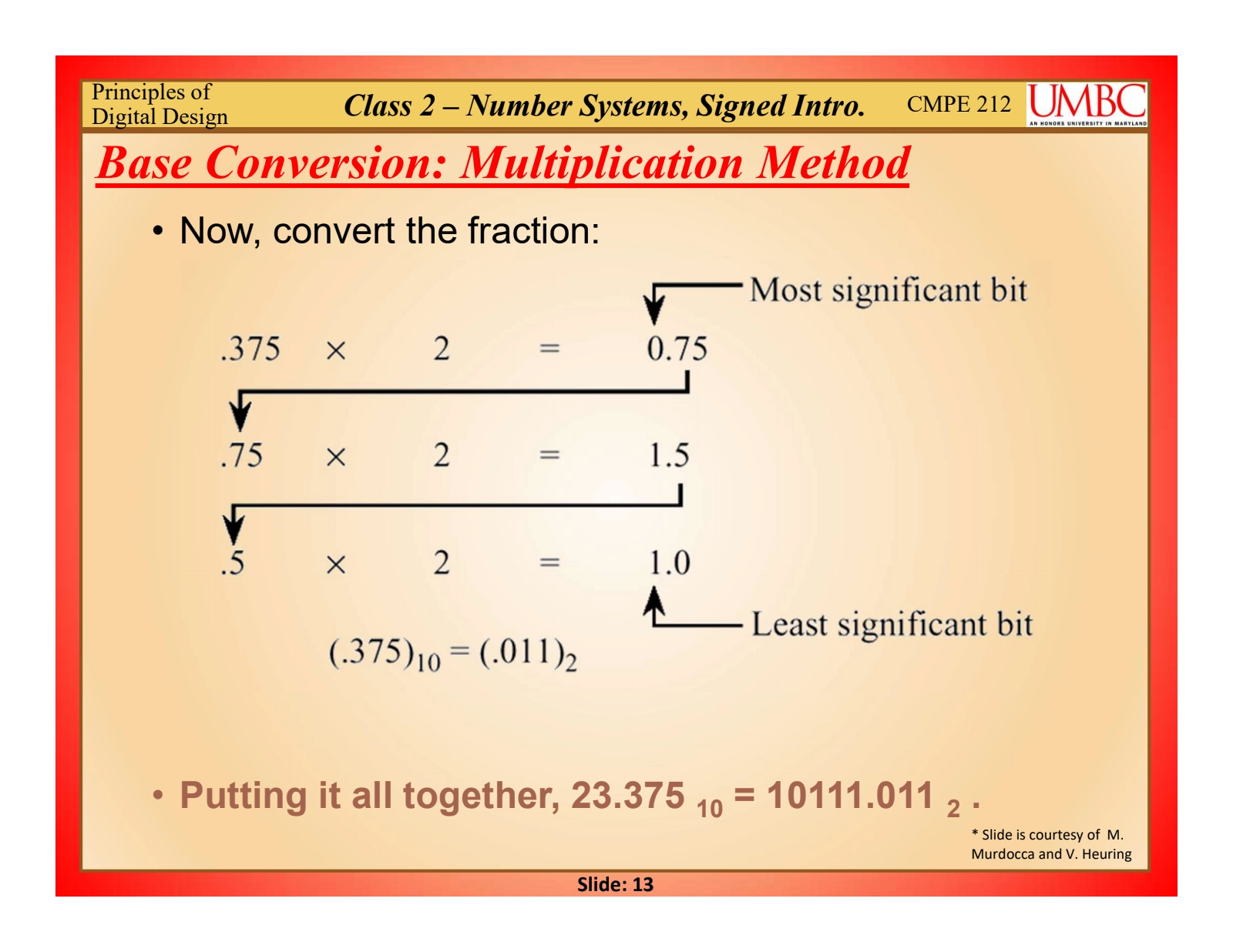

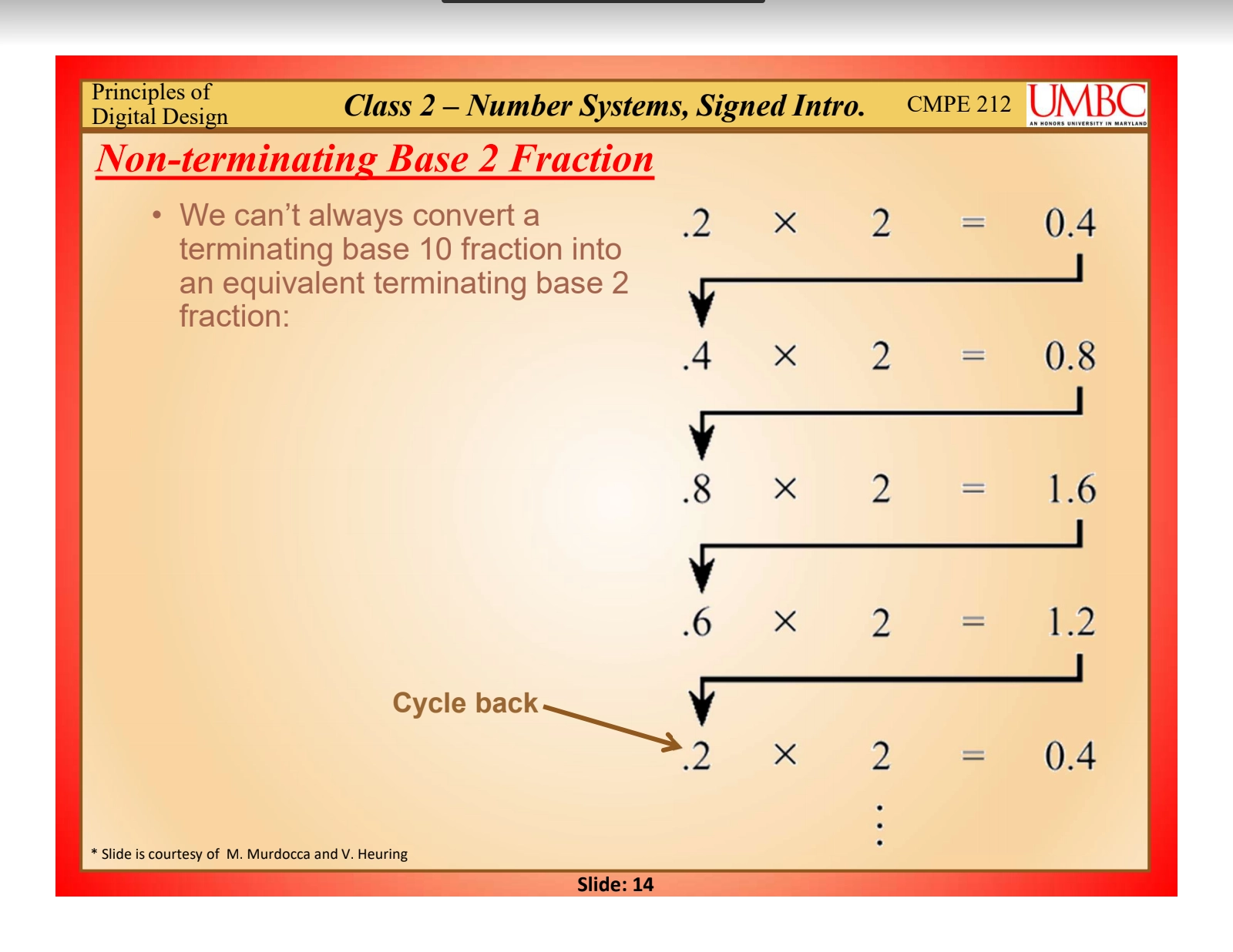

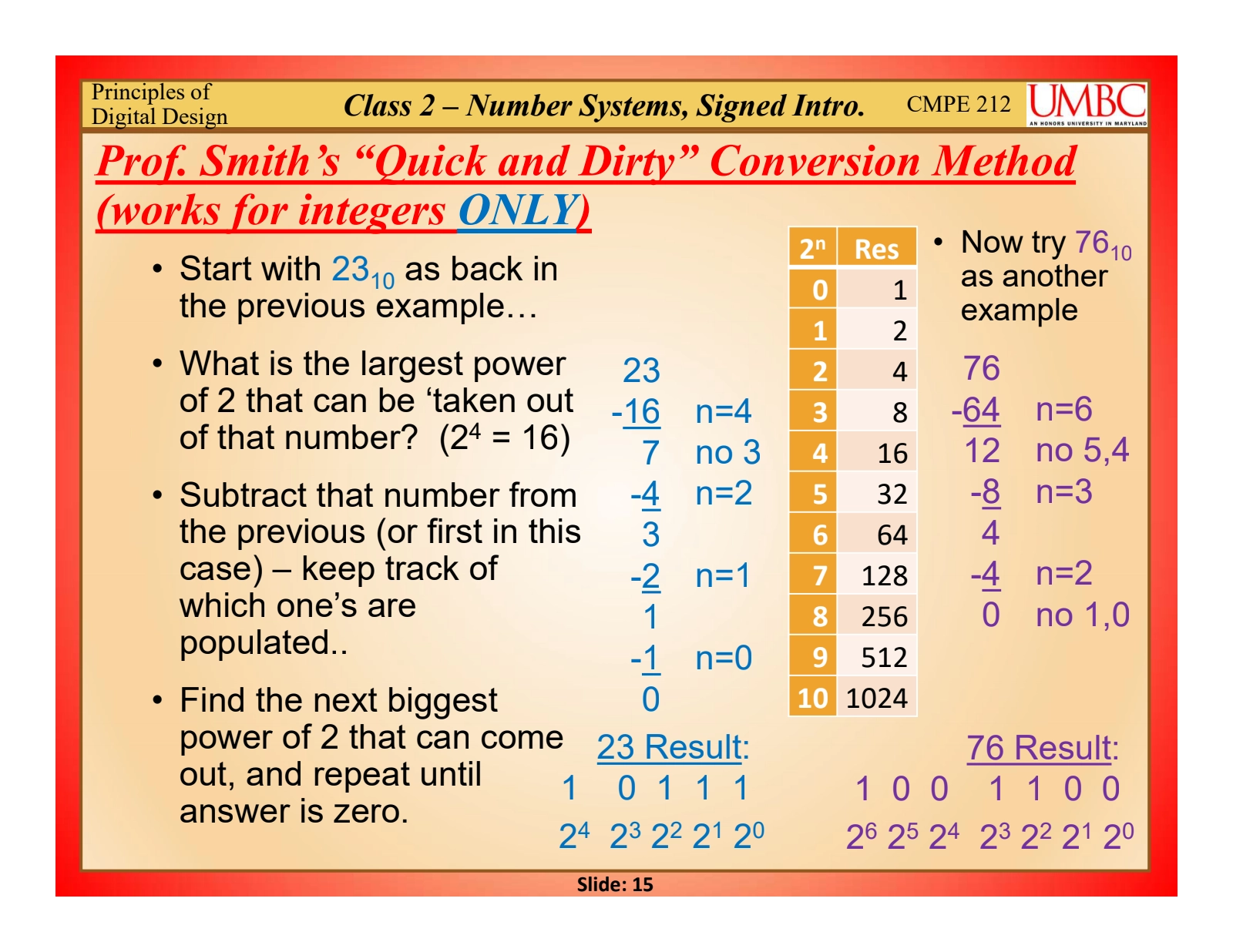

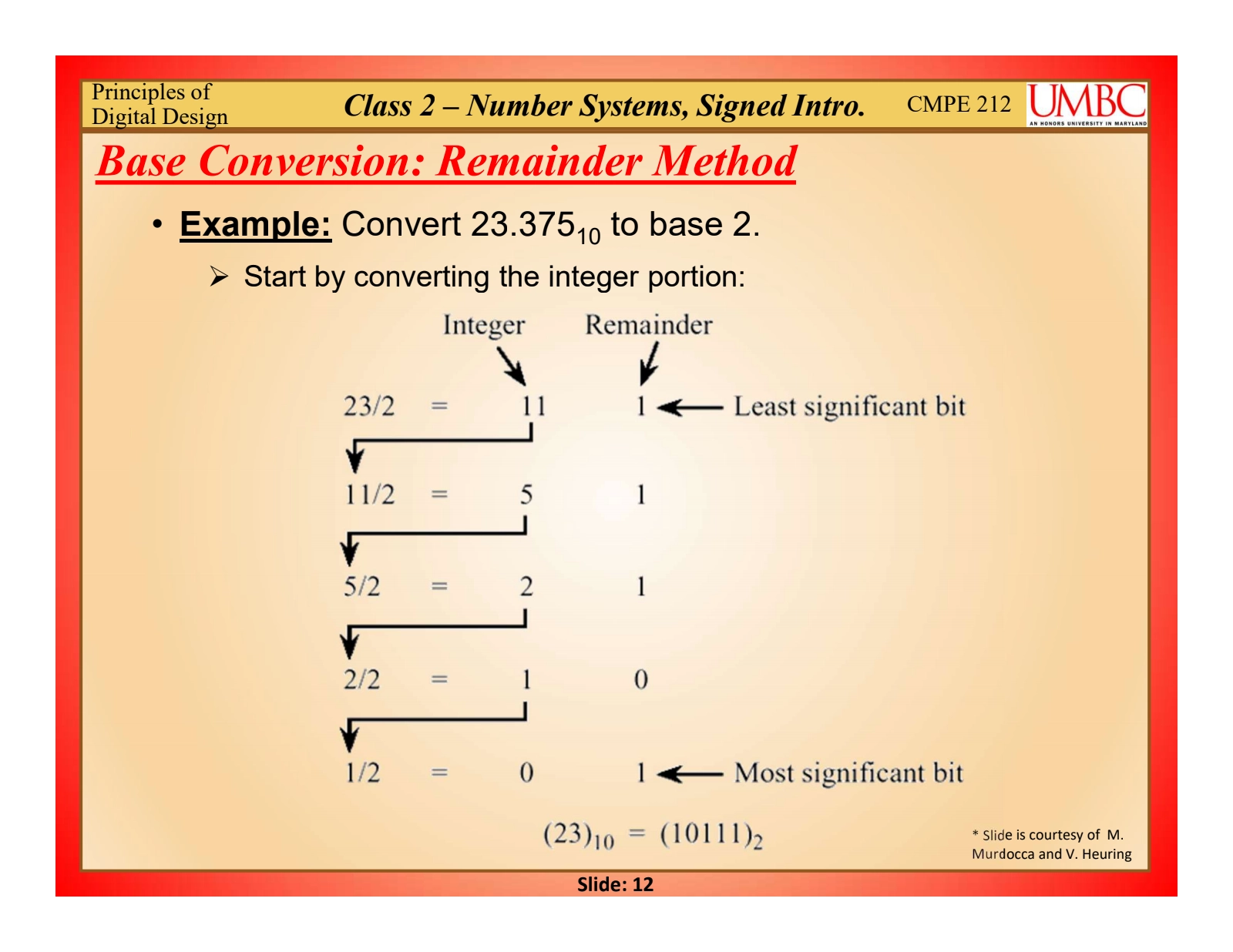

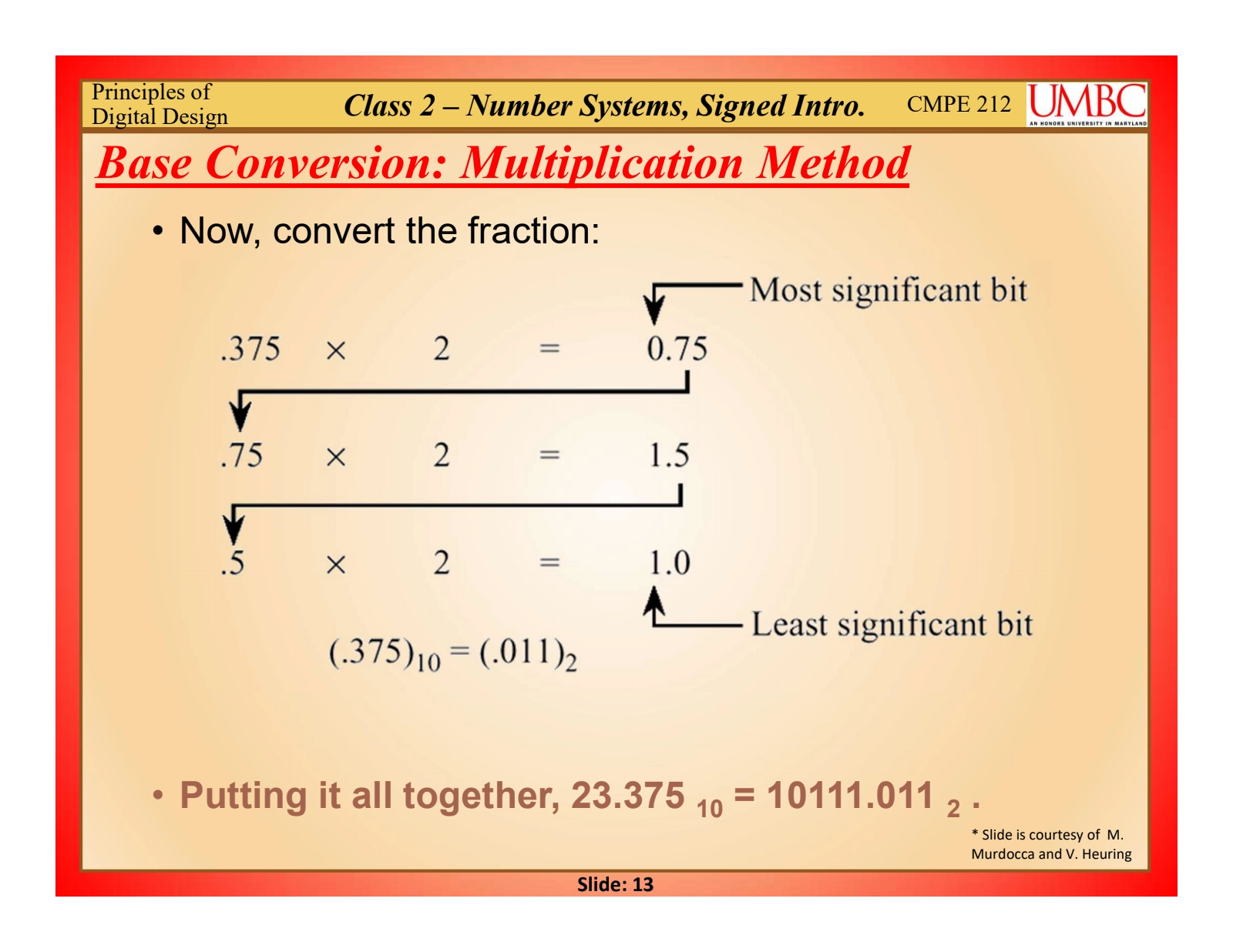

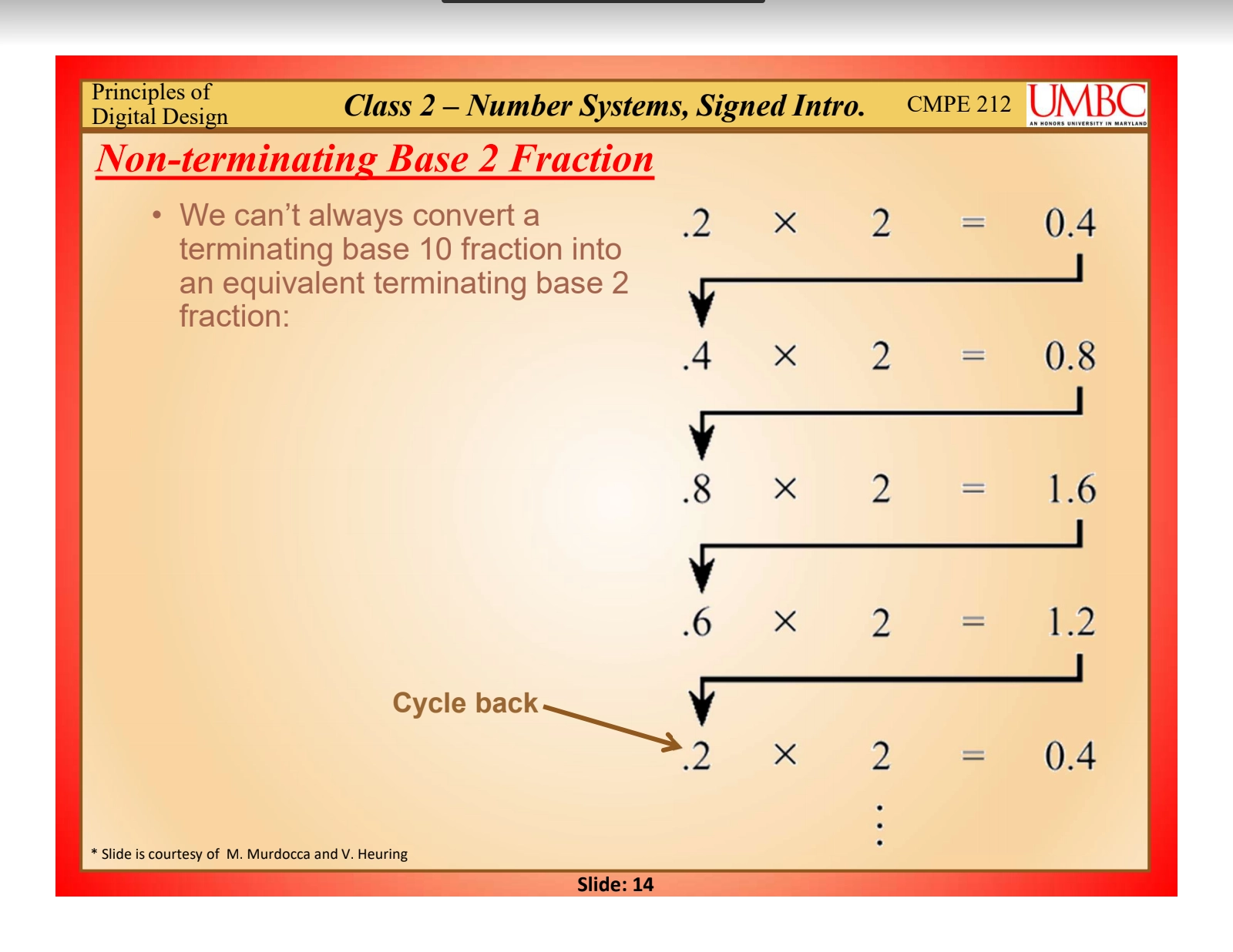

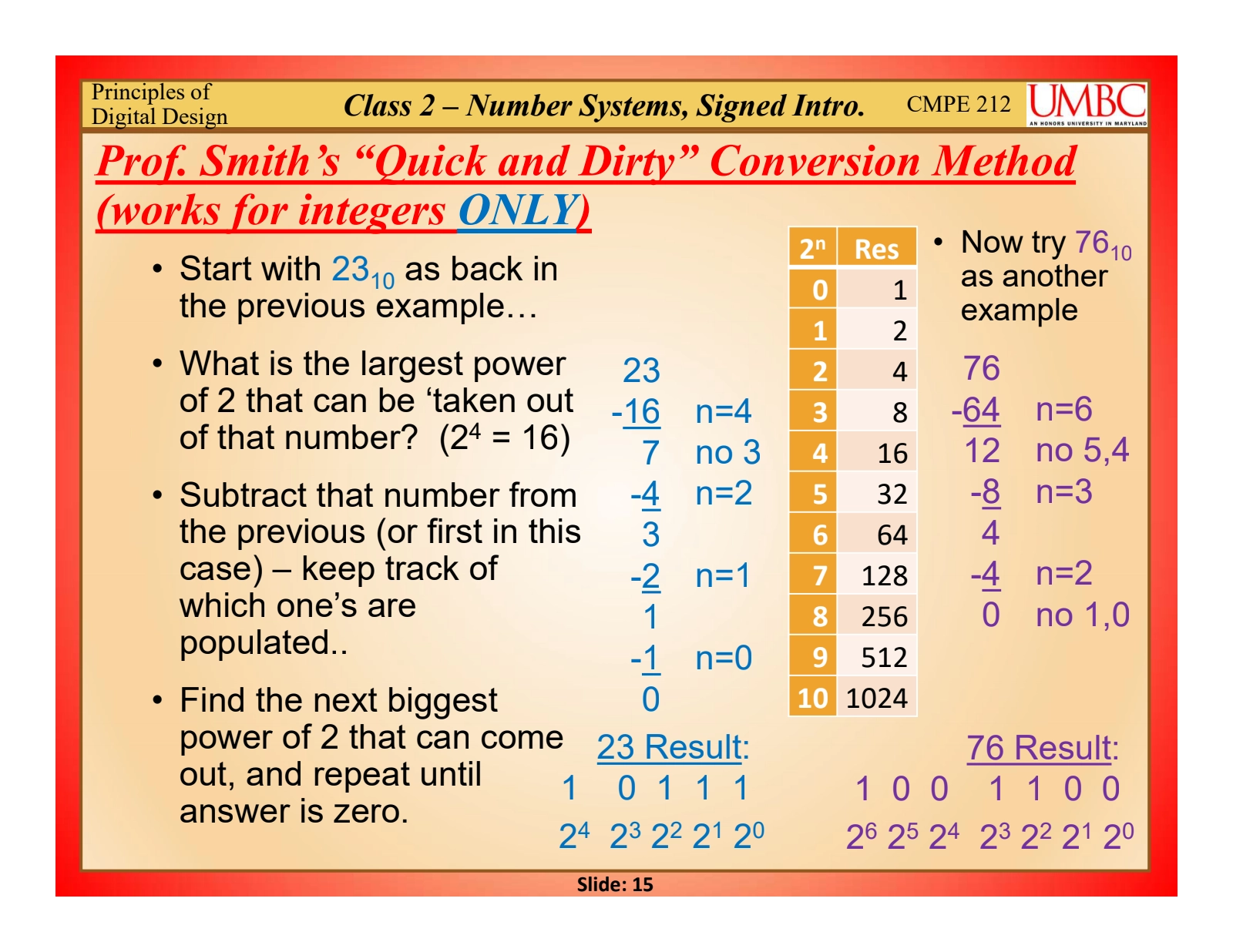

Class: 2, slide: 12-15 → Converting Base 10 to Base 2

Class: 2, slide: 17&18 → Converting hex to/from bin

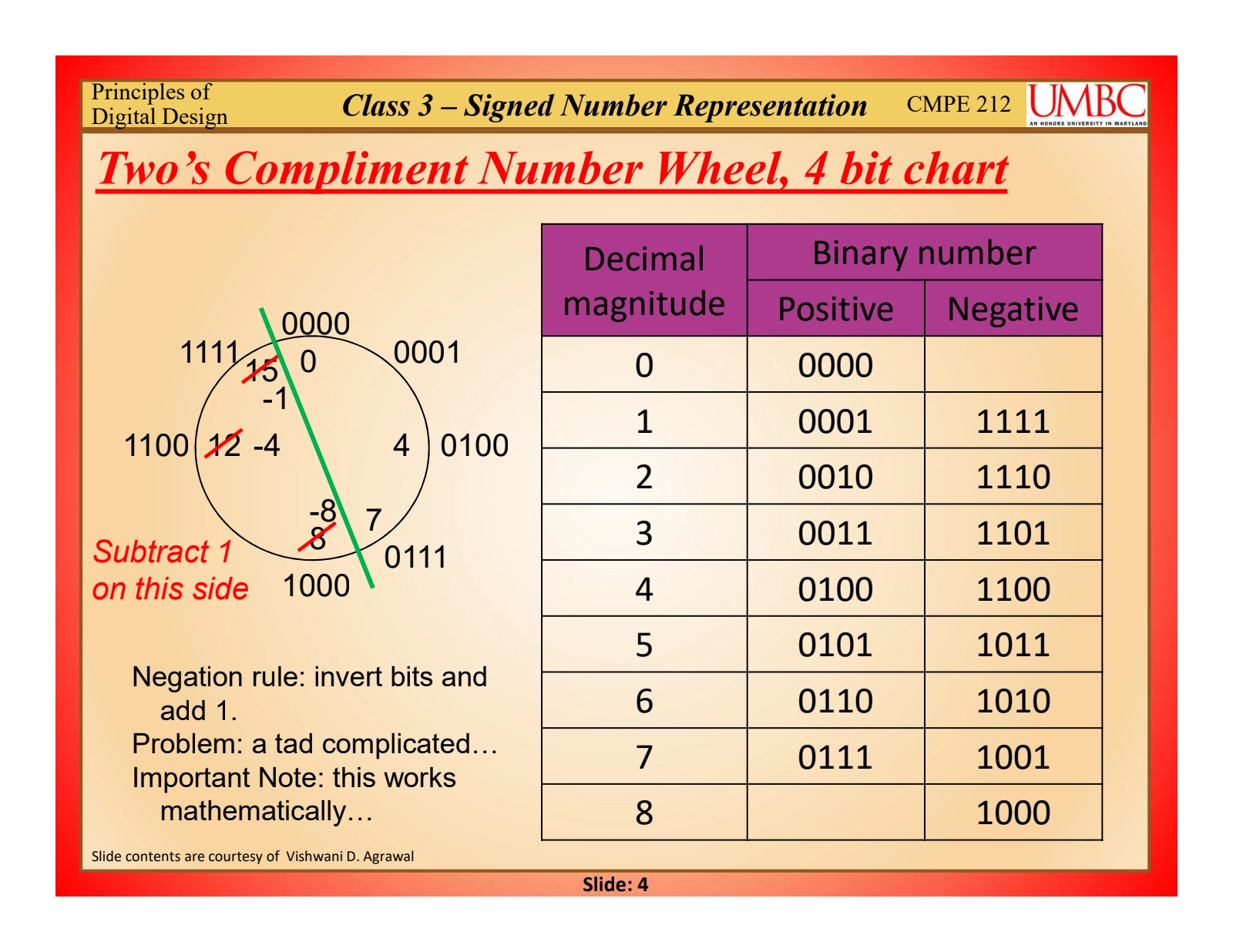

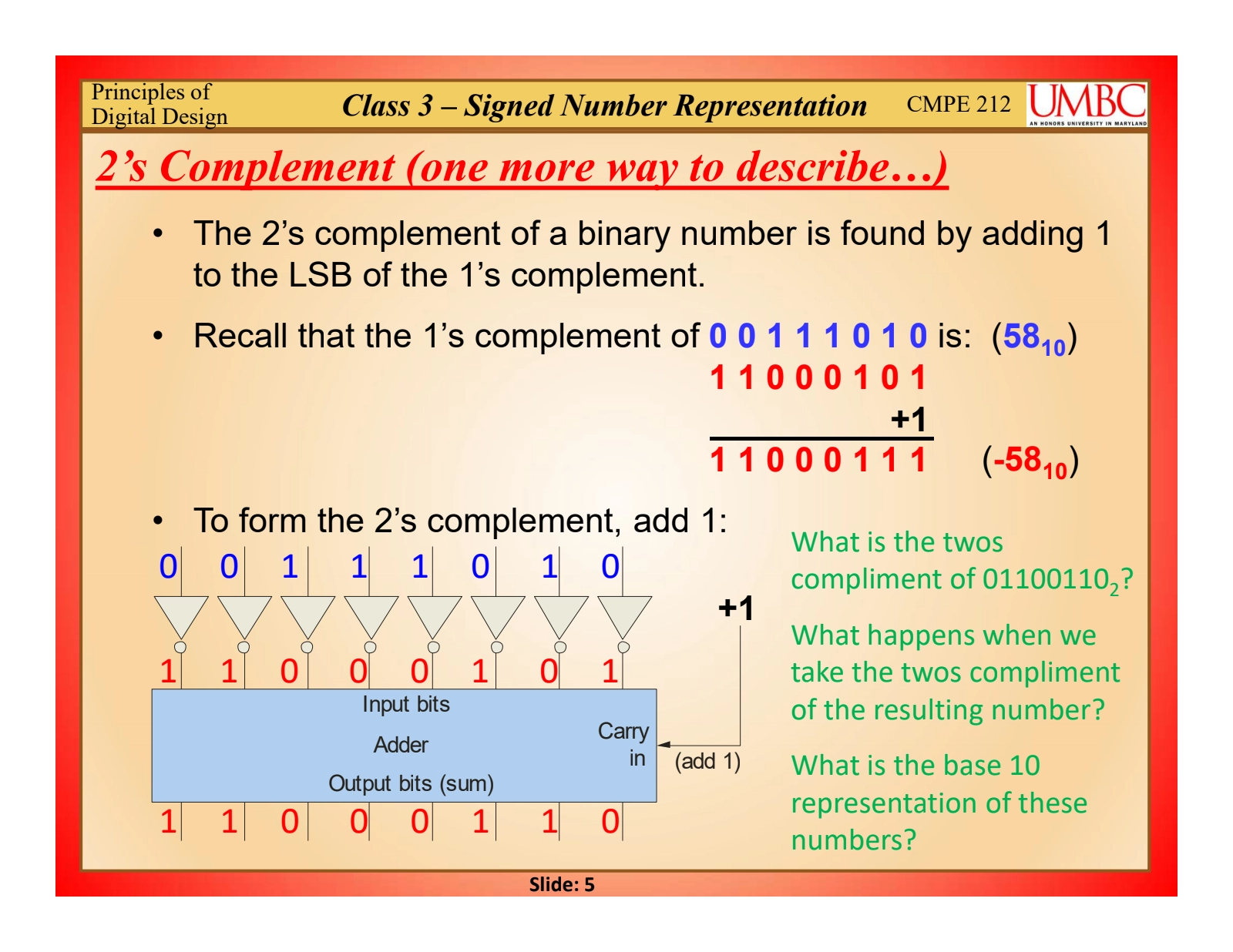

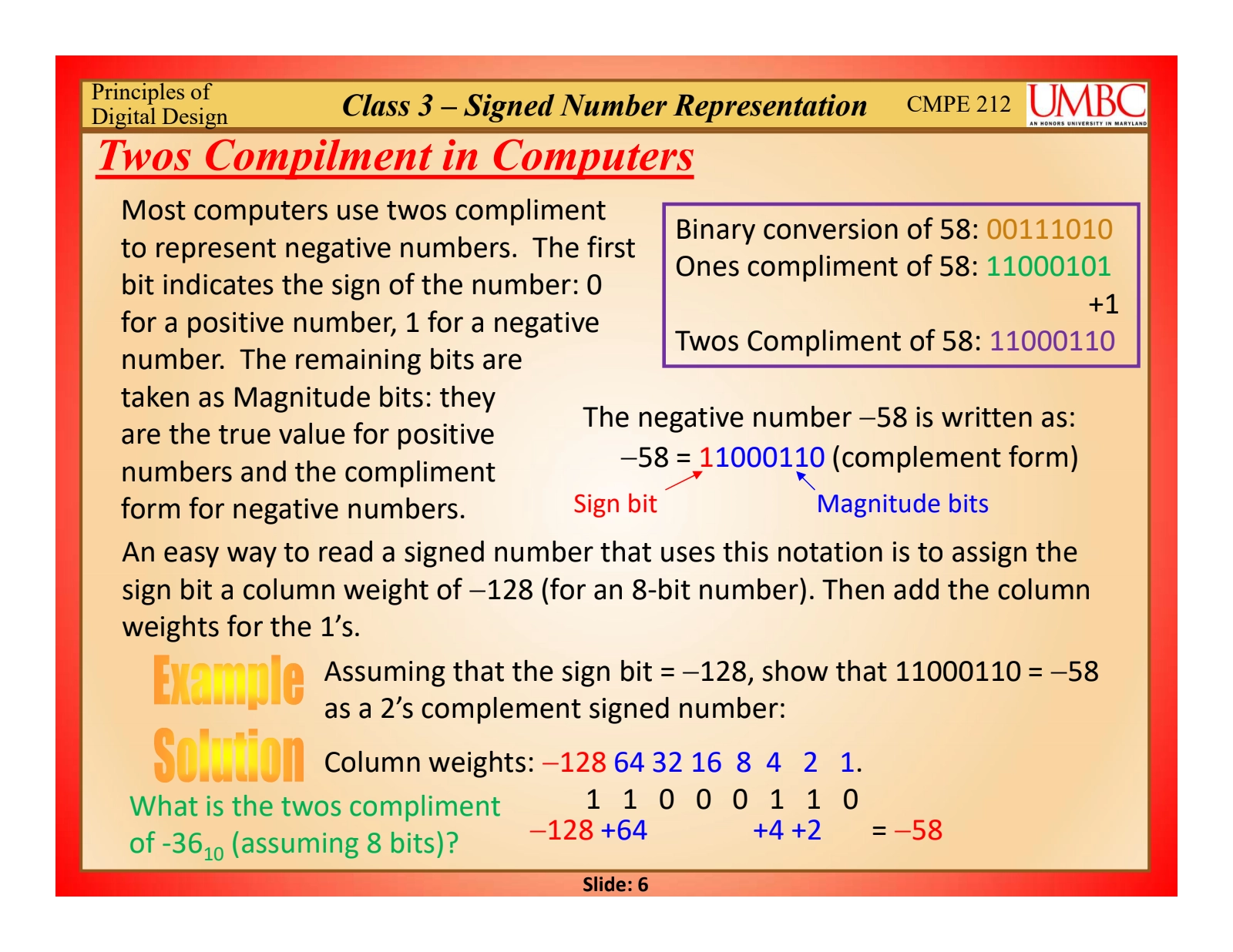

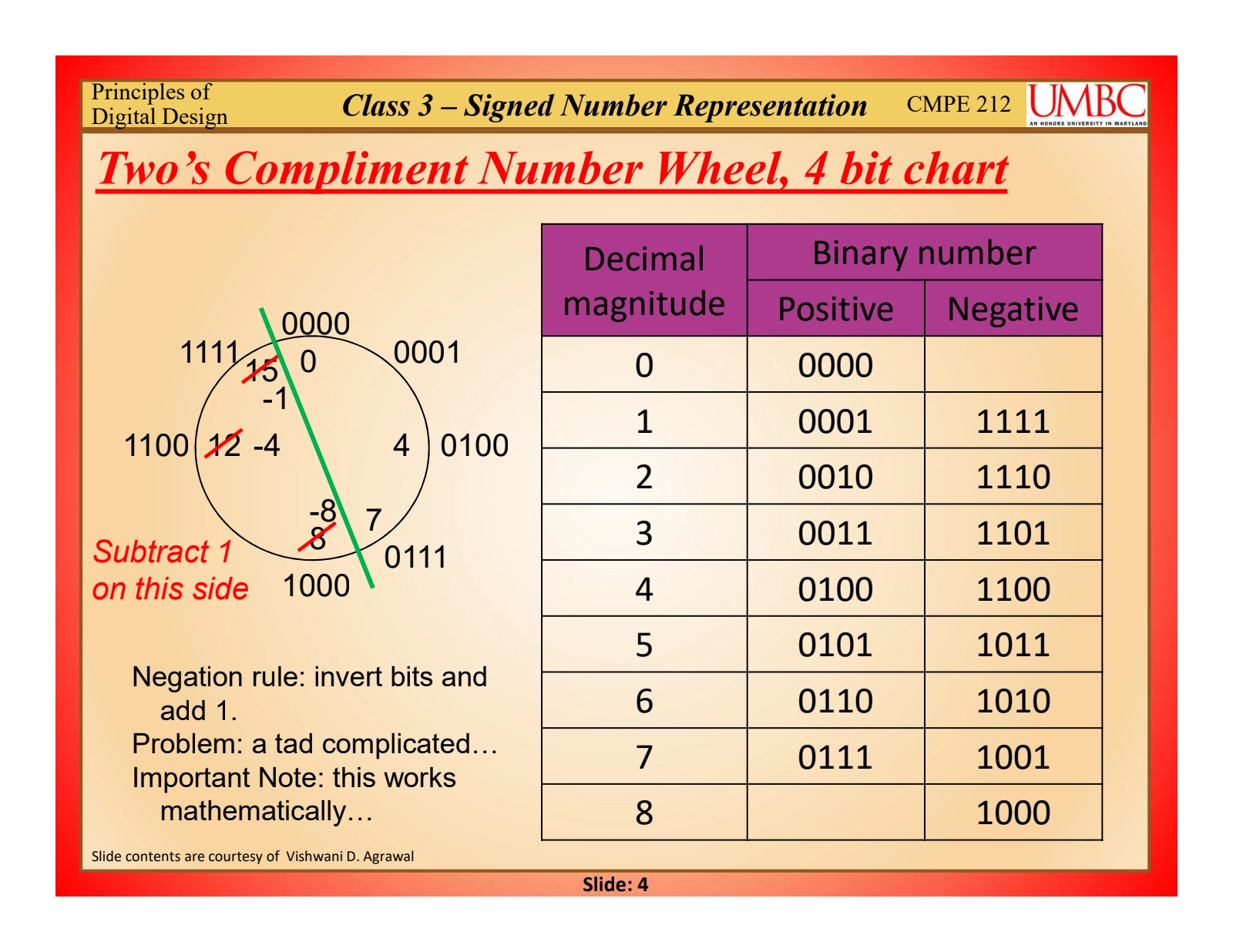

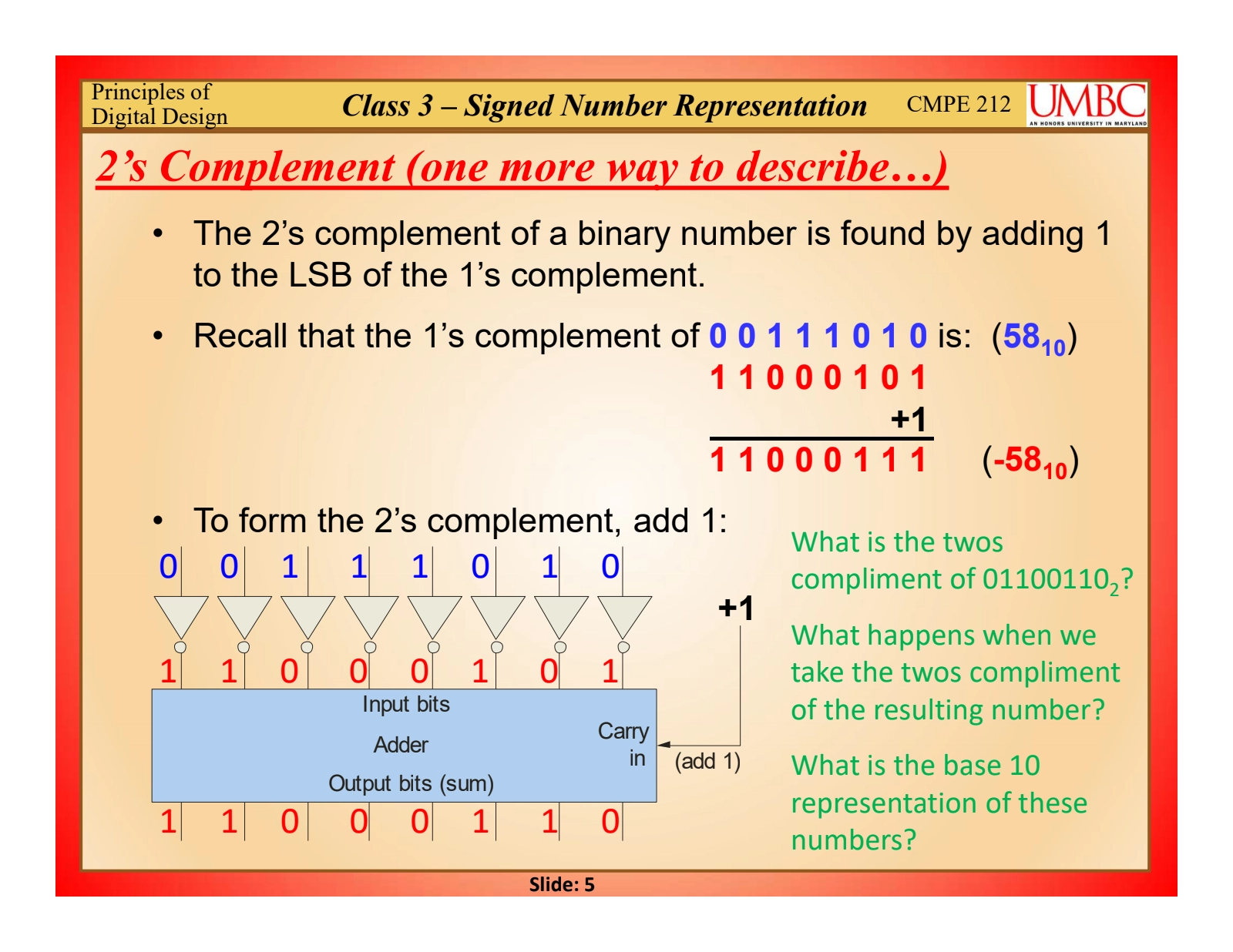

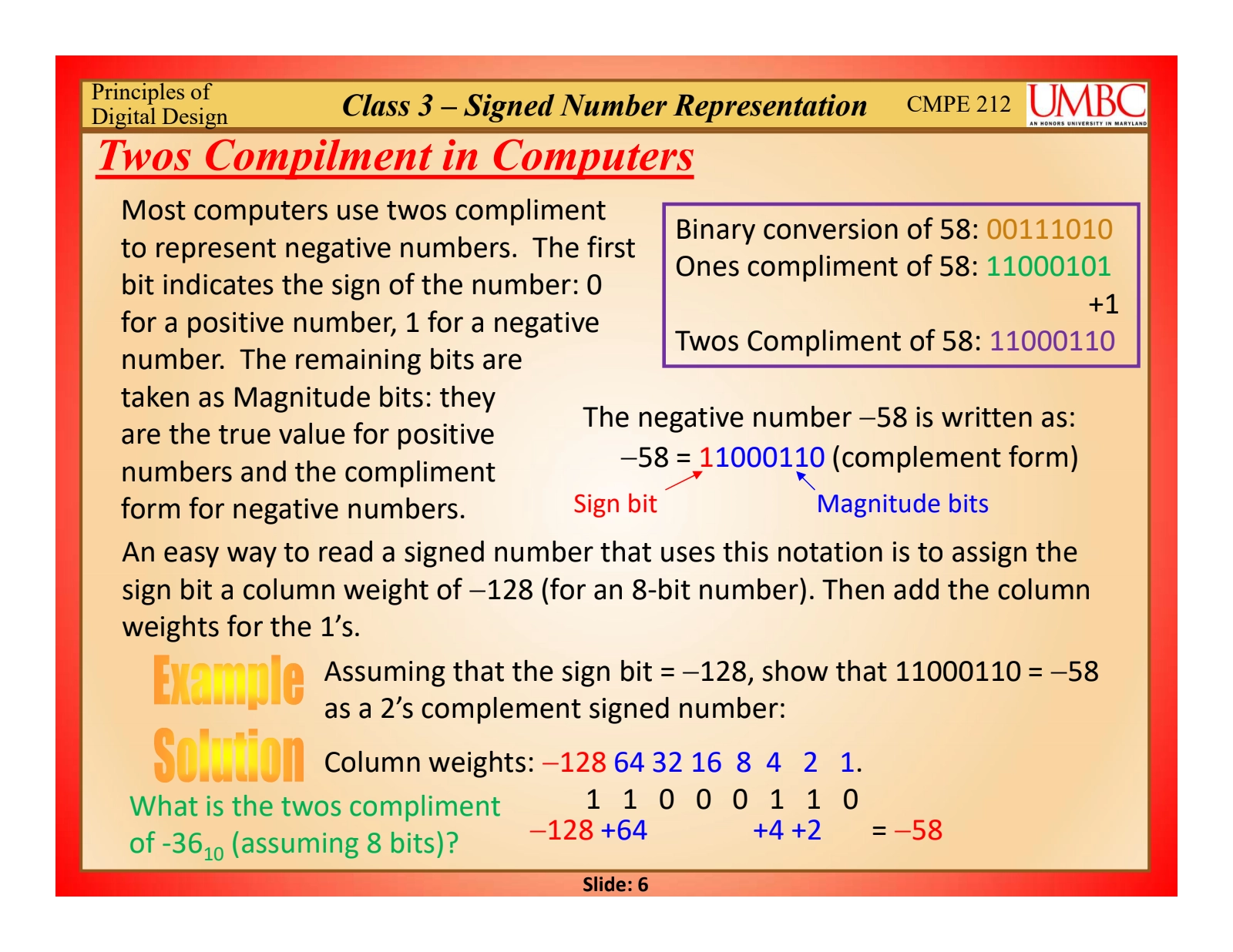

Class: 3, slide: 4-6 → Convert Dec to/from Two's Compliment

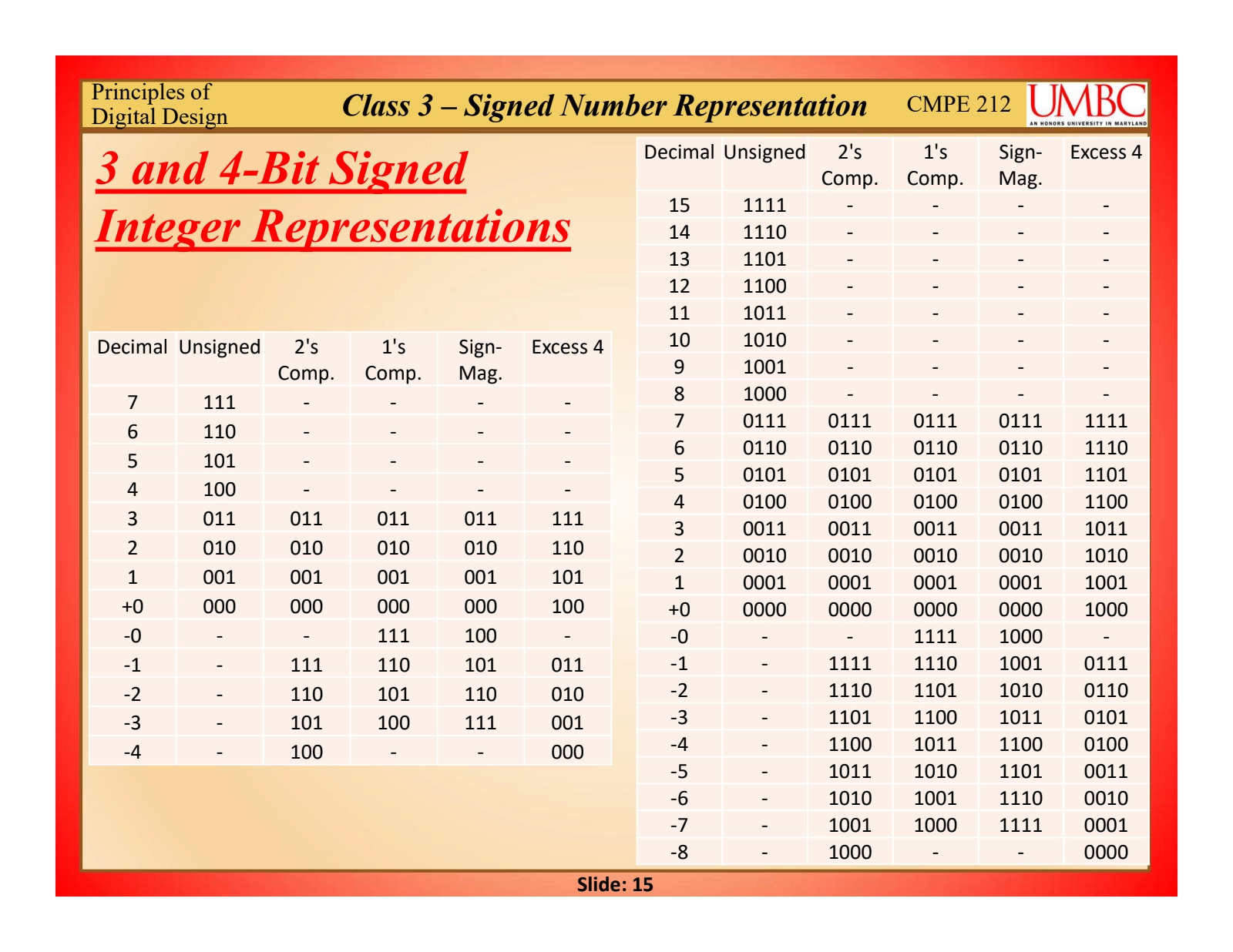

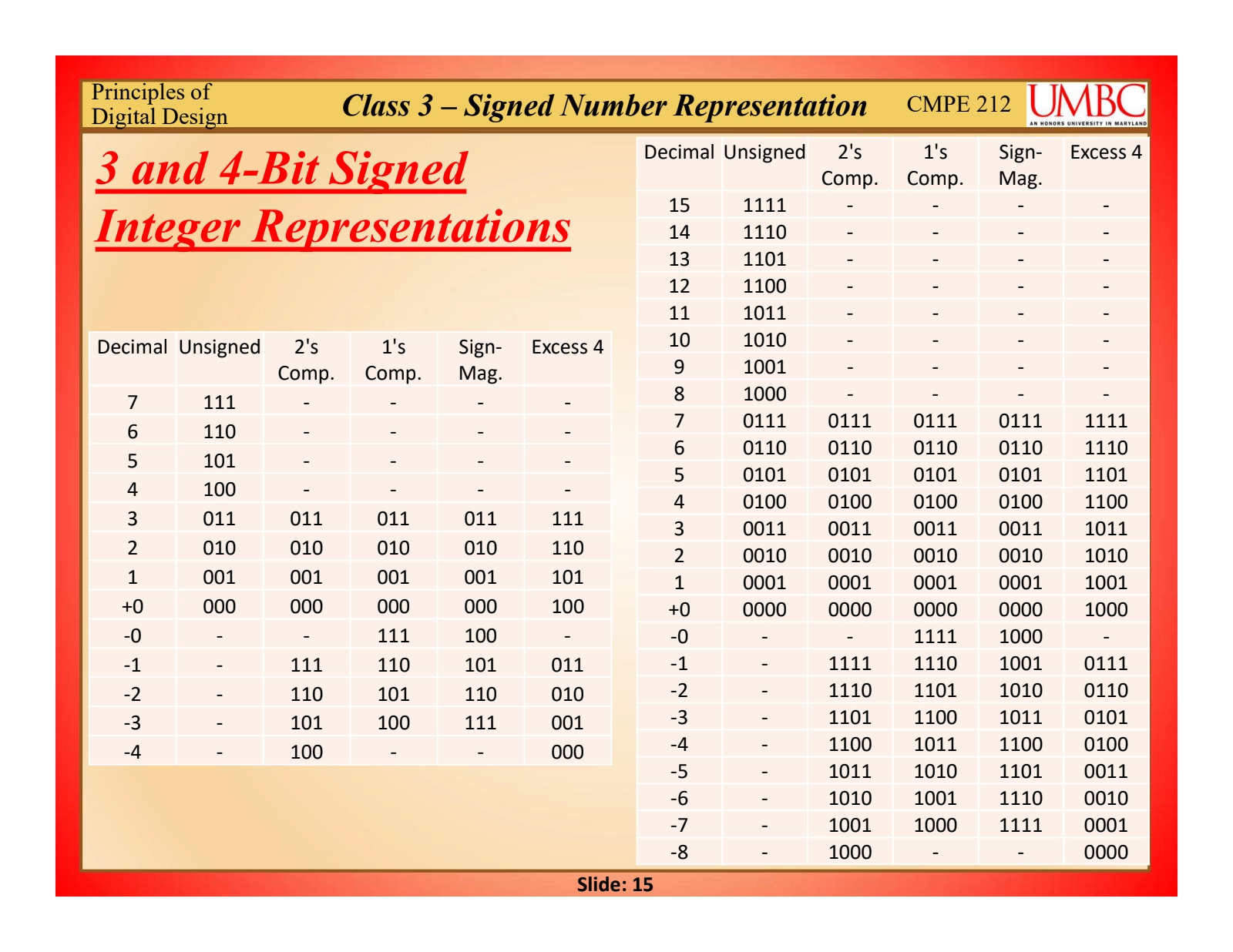

Class: 3, slide: 15 → Map from dec to other signed representations

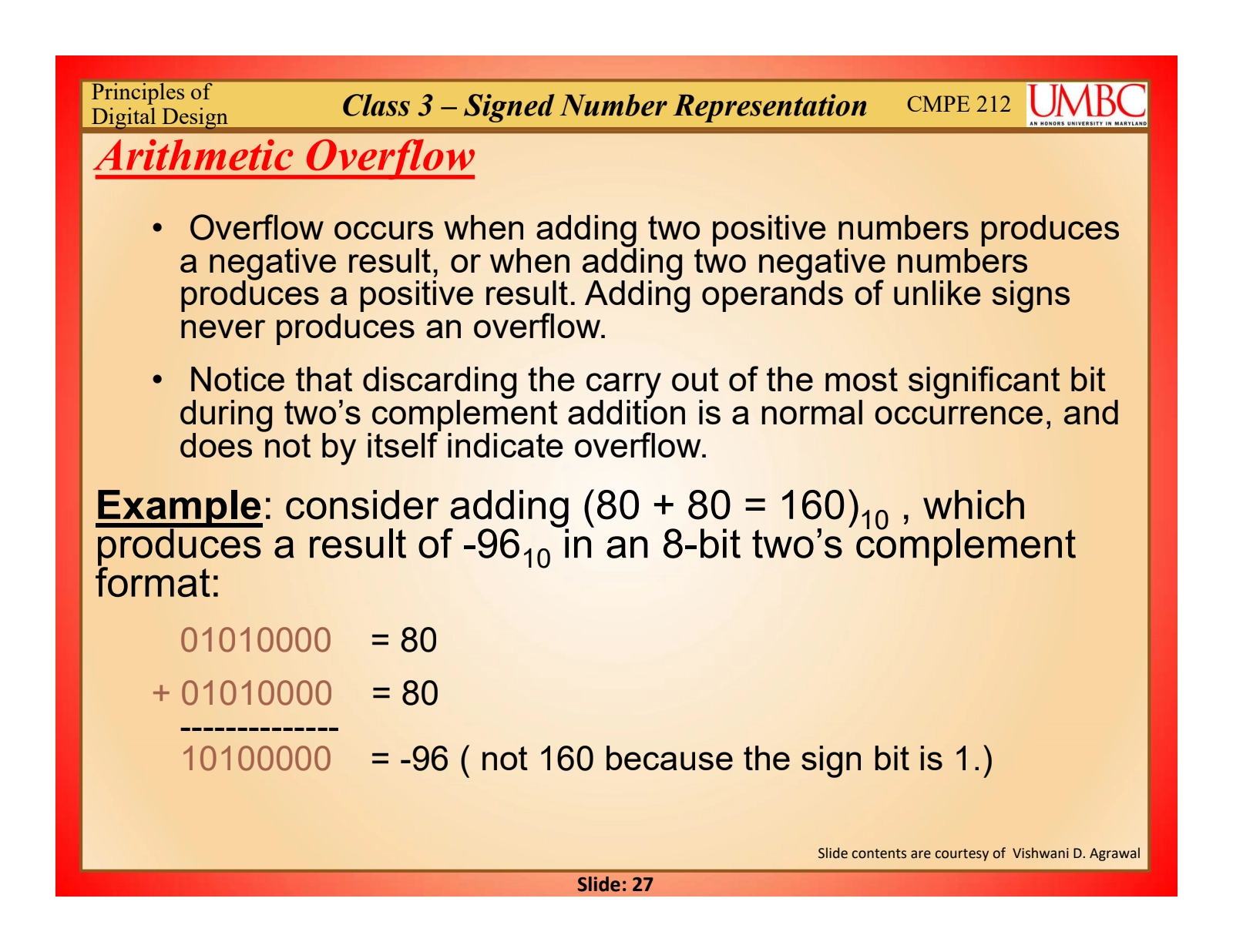

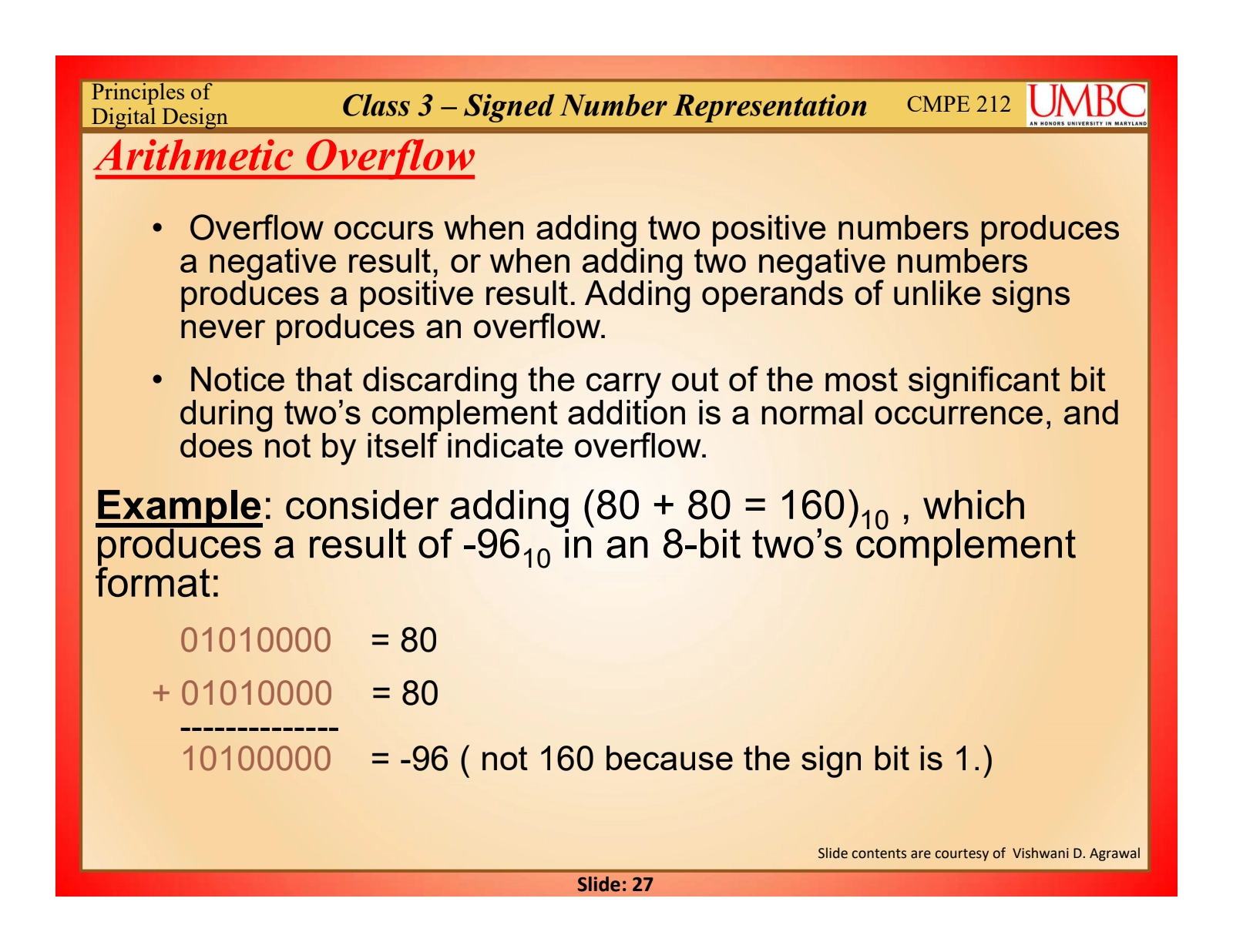

Class: 3, slide: 27 → Arithmetic Overflow

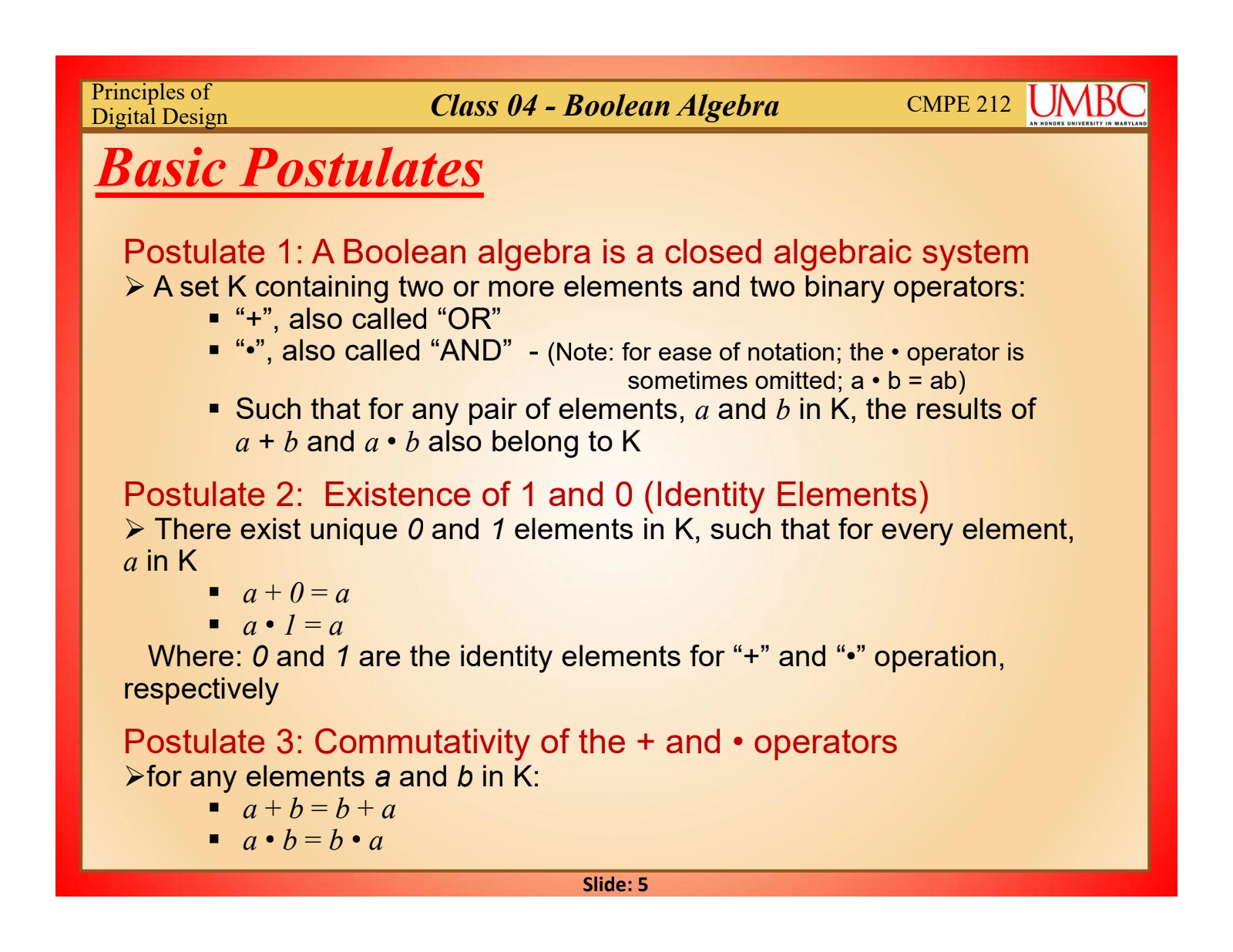

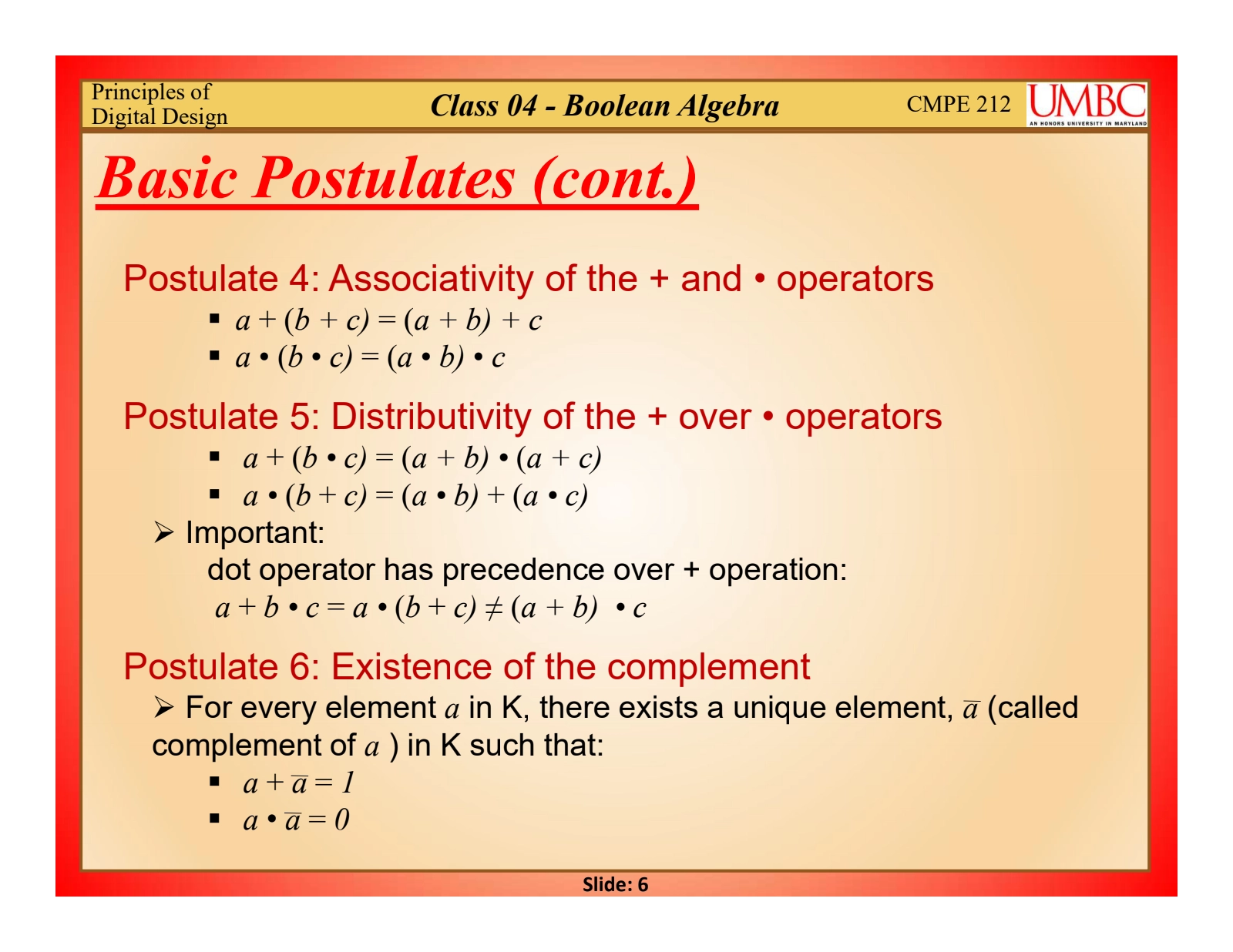

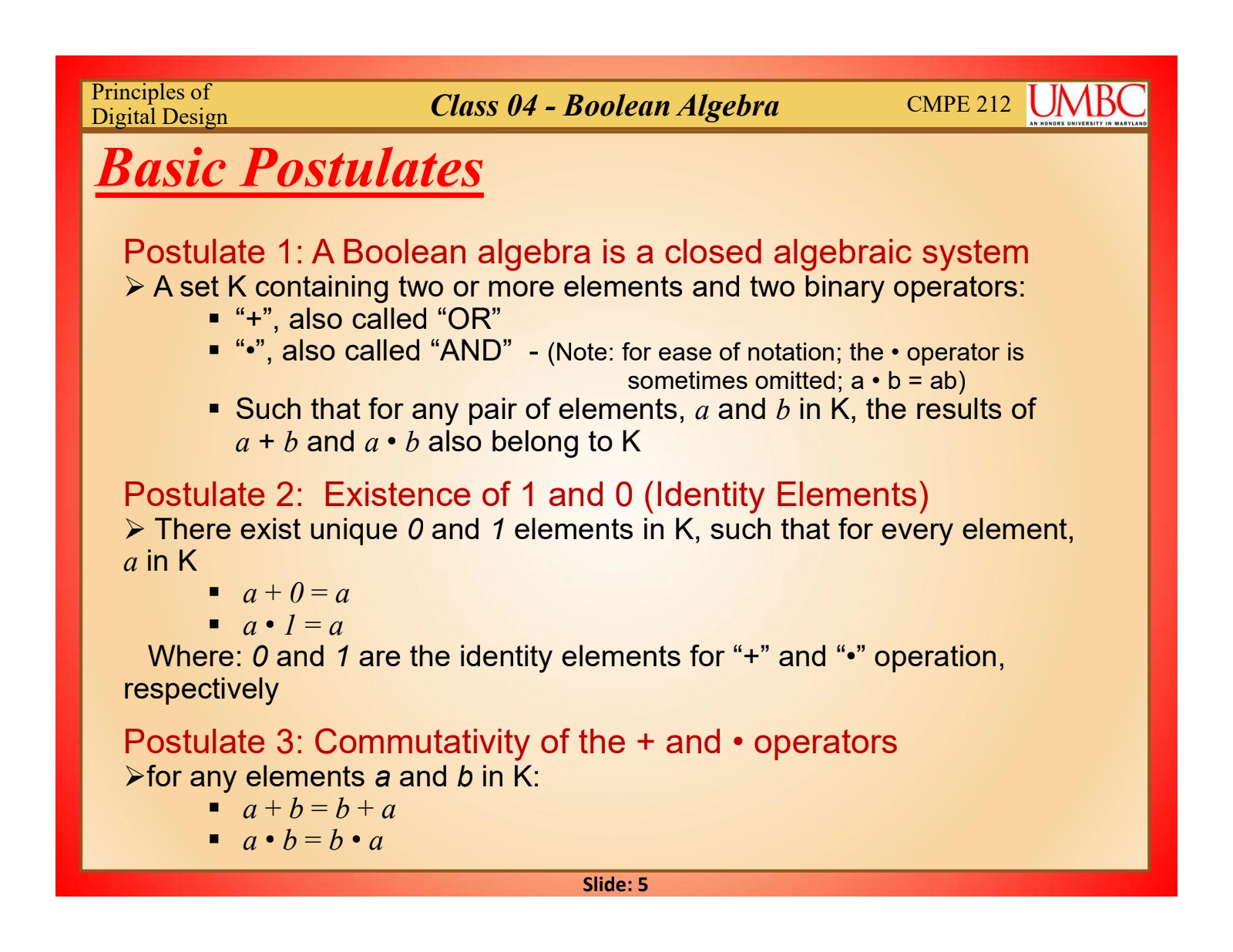

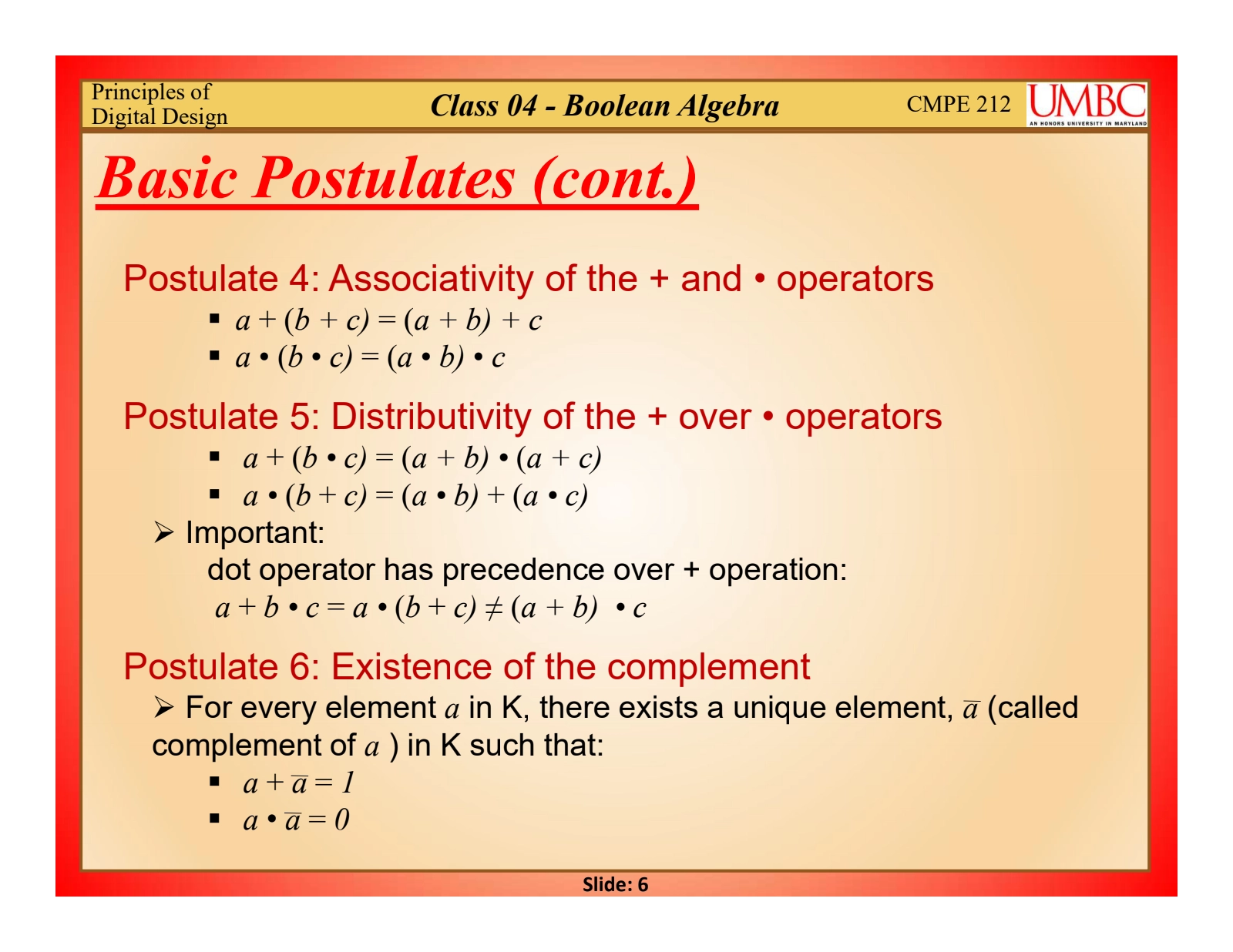

Class: 4, slide: 5-6 → Basic Boolean Postulates

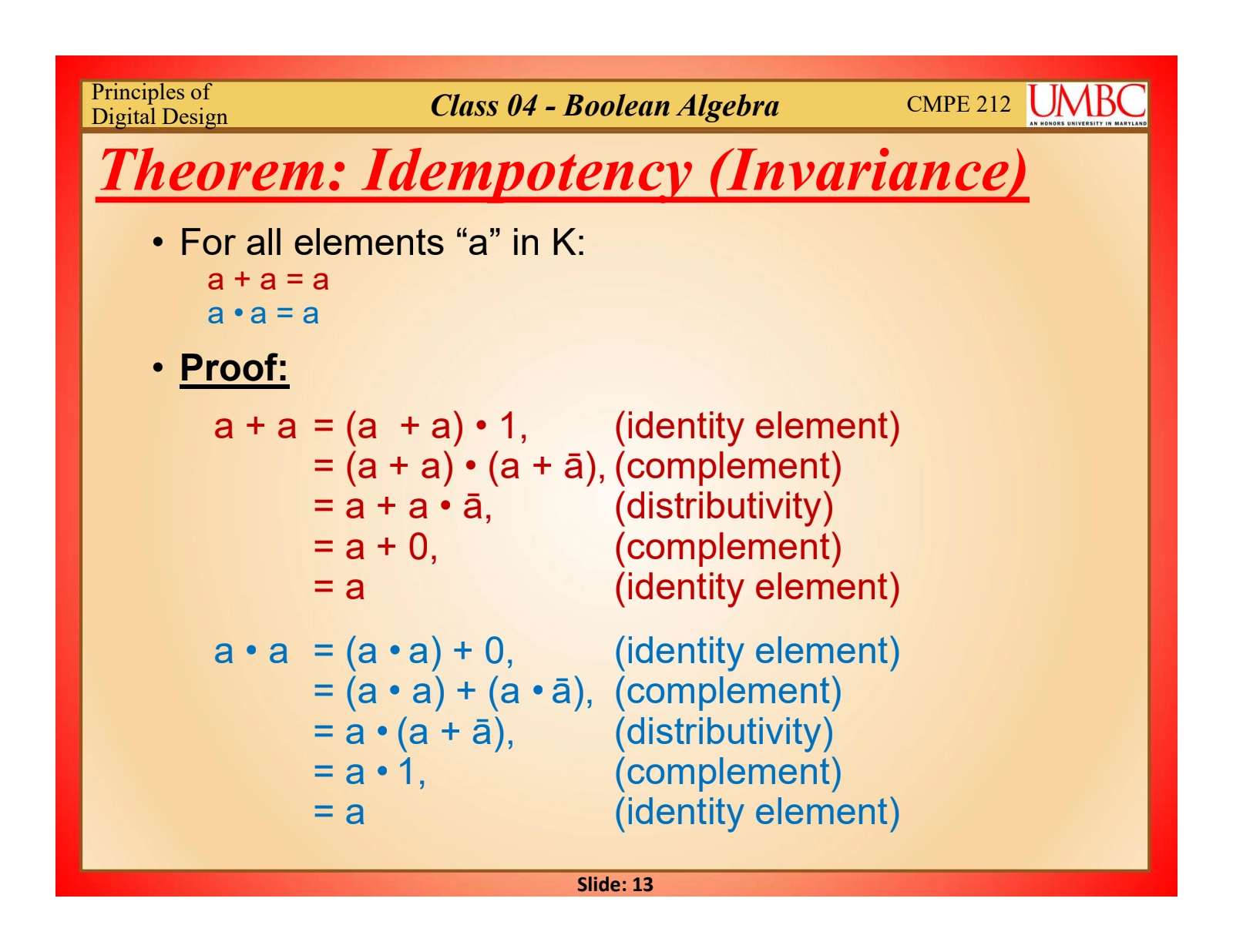

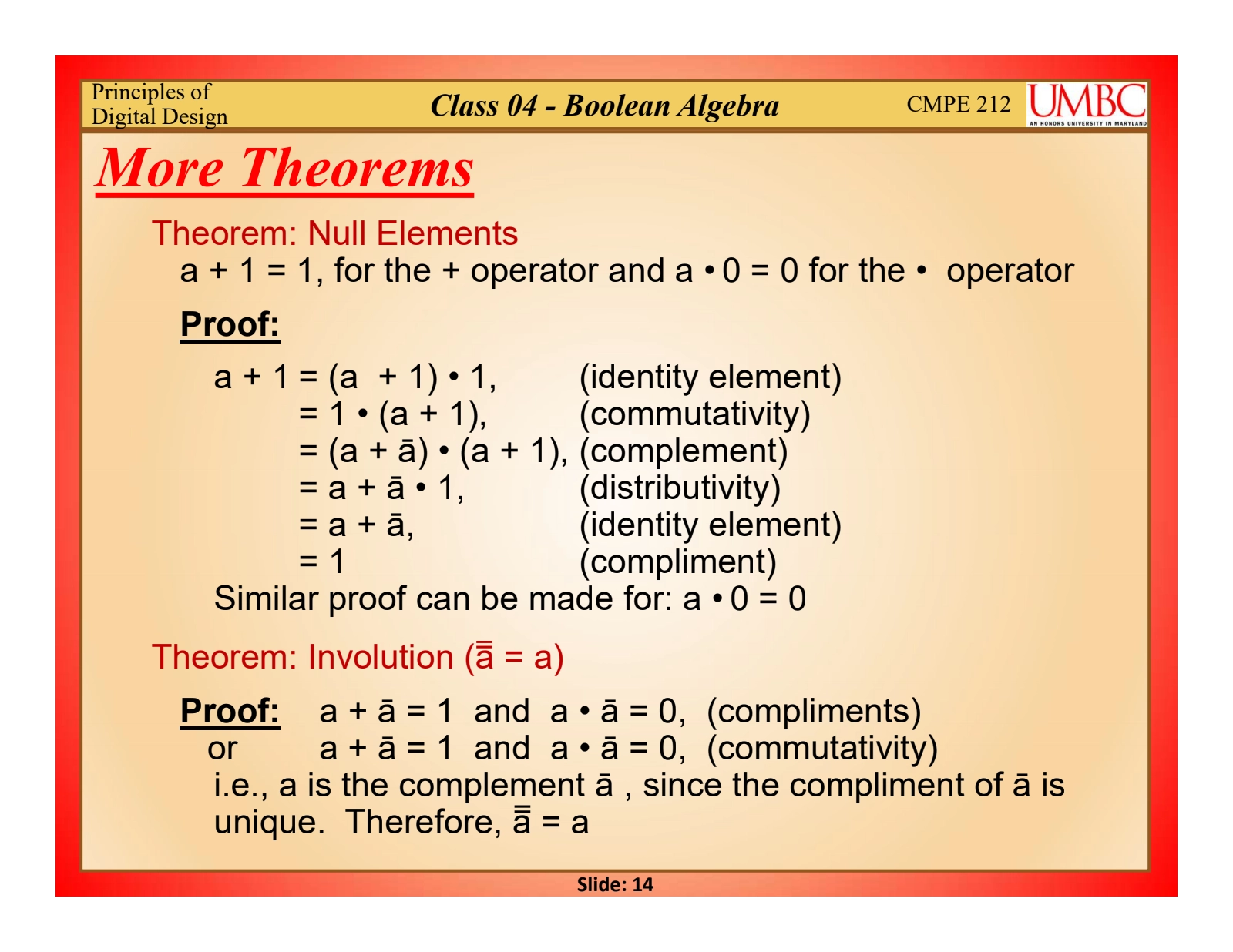

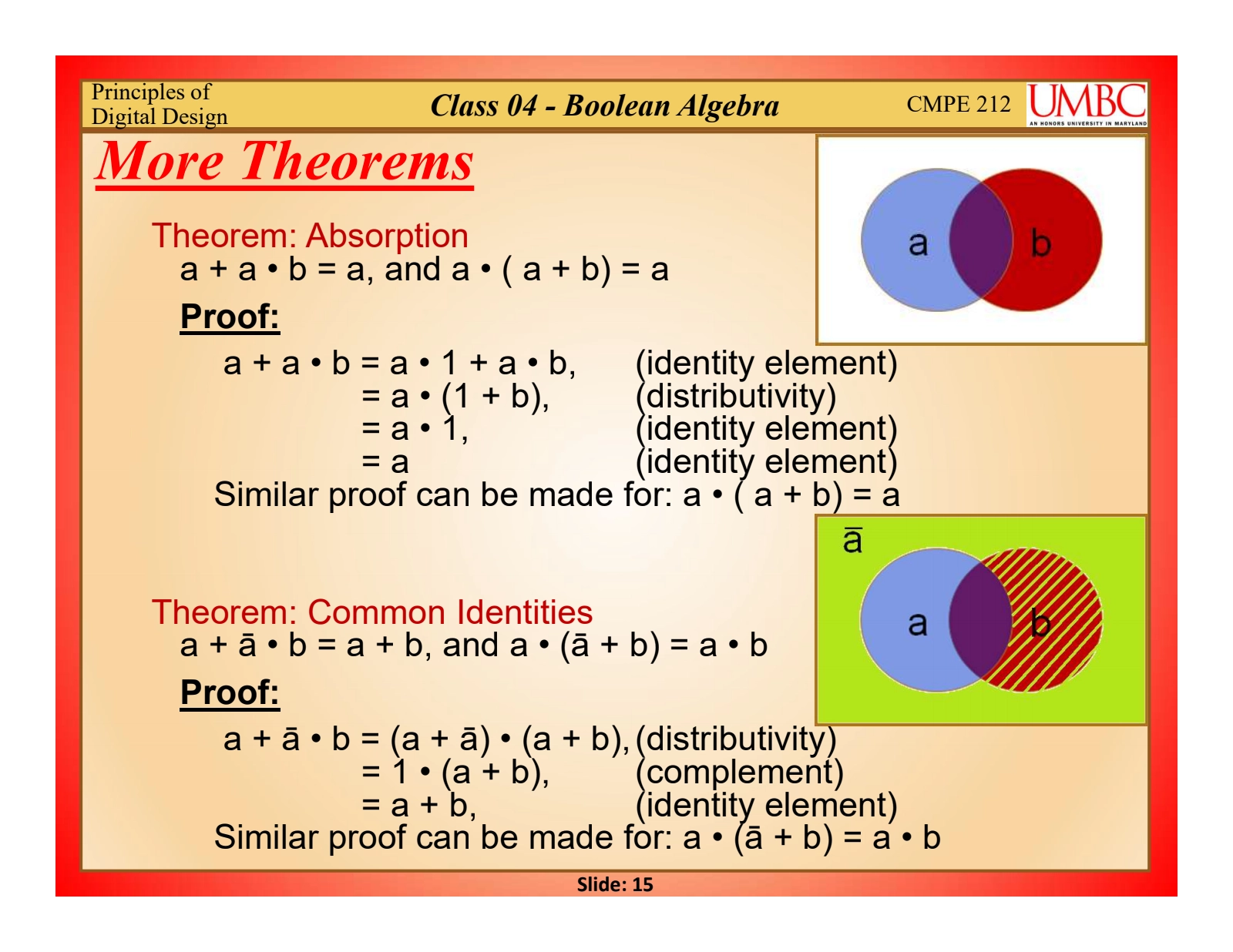

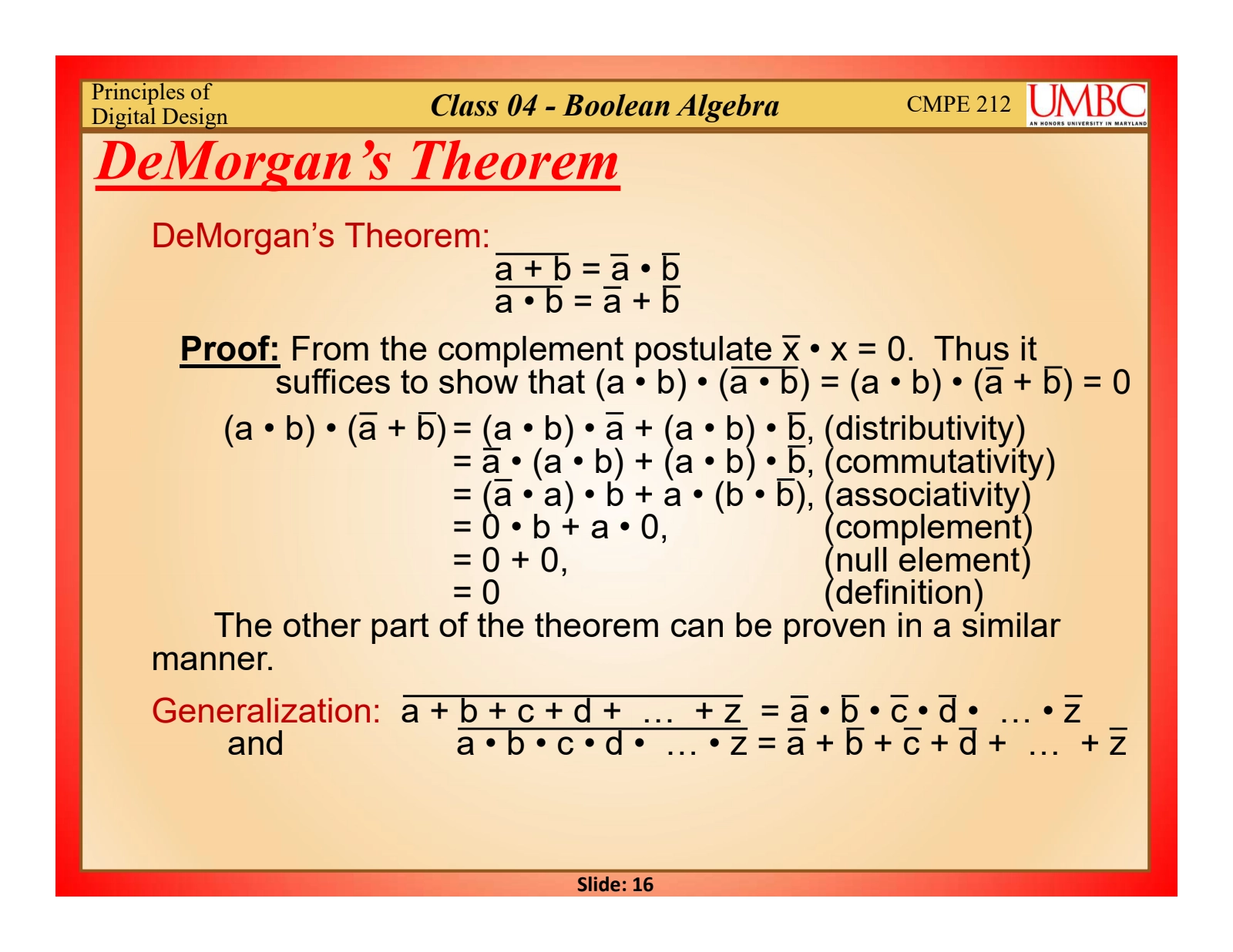

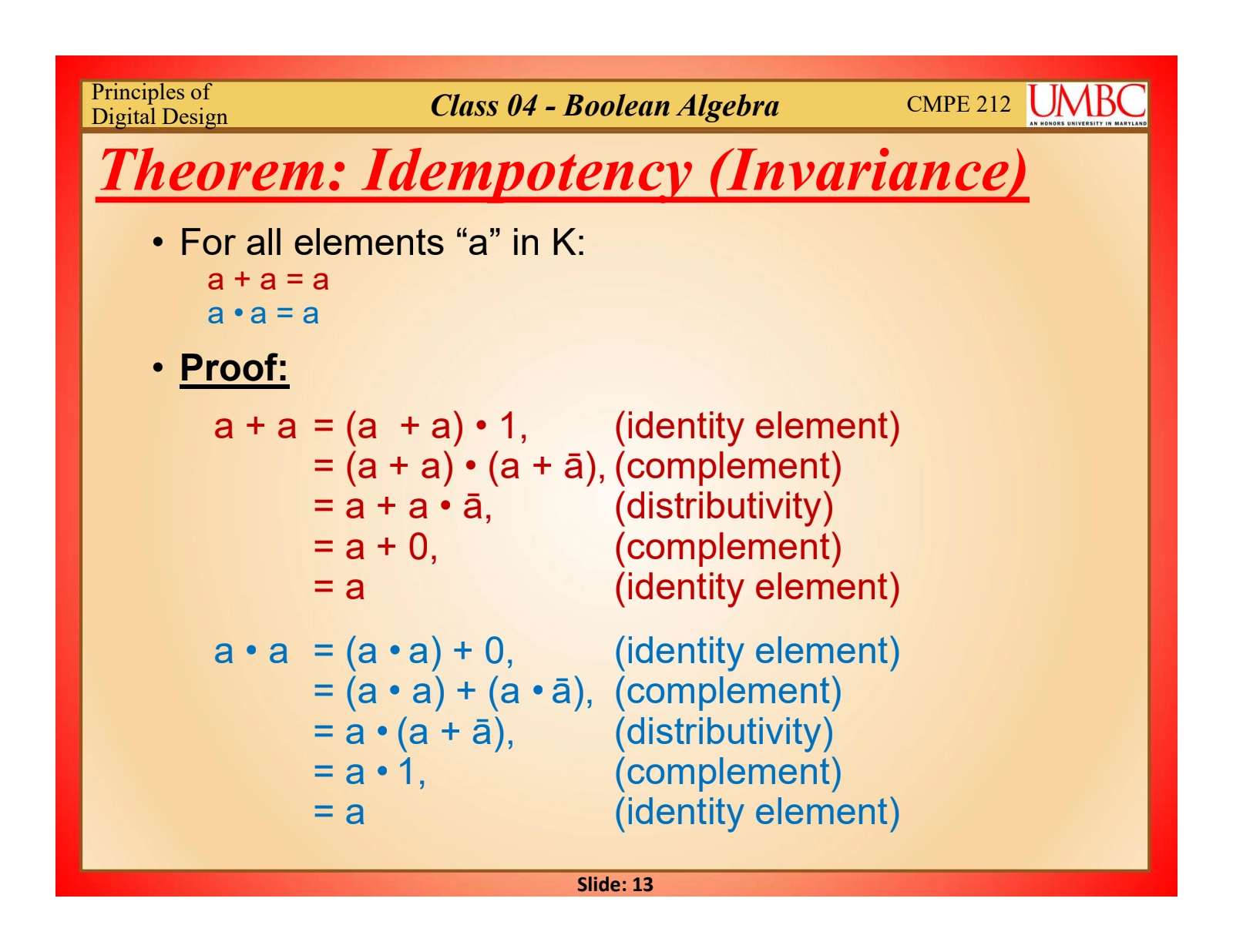

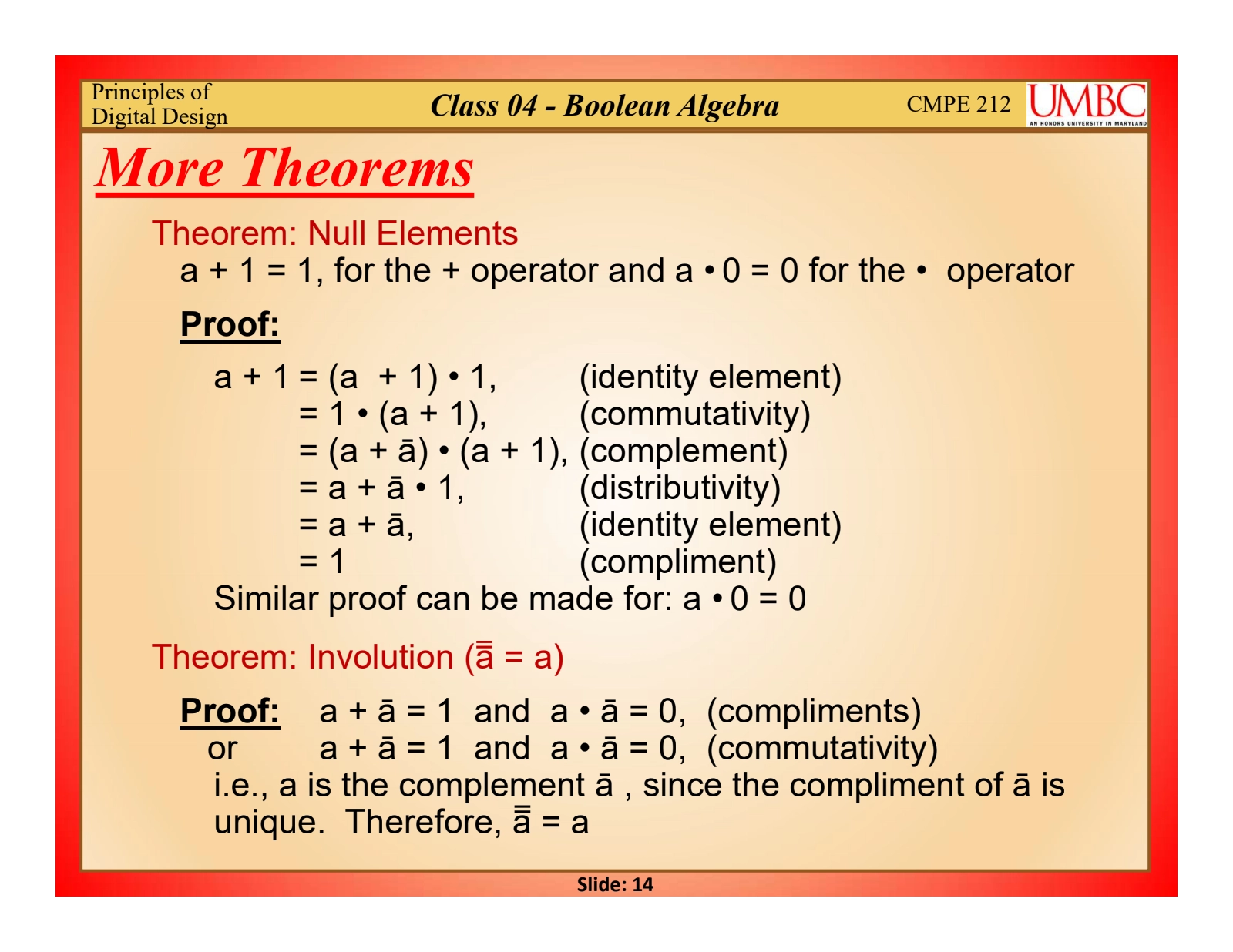

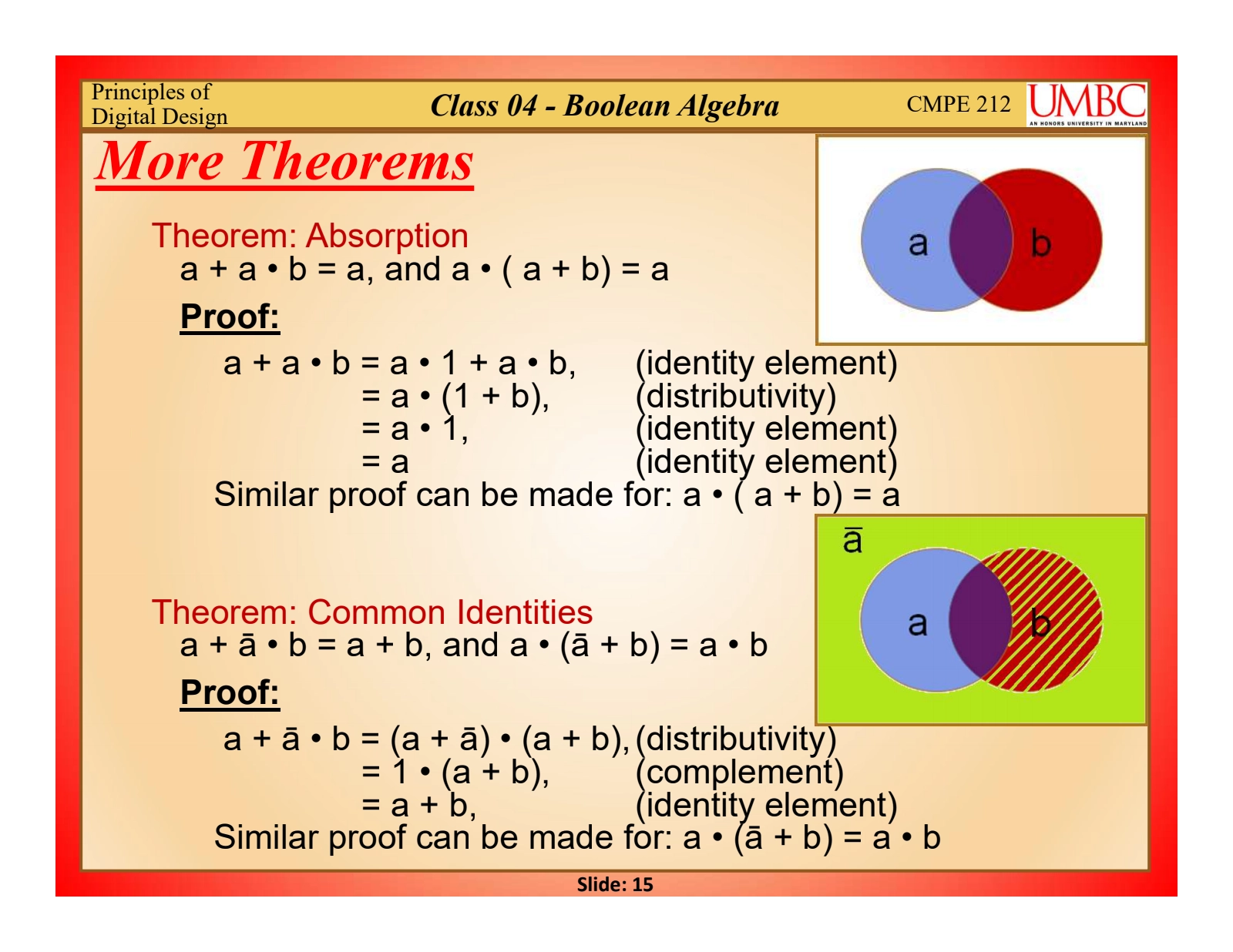

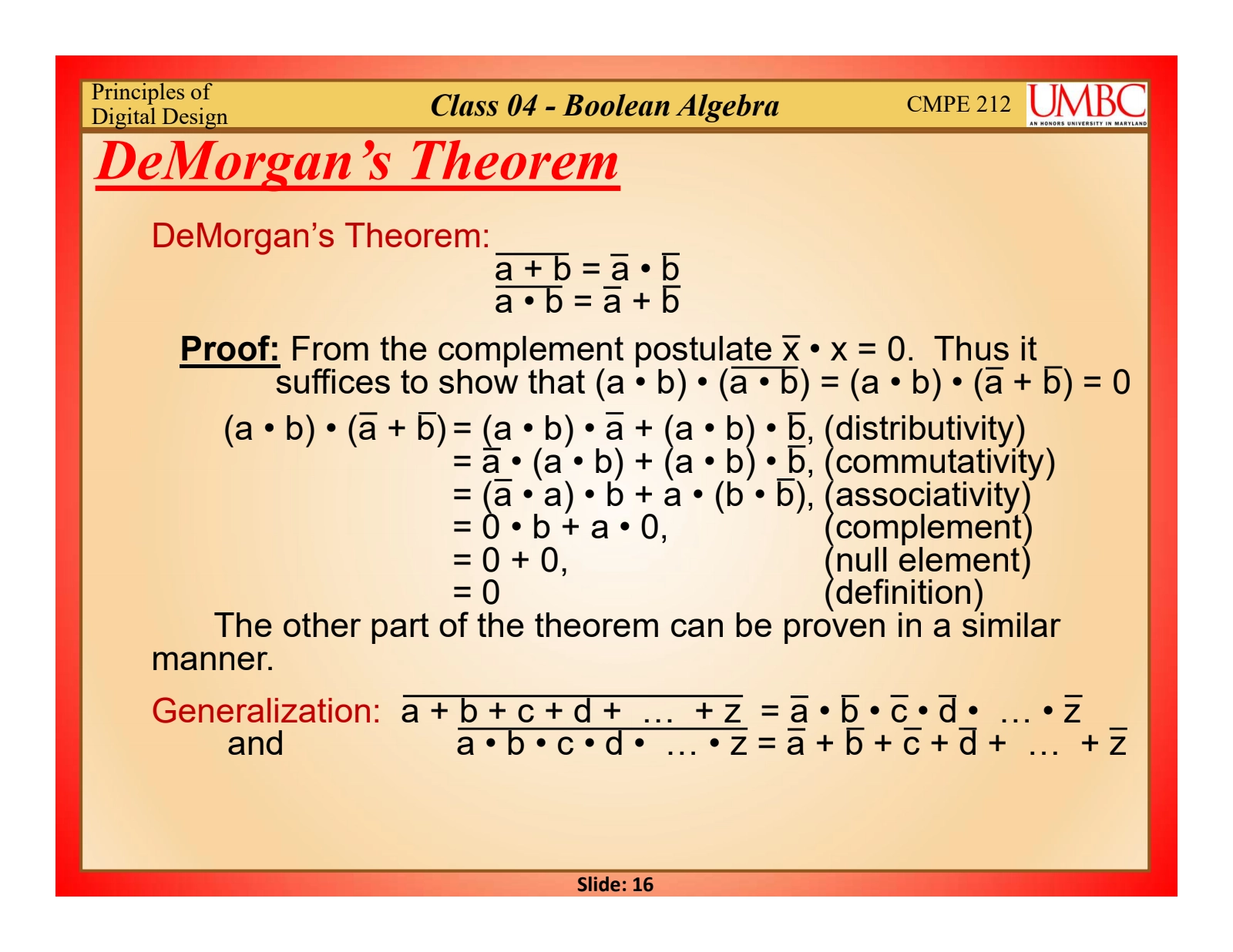

Class: 4, slide: 13-16 → More Boolean Theorms, Invariance, Null Elements, DeMorgan's

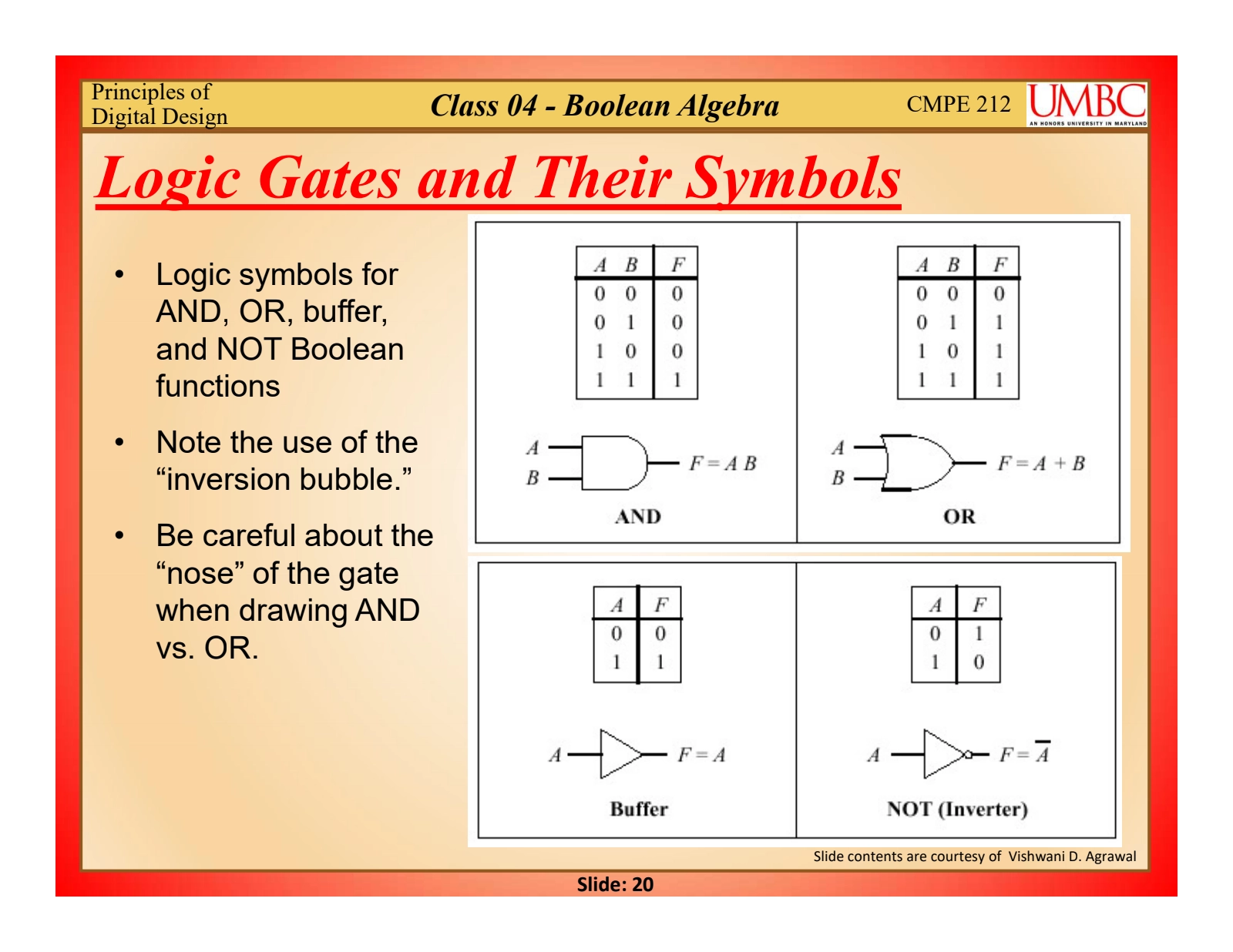

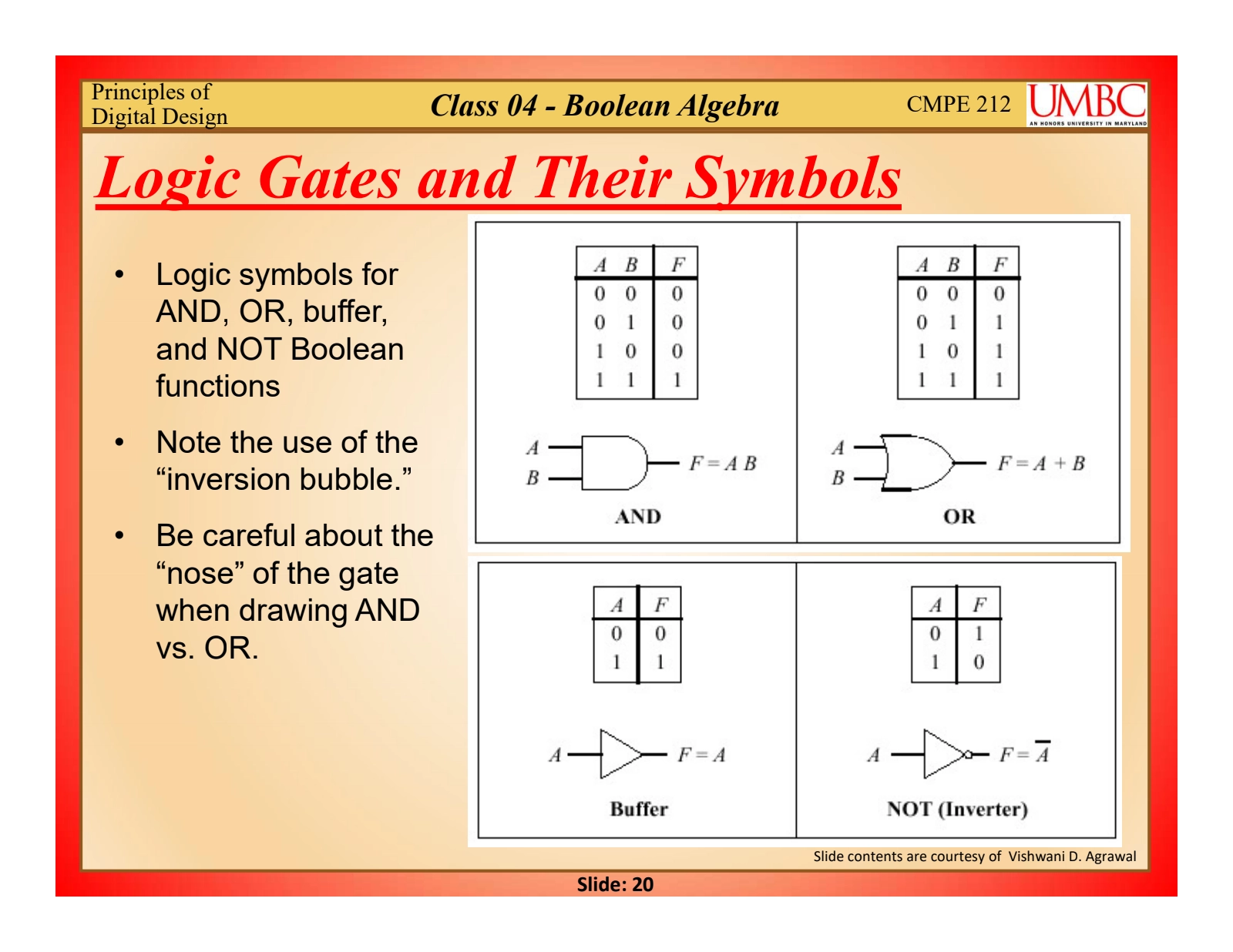

Class: 4, slide: 20 → Logic Gates and their Symbols

Materials to Review for Quiz 2:

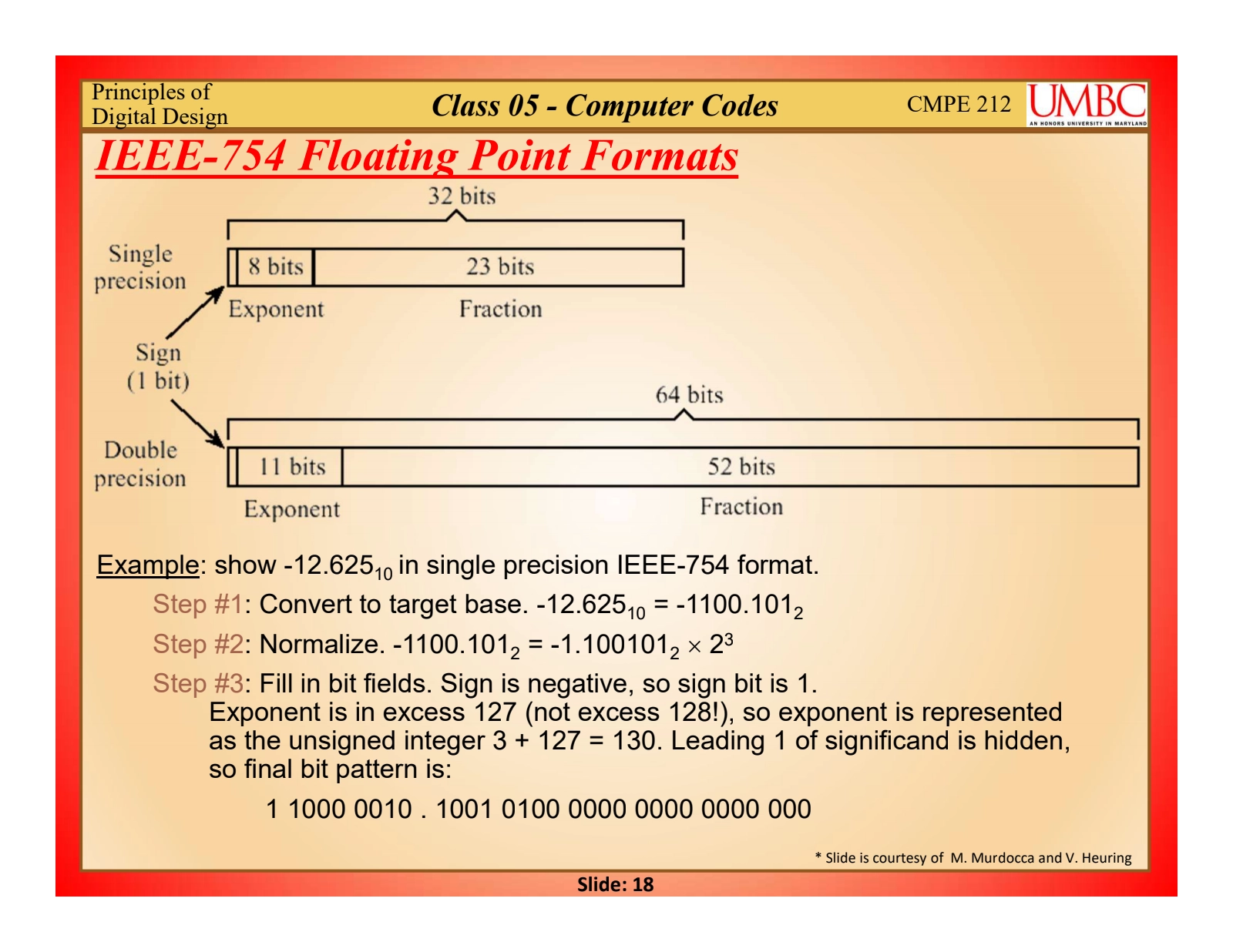

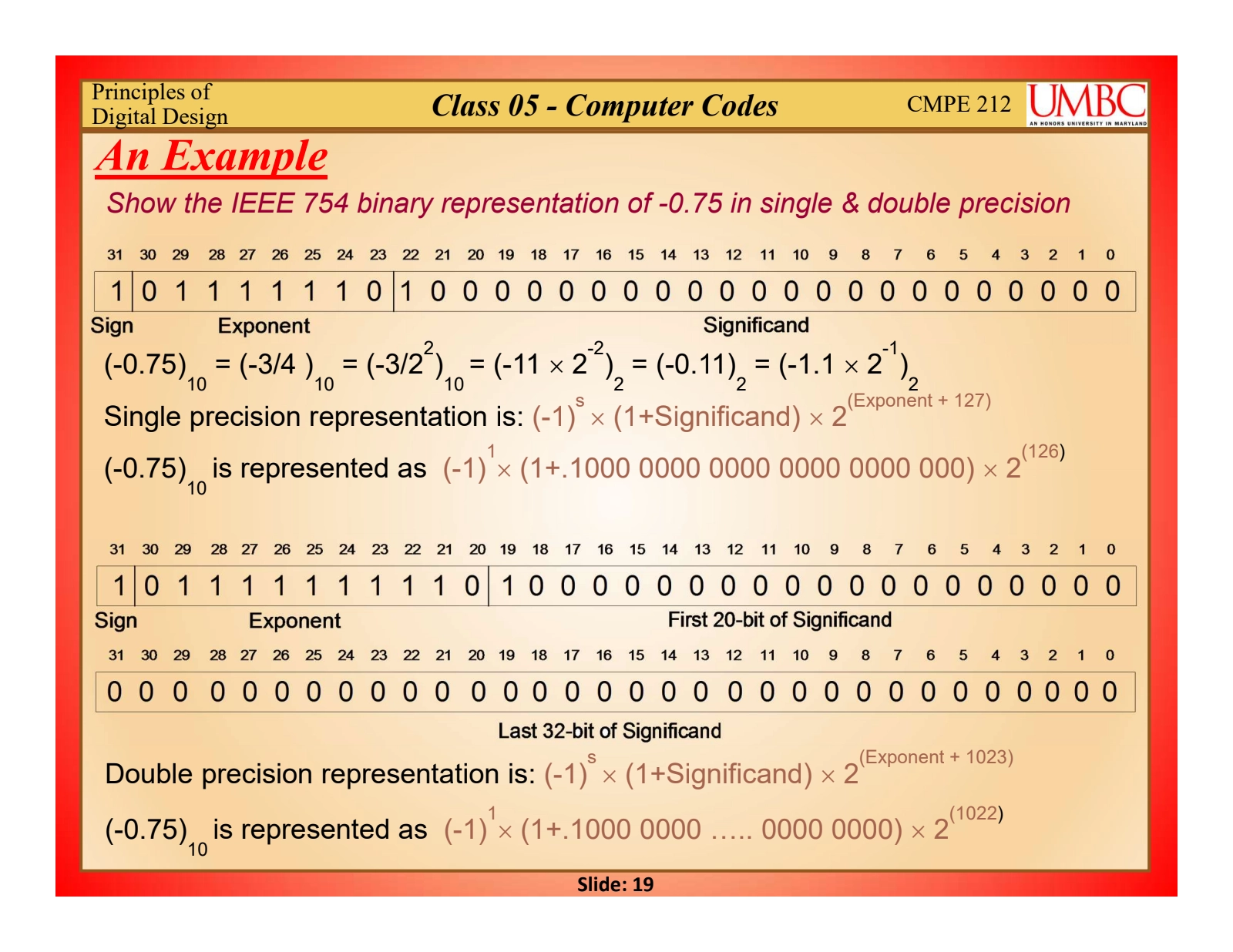

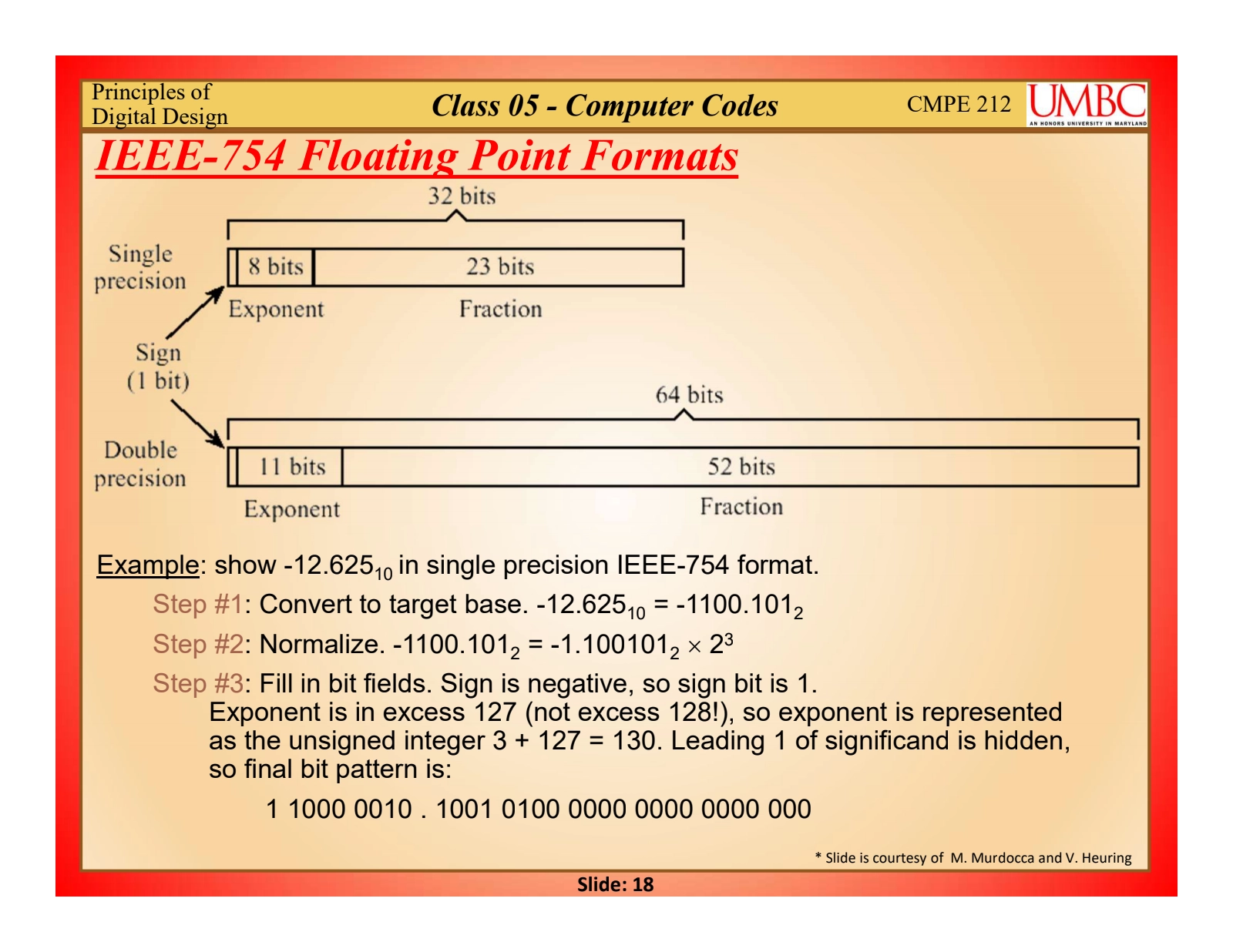

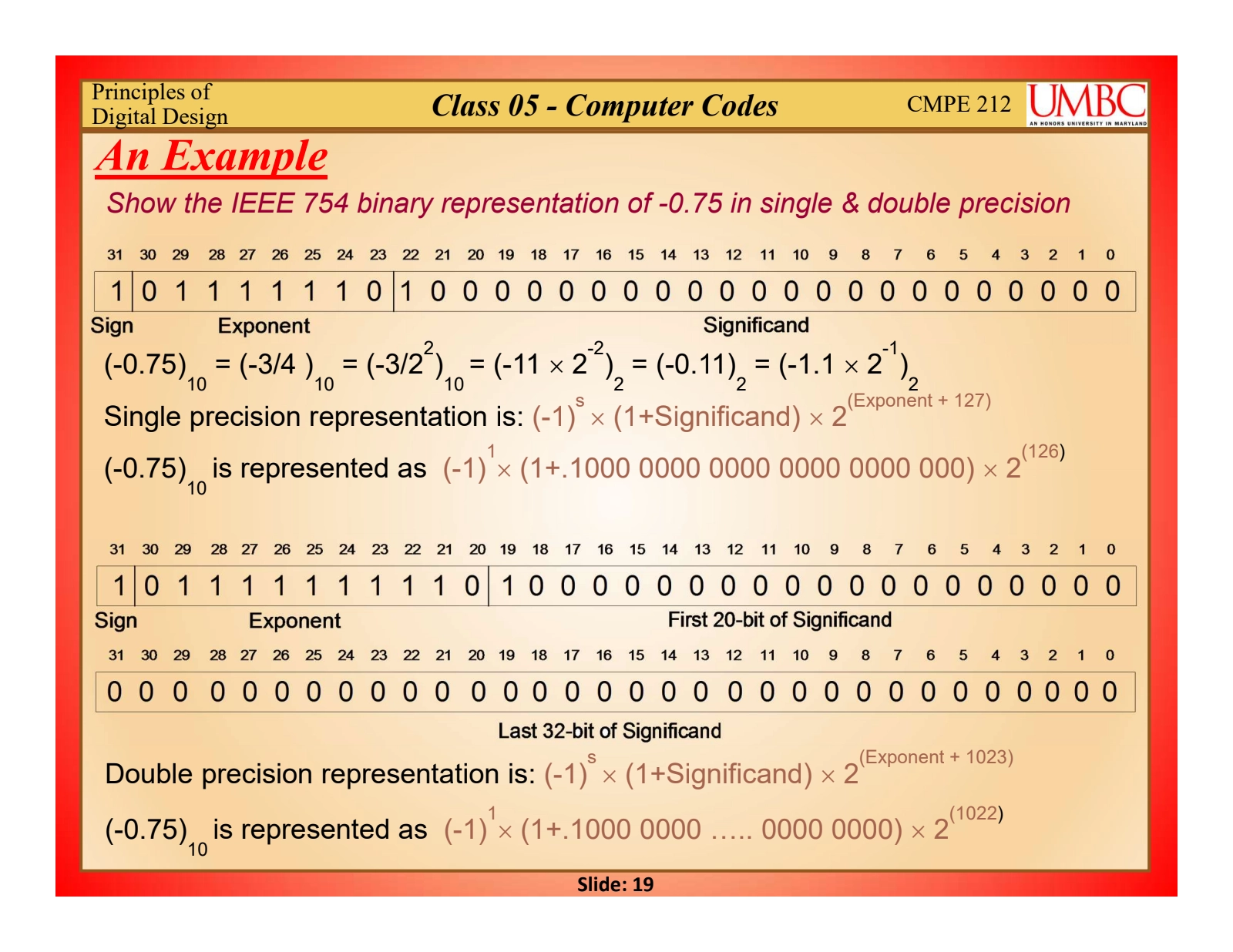

Class: 5, slide: 19 → Floating Point with example (ref slide 18)

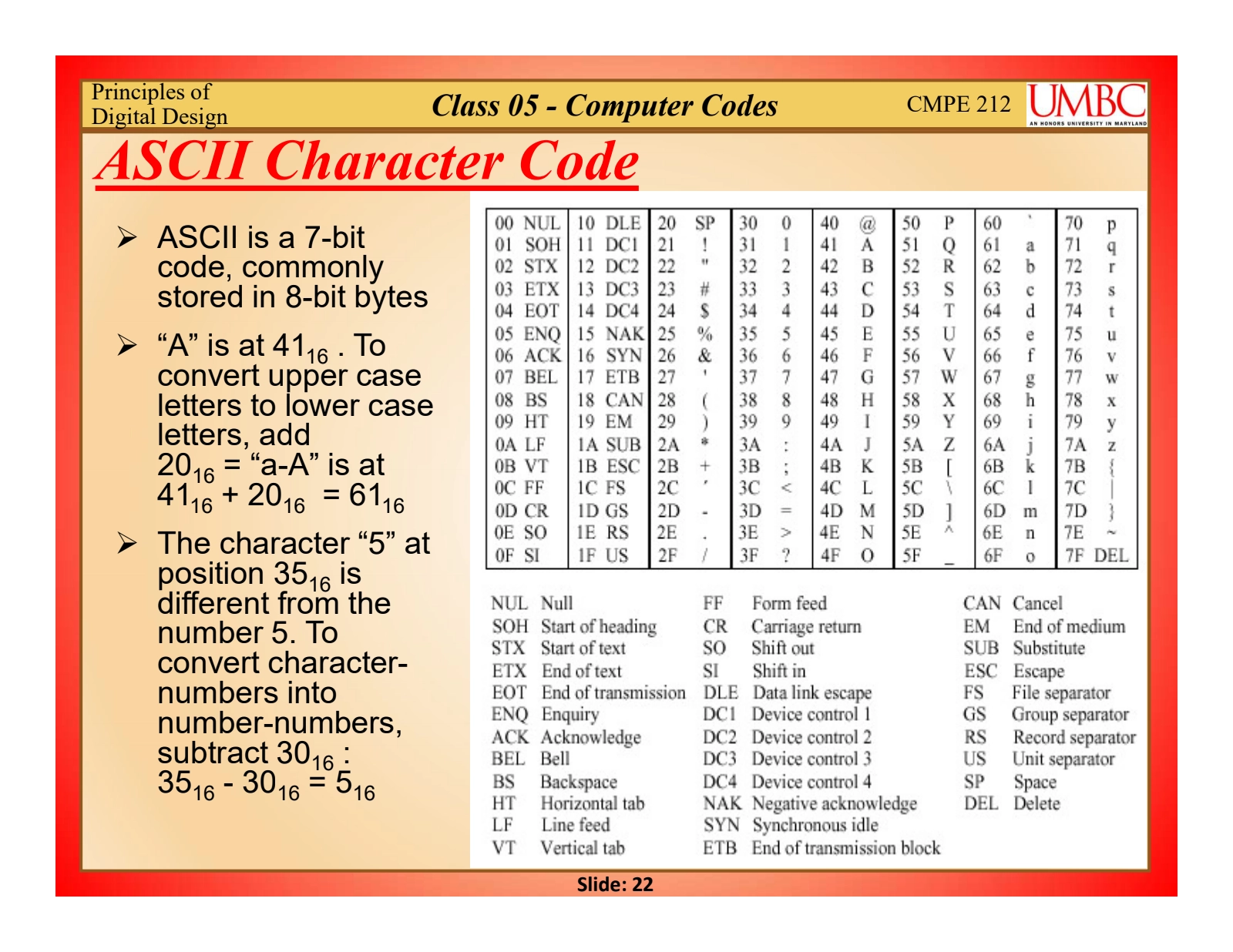

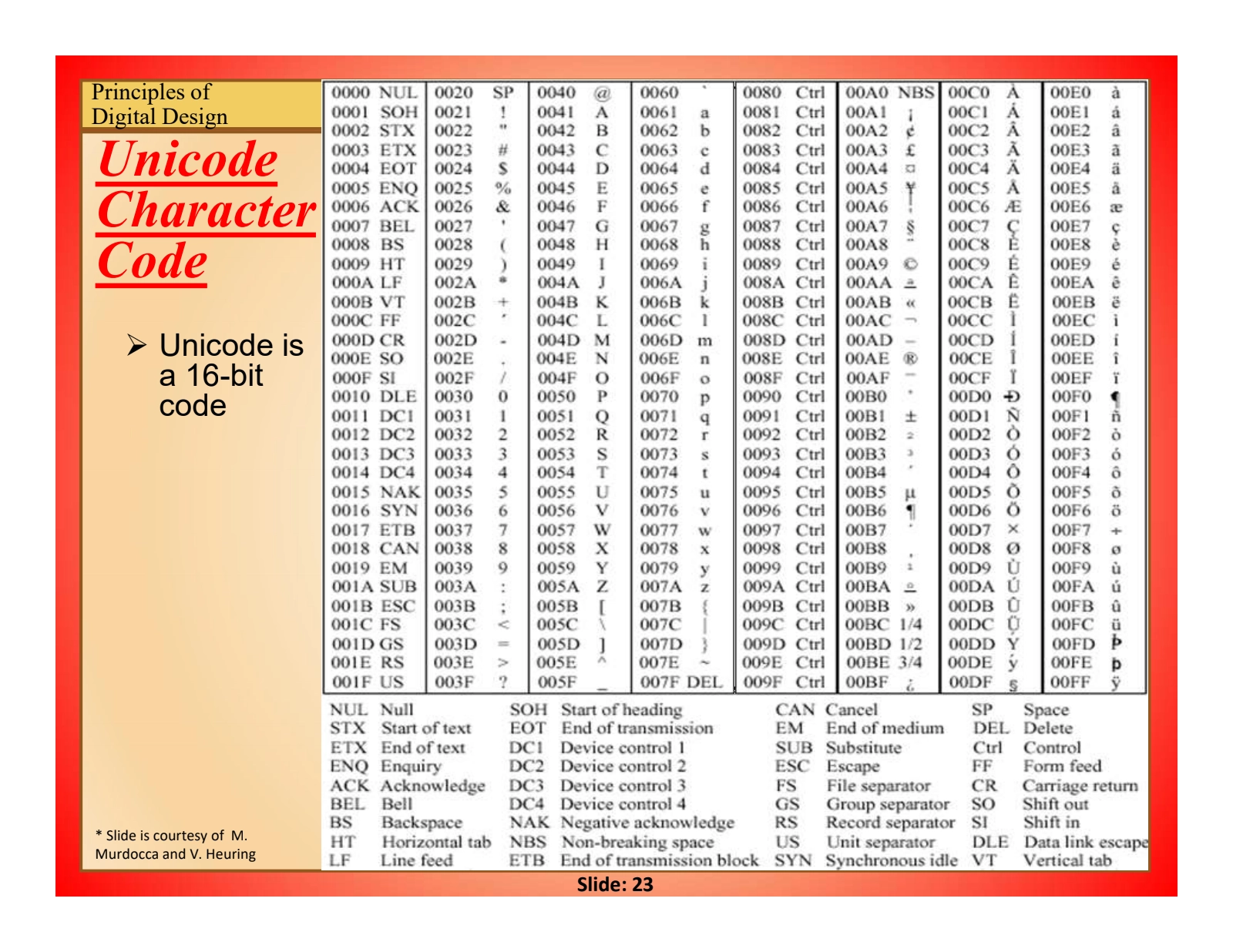

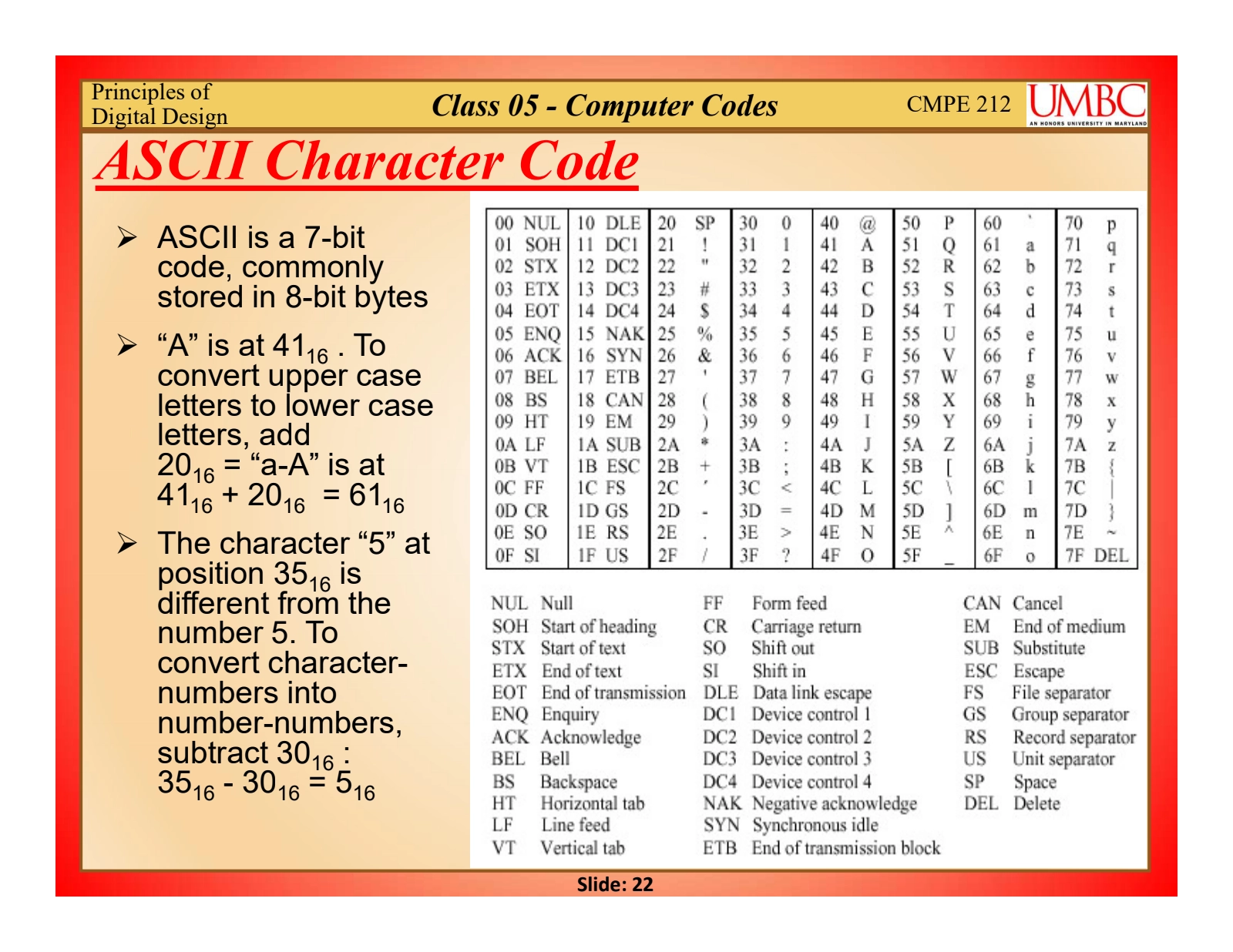

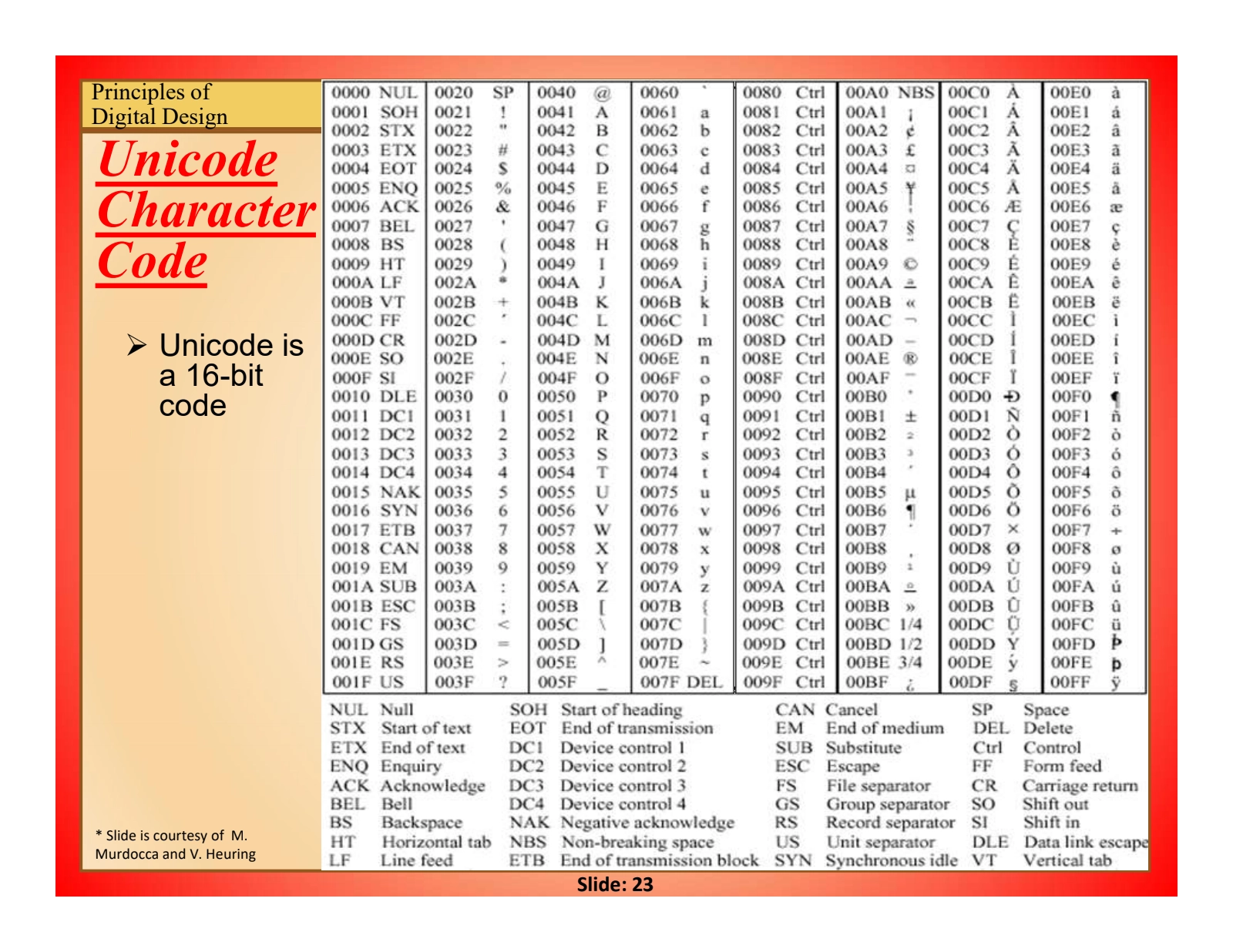

Class: 5, slide: 22-23 → Ascii - know how to convert letters and Numbers

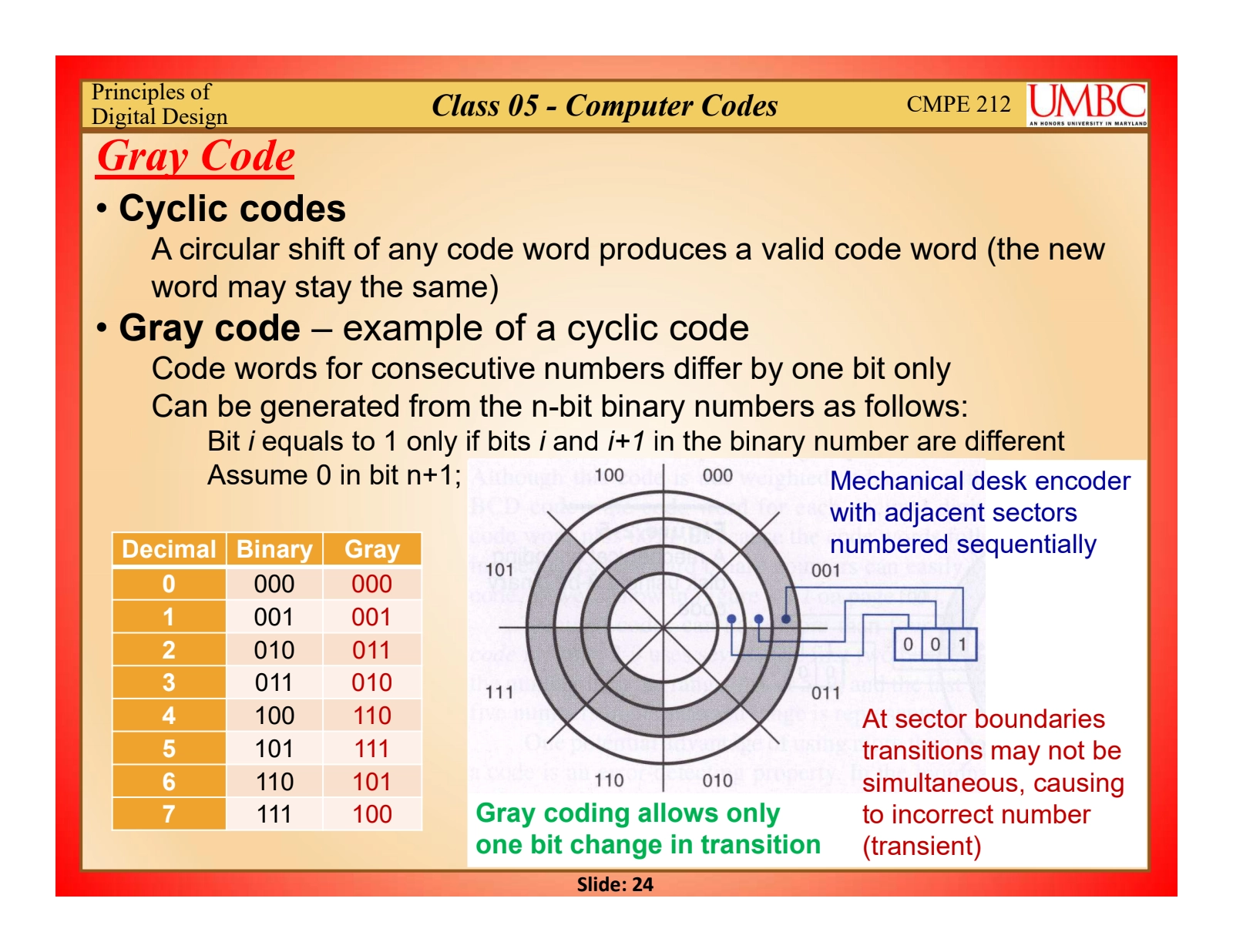

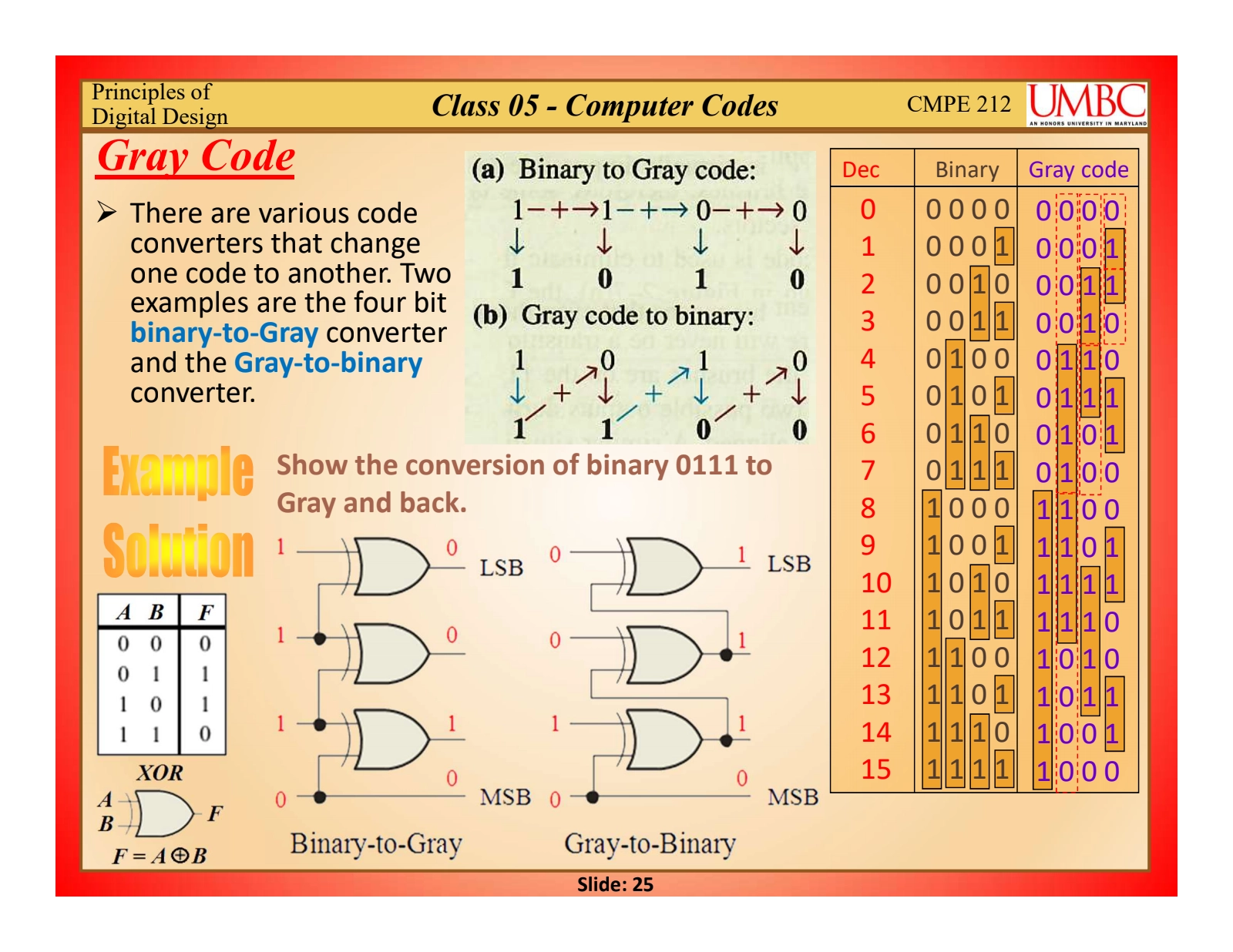

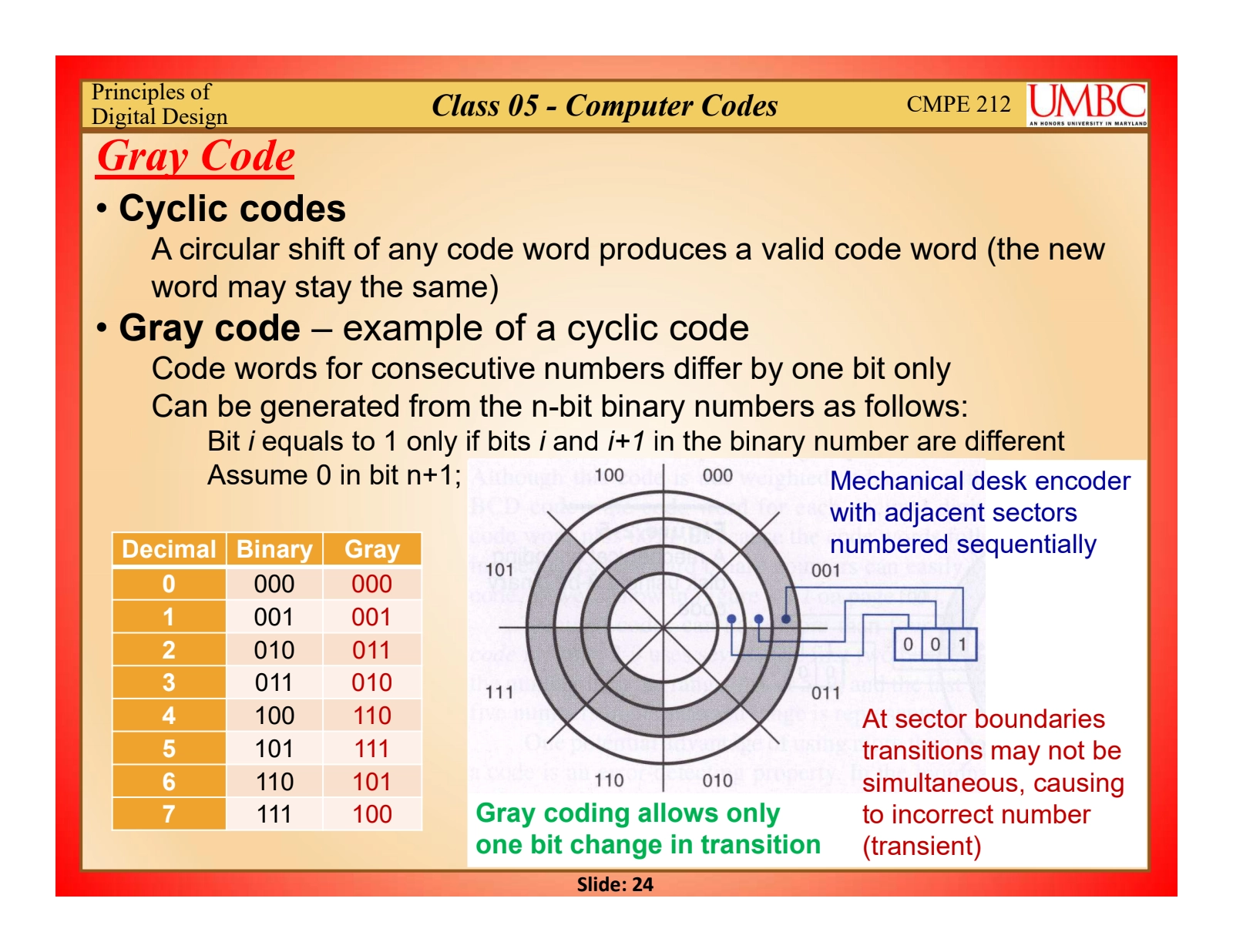

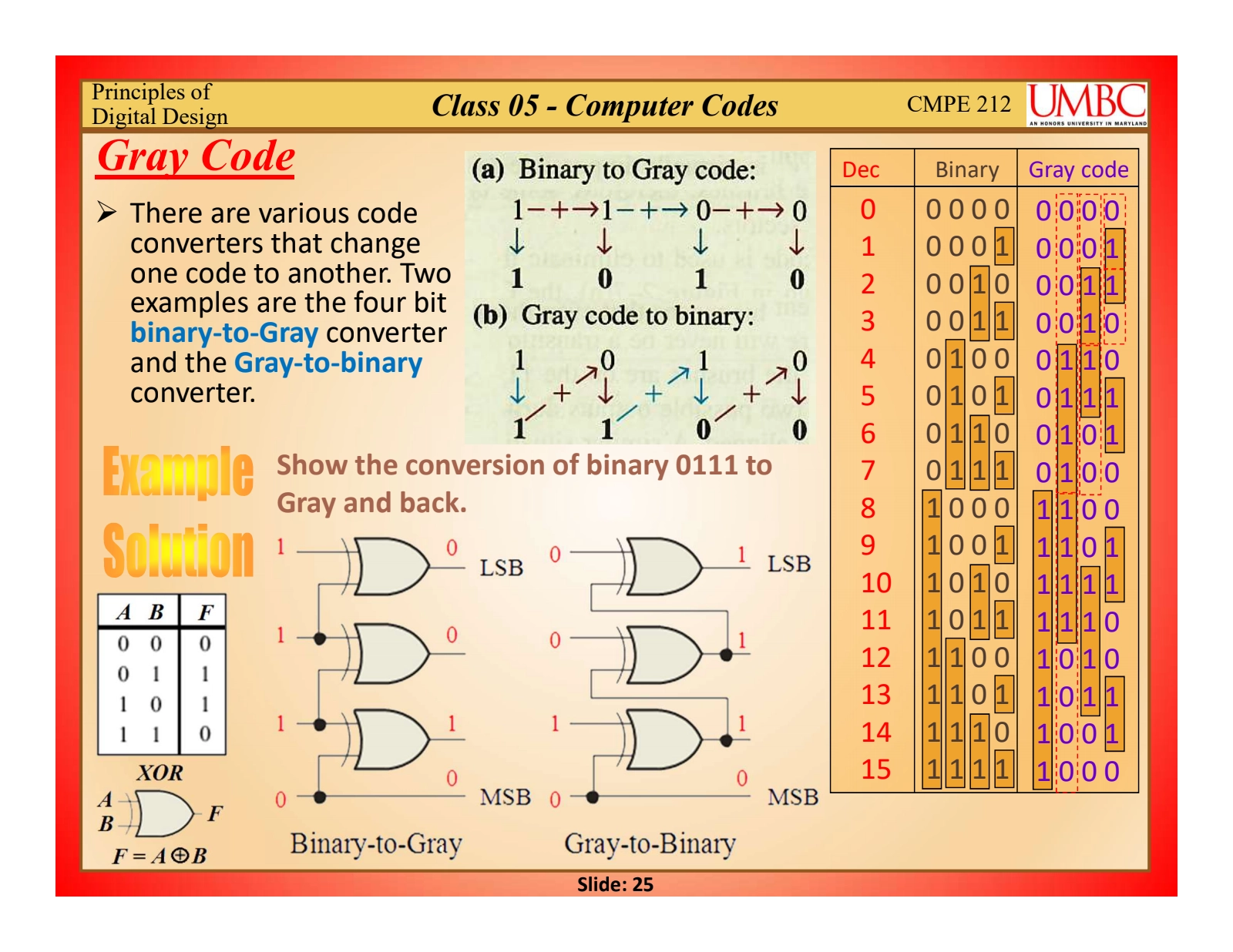

Class: 5, slide: 24-25 → Grey Code

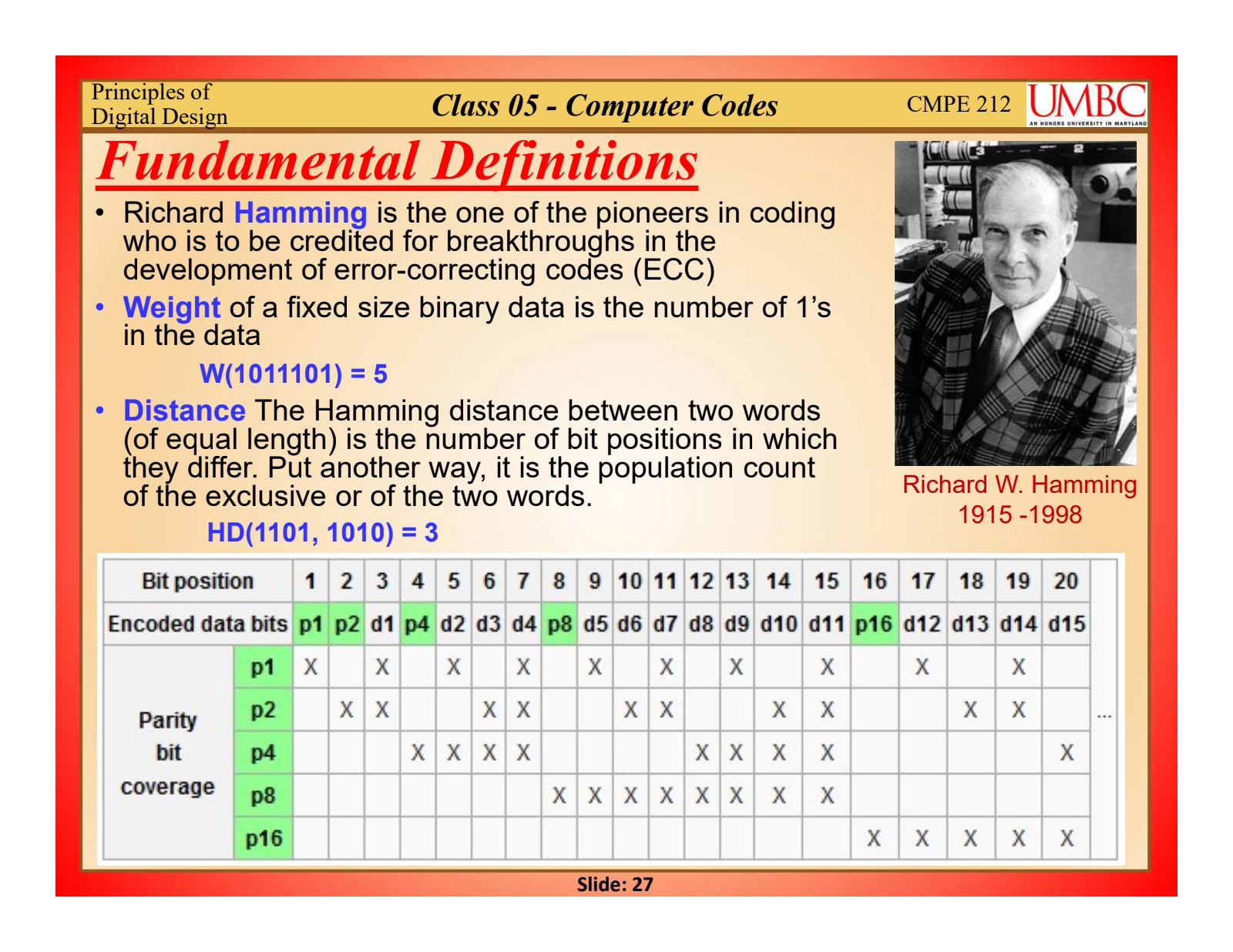

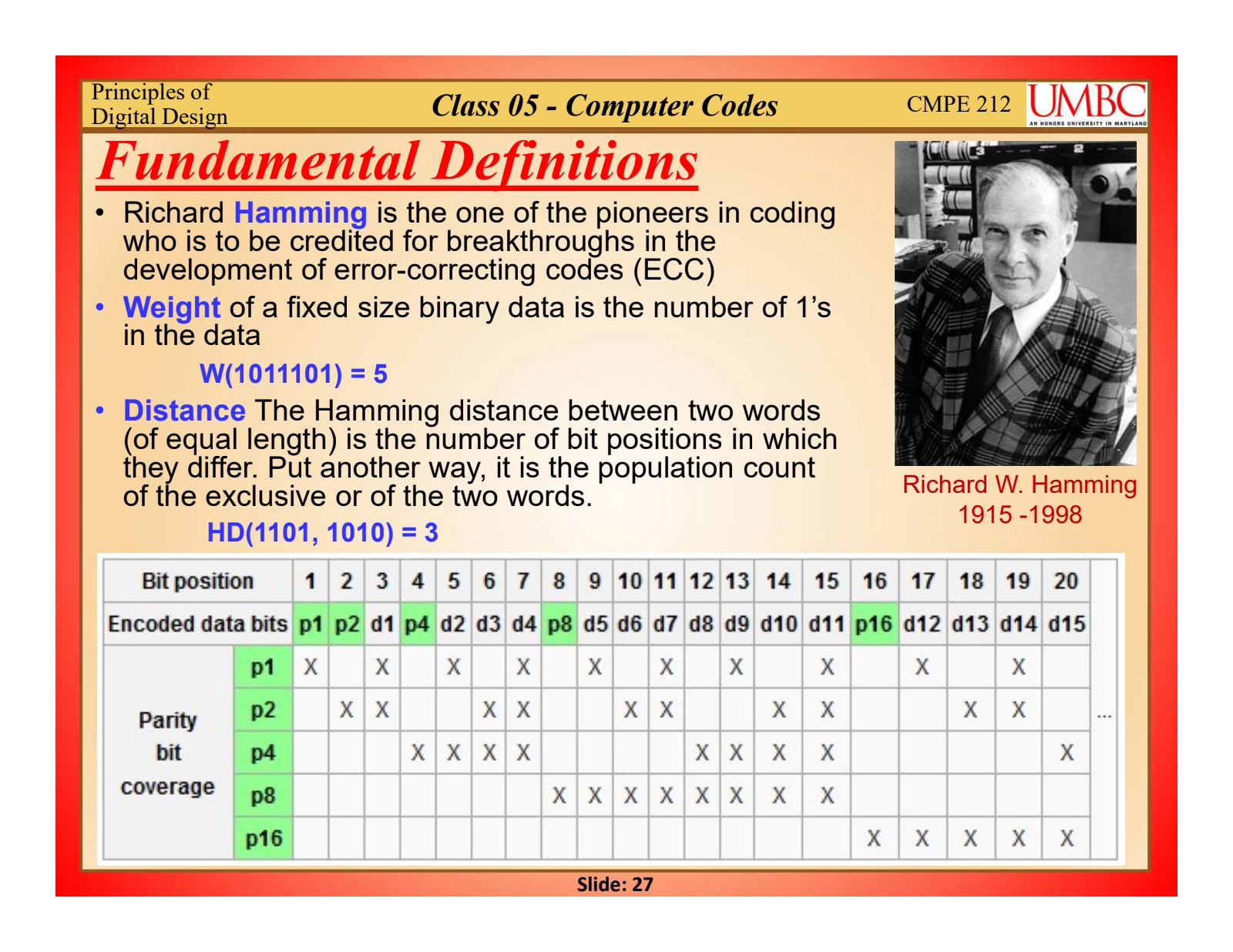

Class: 5, slide: 27 → Fundamental SECDED definitions

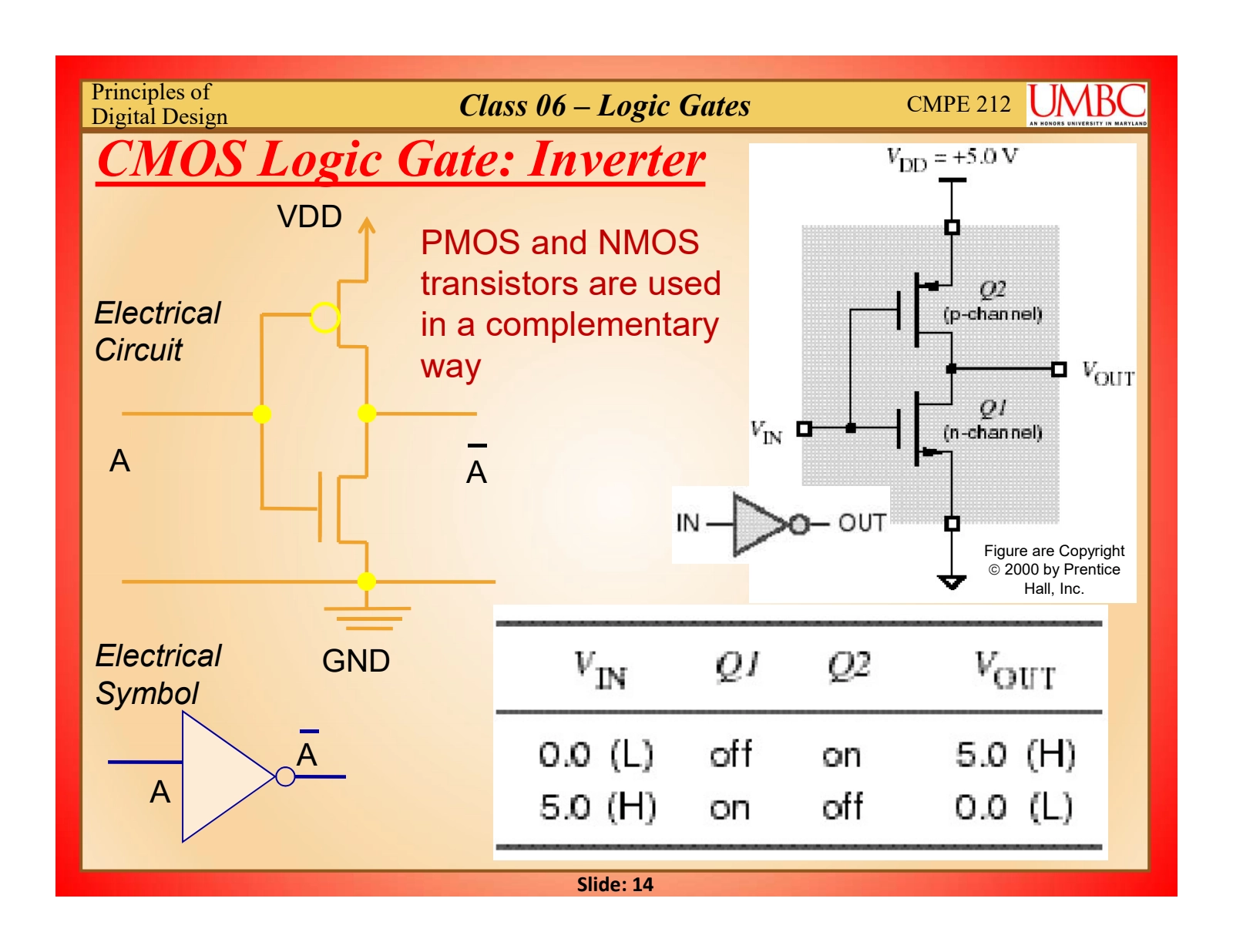

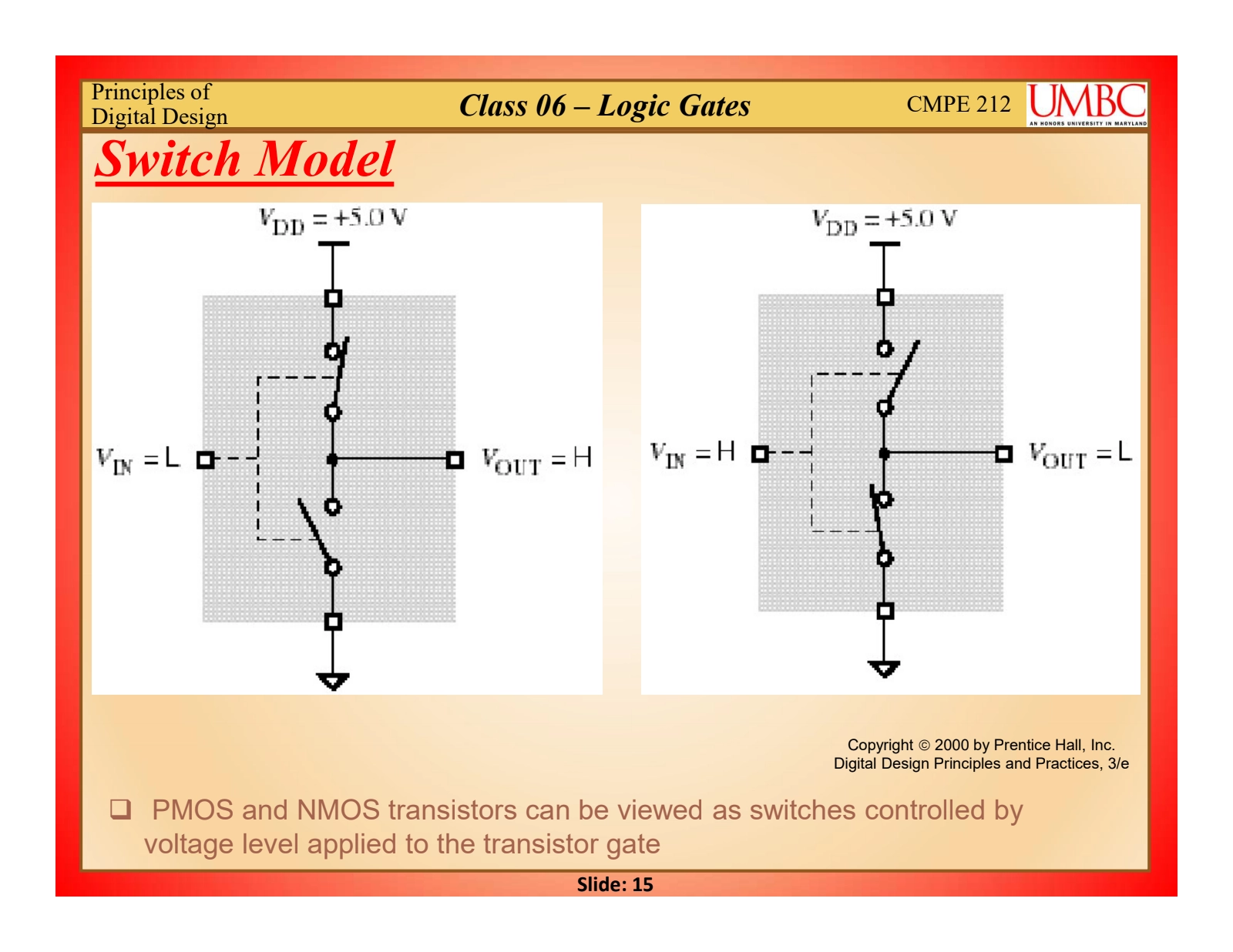

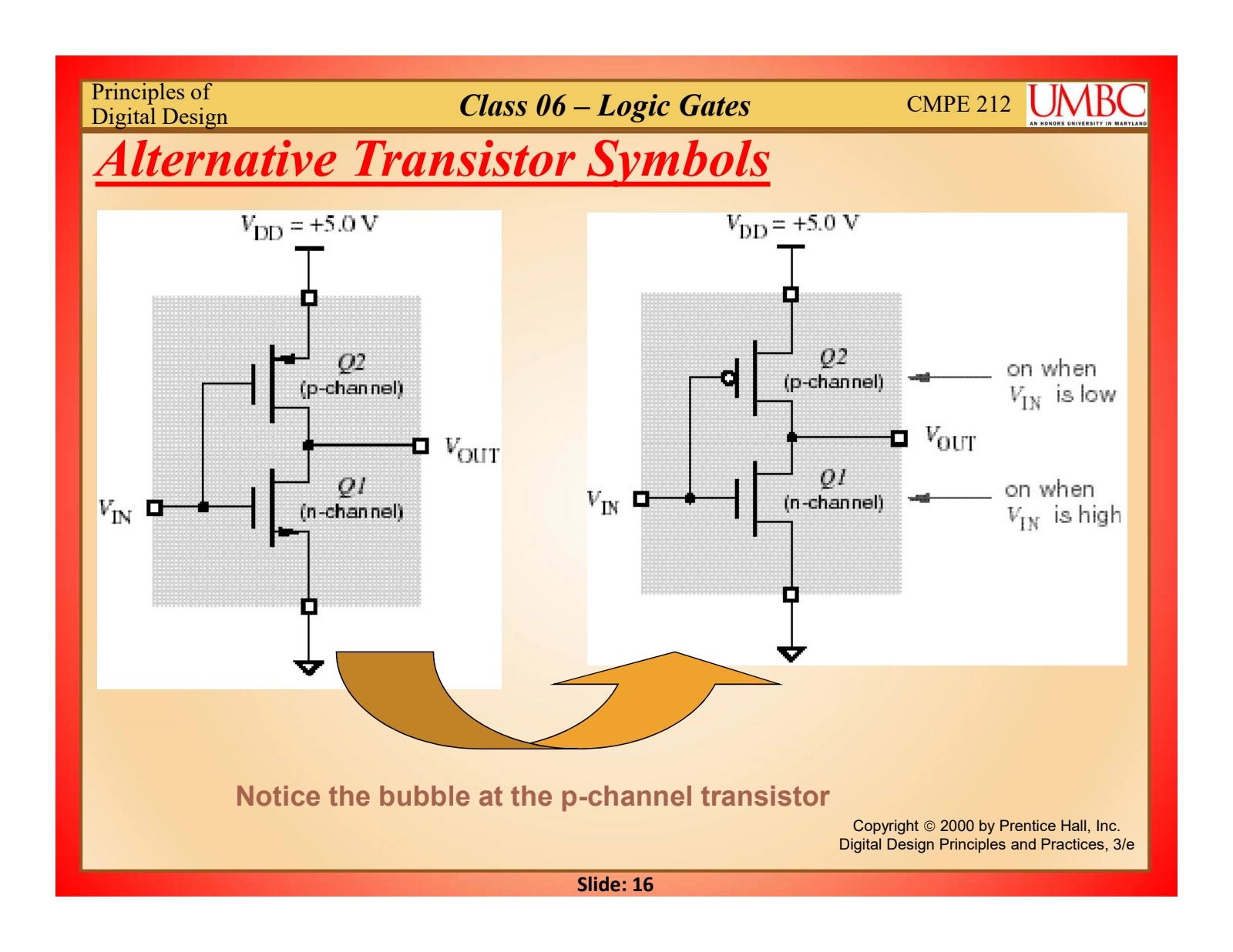

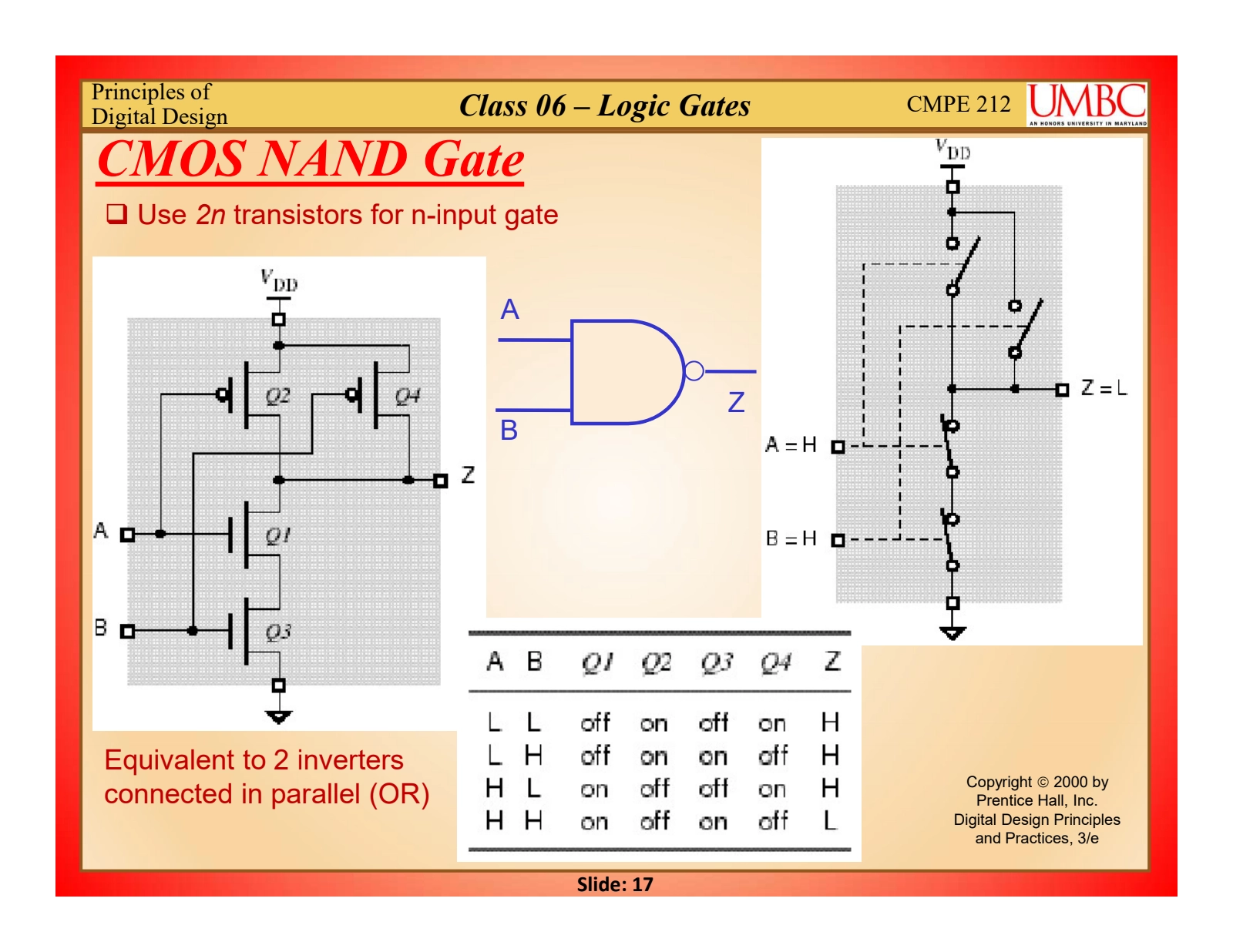

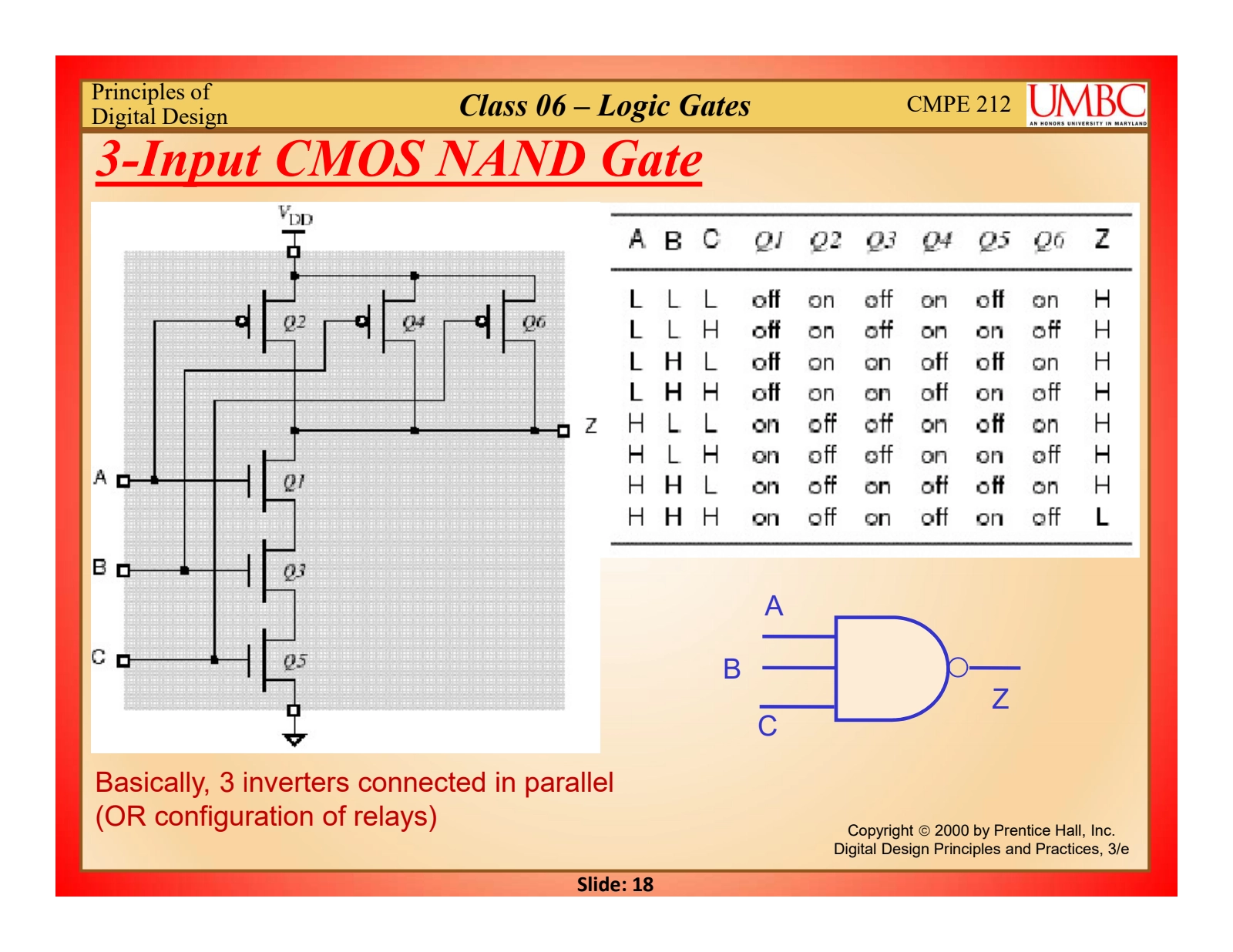

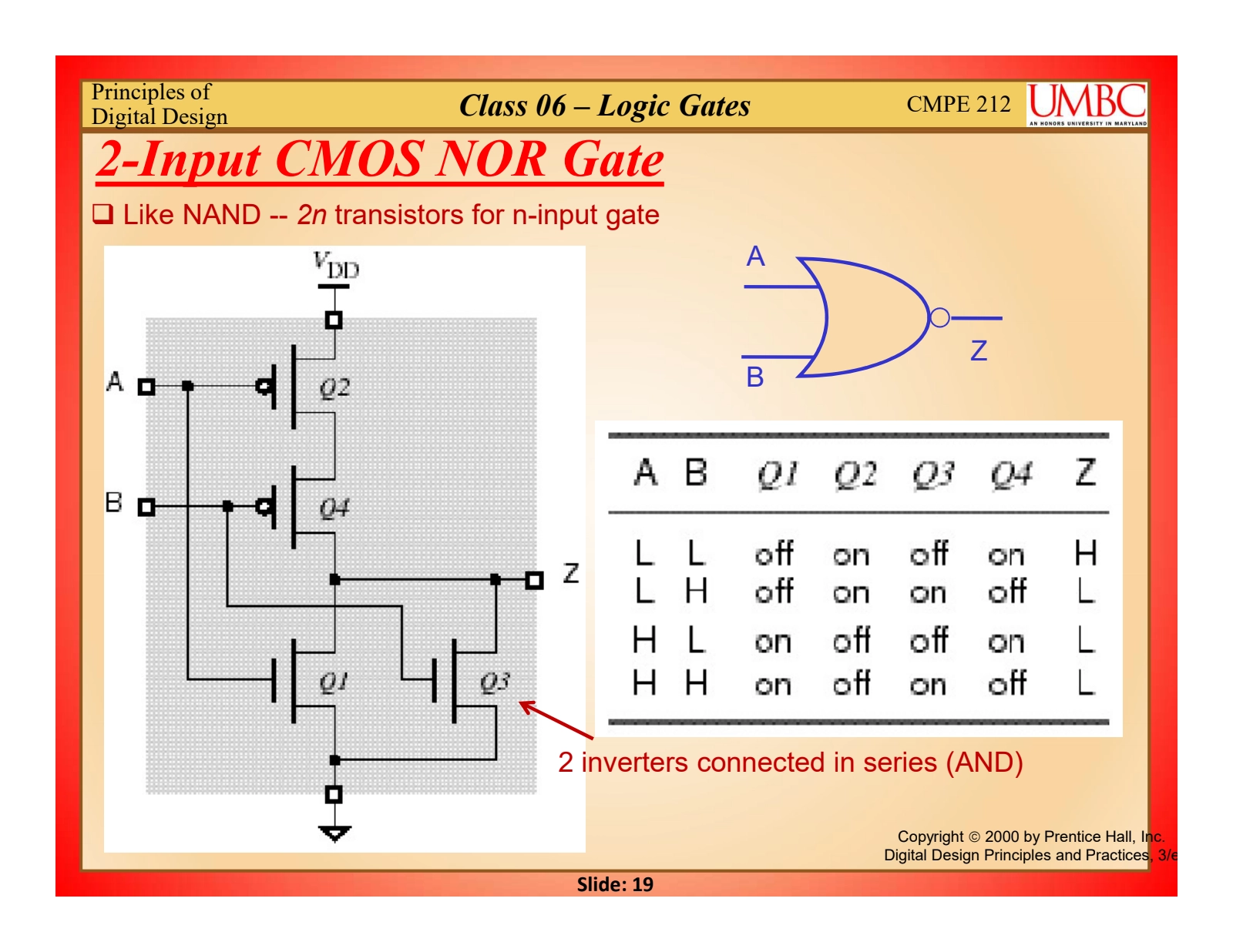

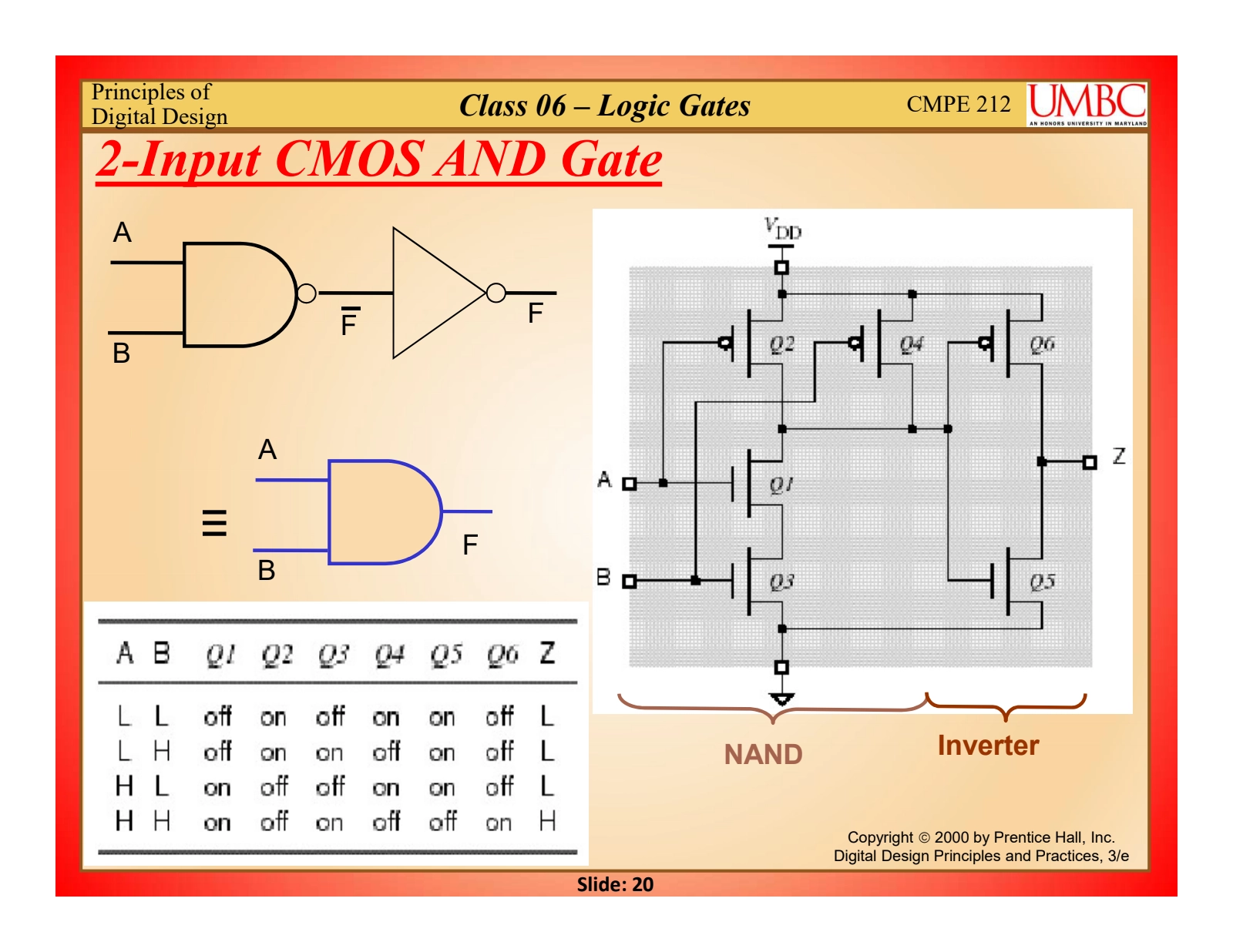

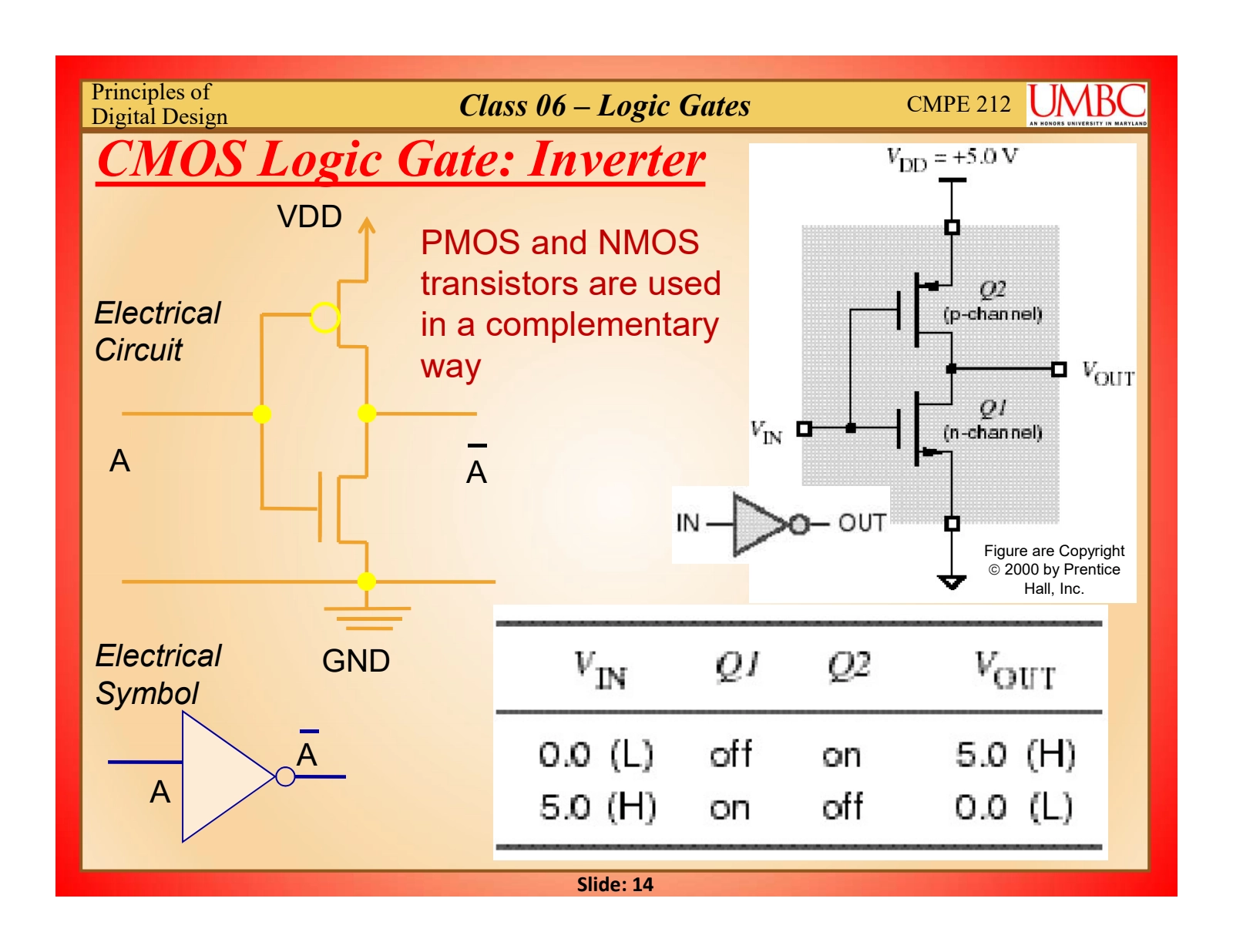

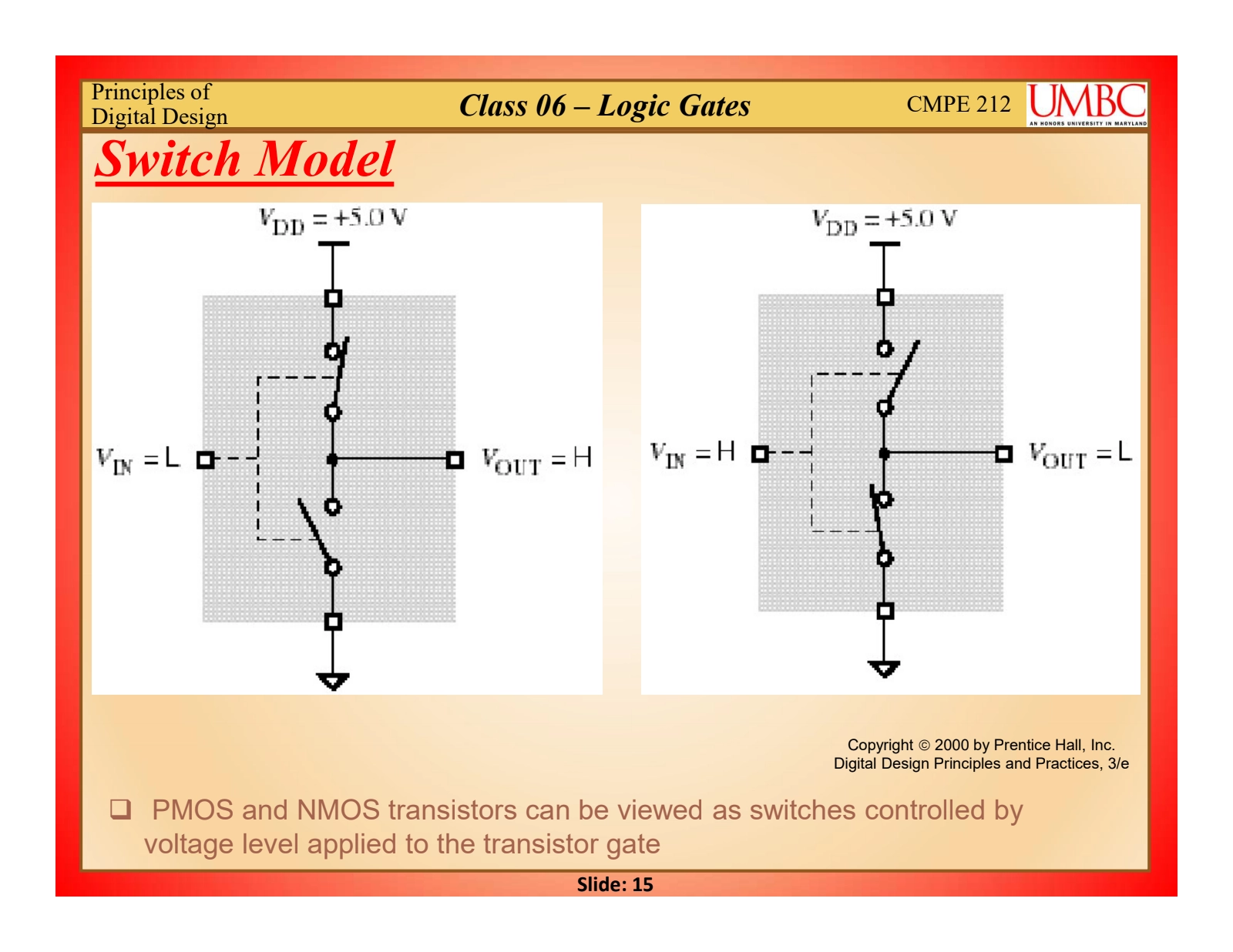

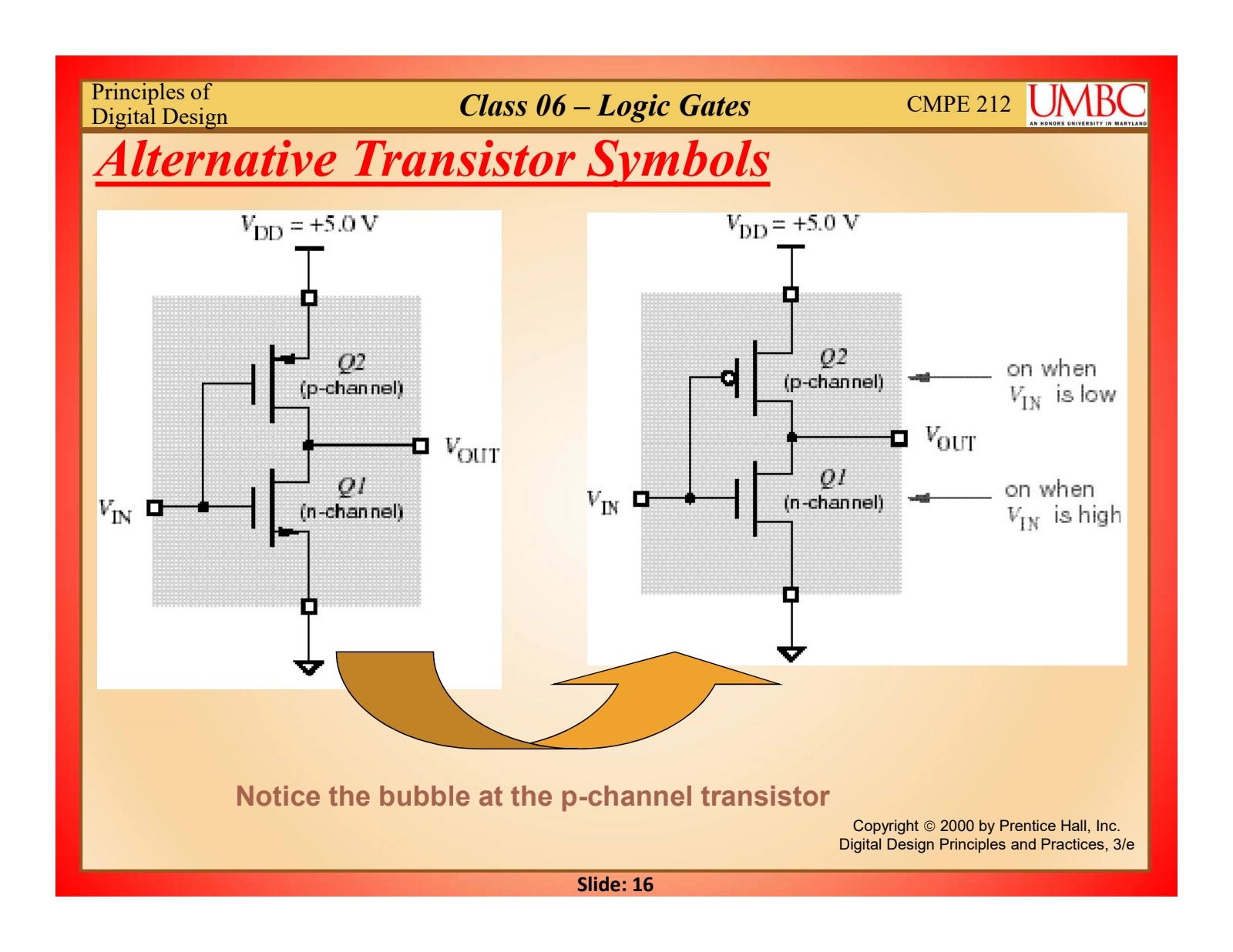

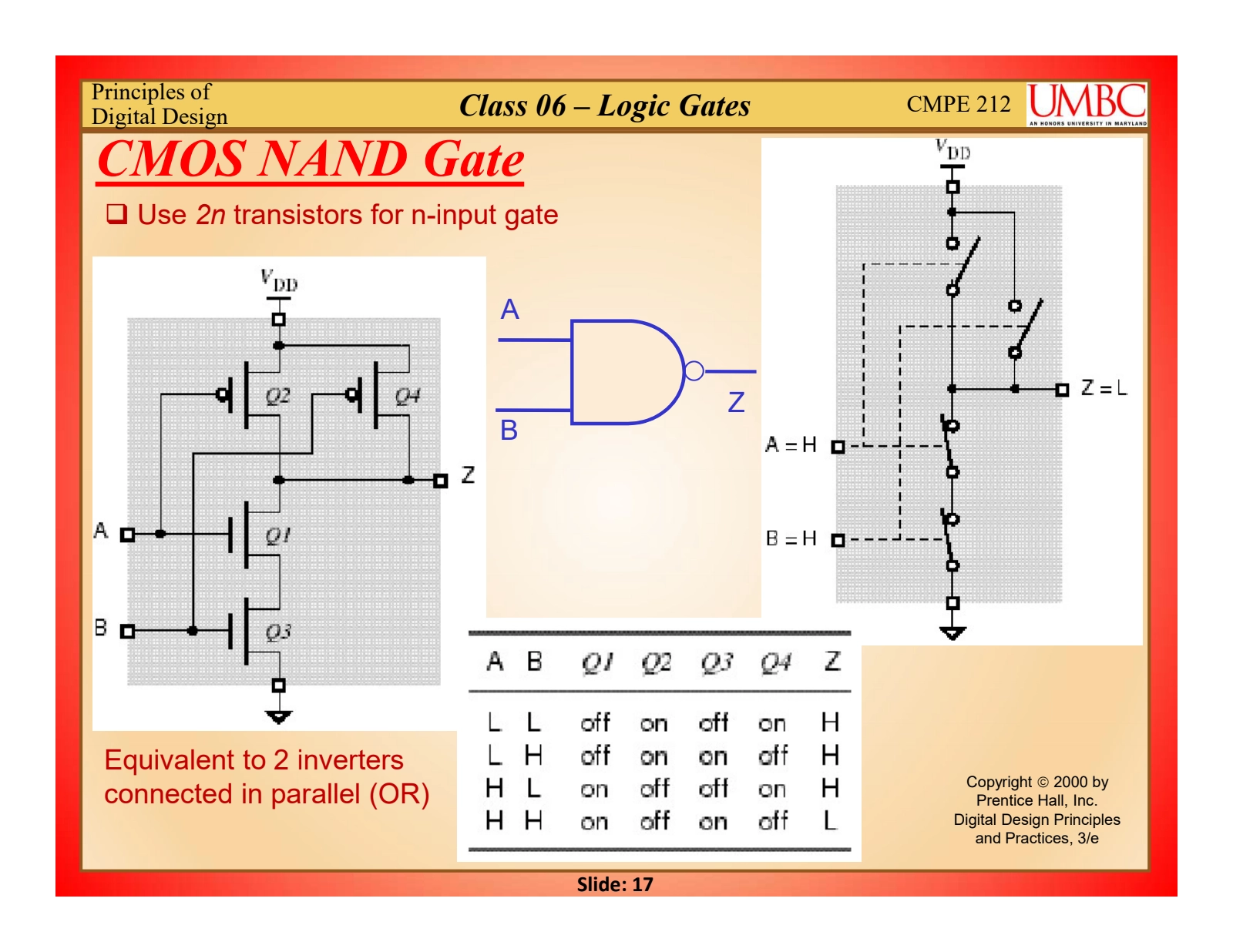

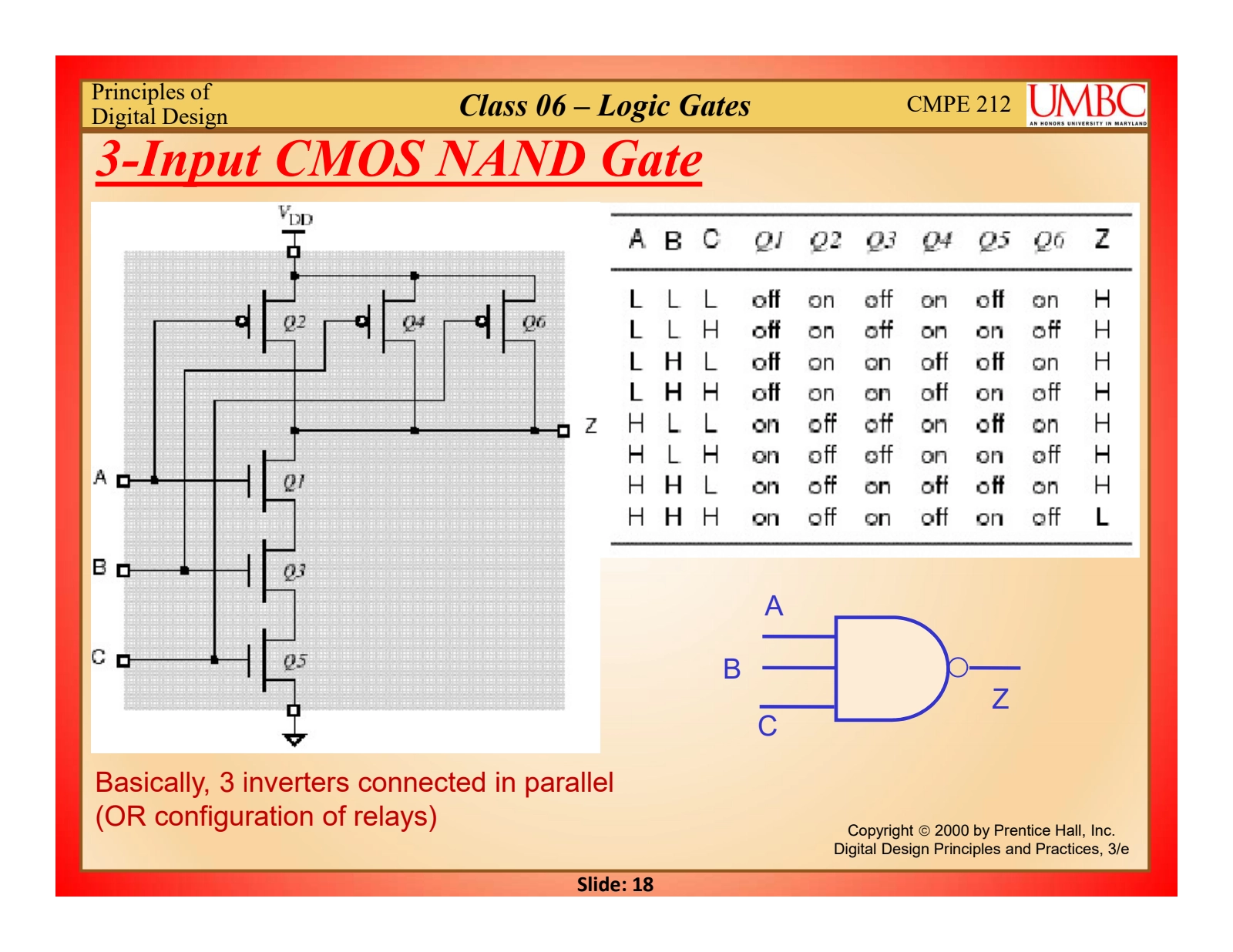

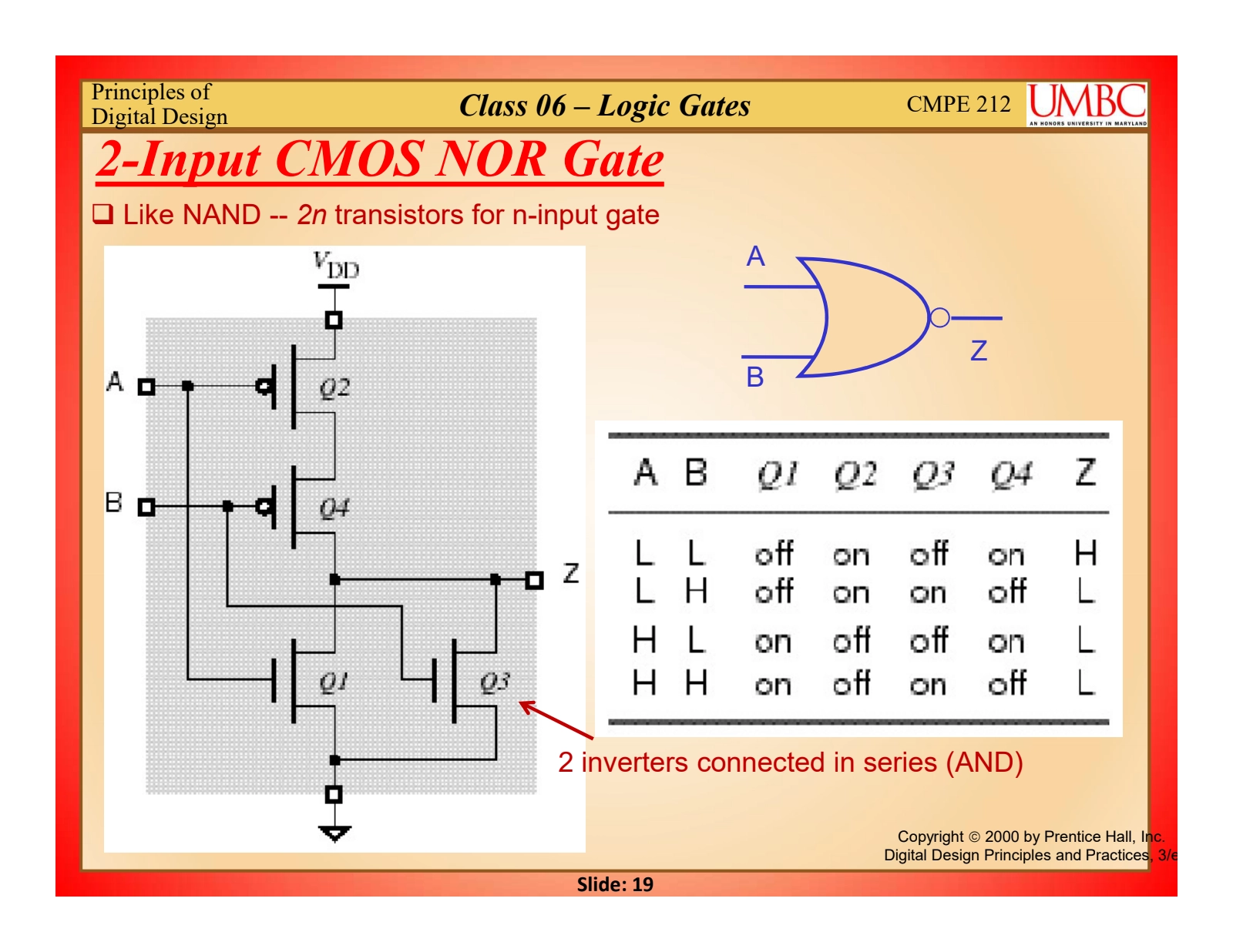

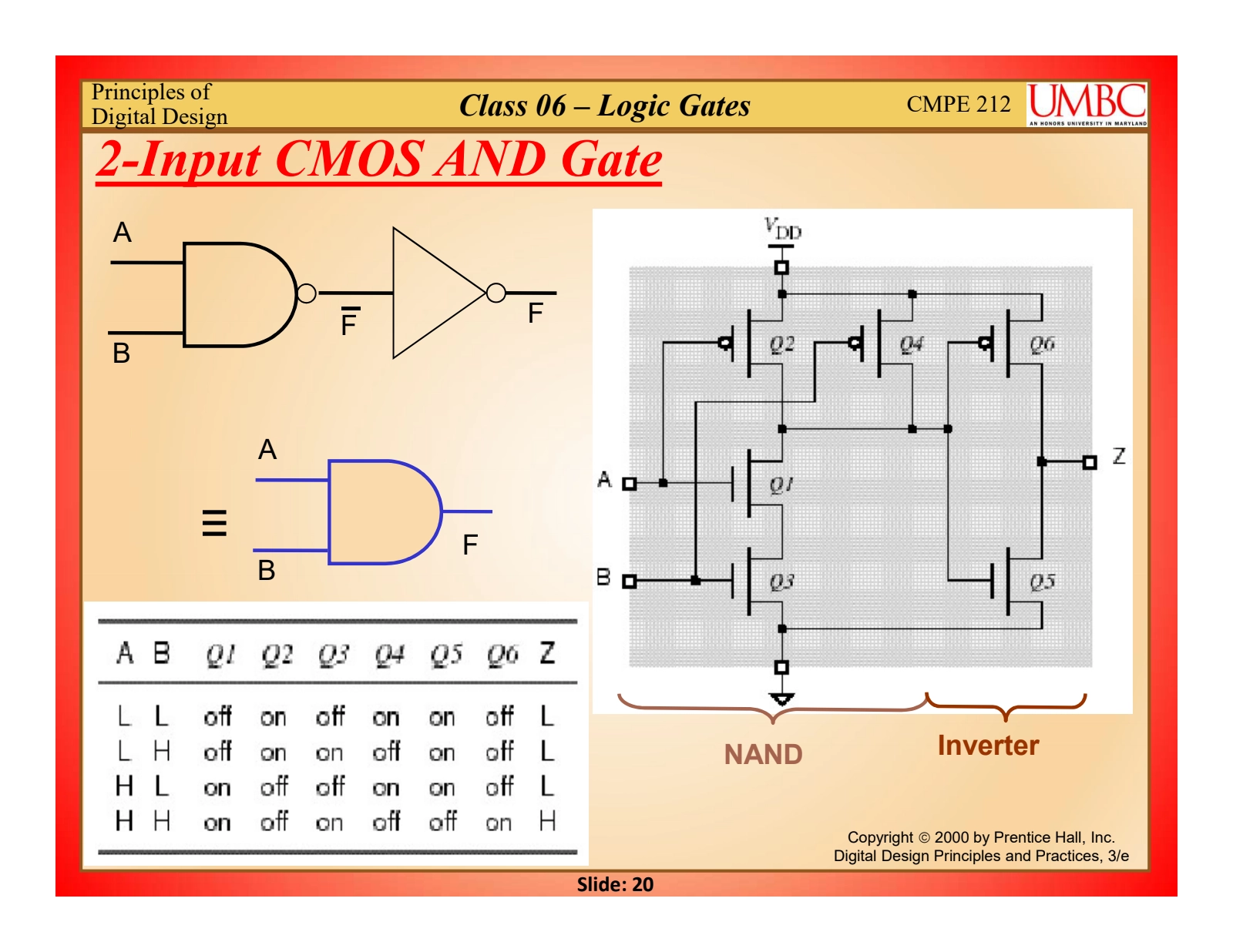

Class: 6, slide: 14,17-20 → Draw and explain operation of Gates

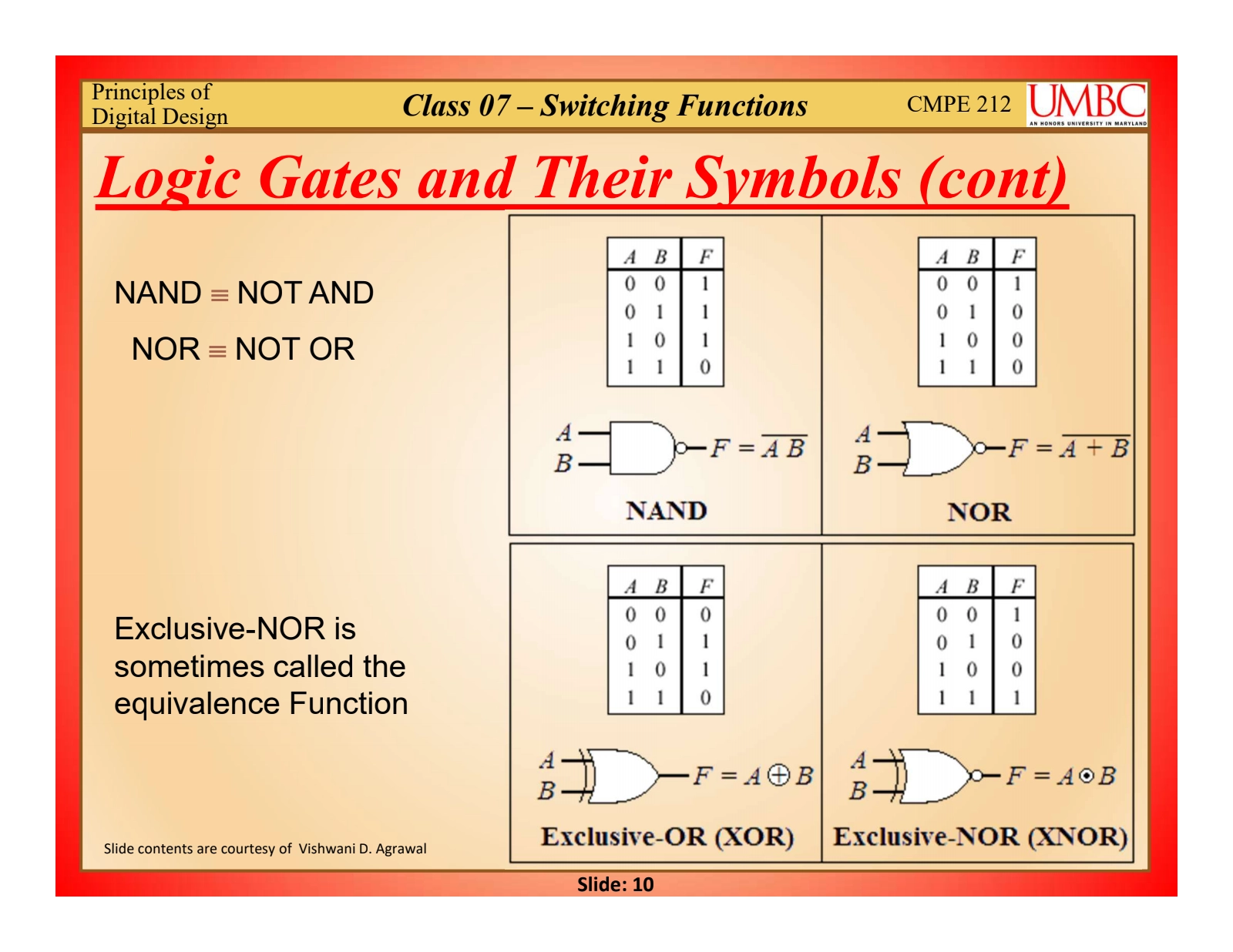

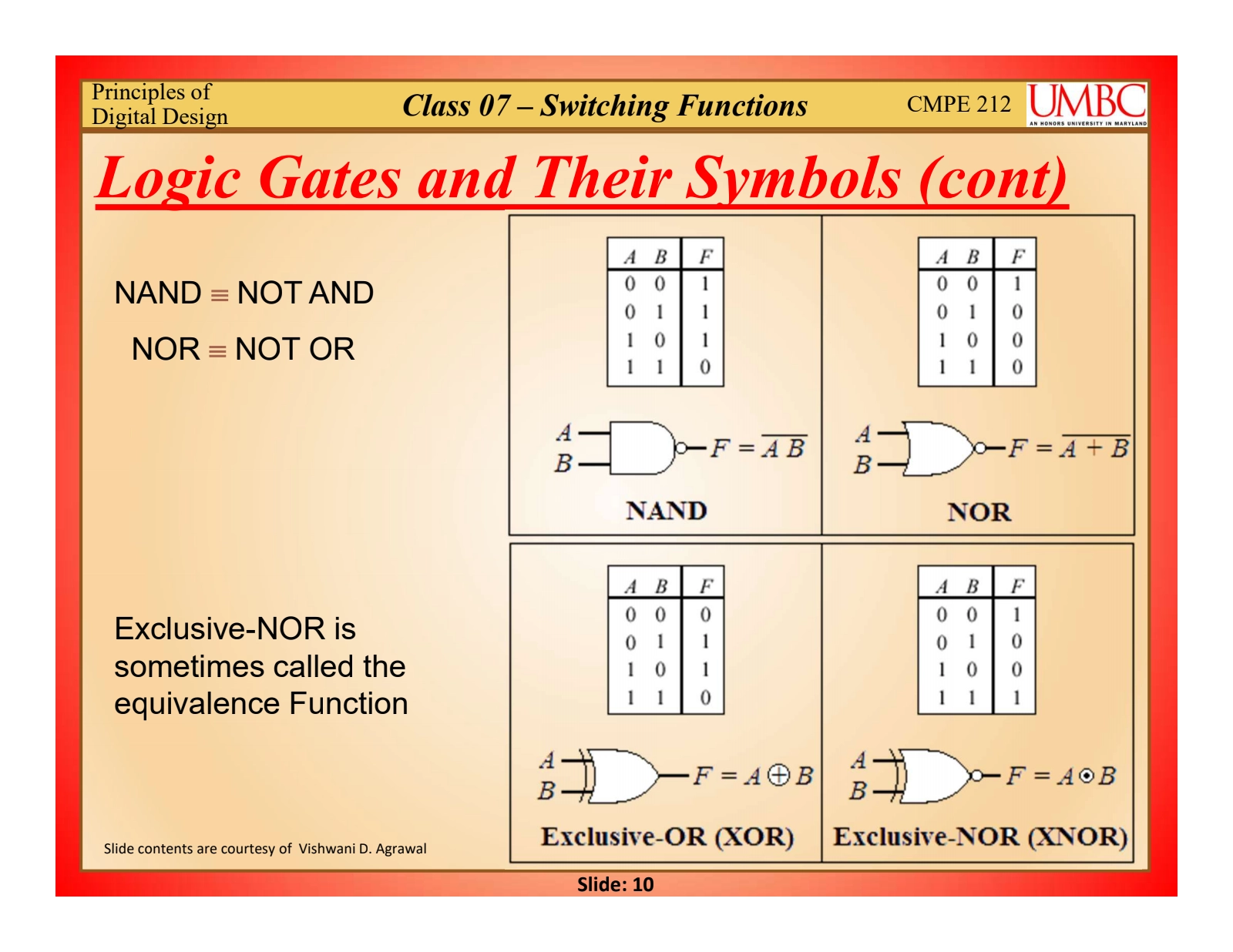

Class: 7, slide: 10 → NAND, NOR, XOR, XNOR Truth Tables

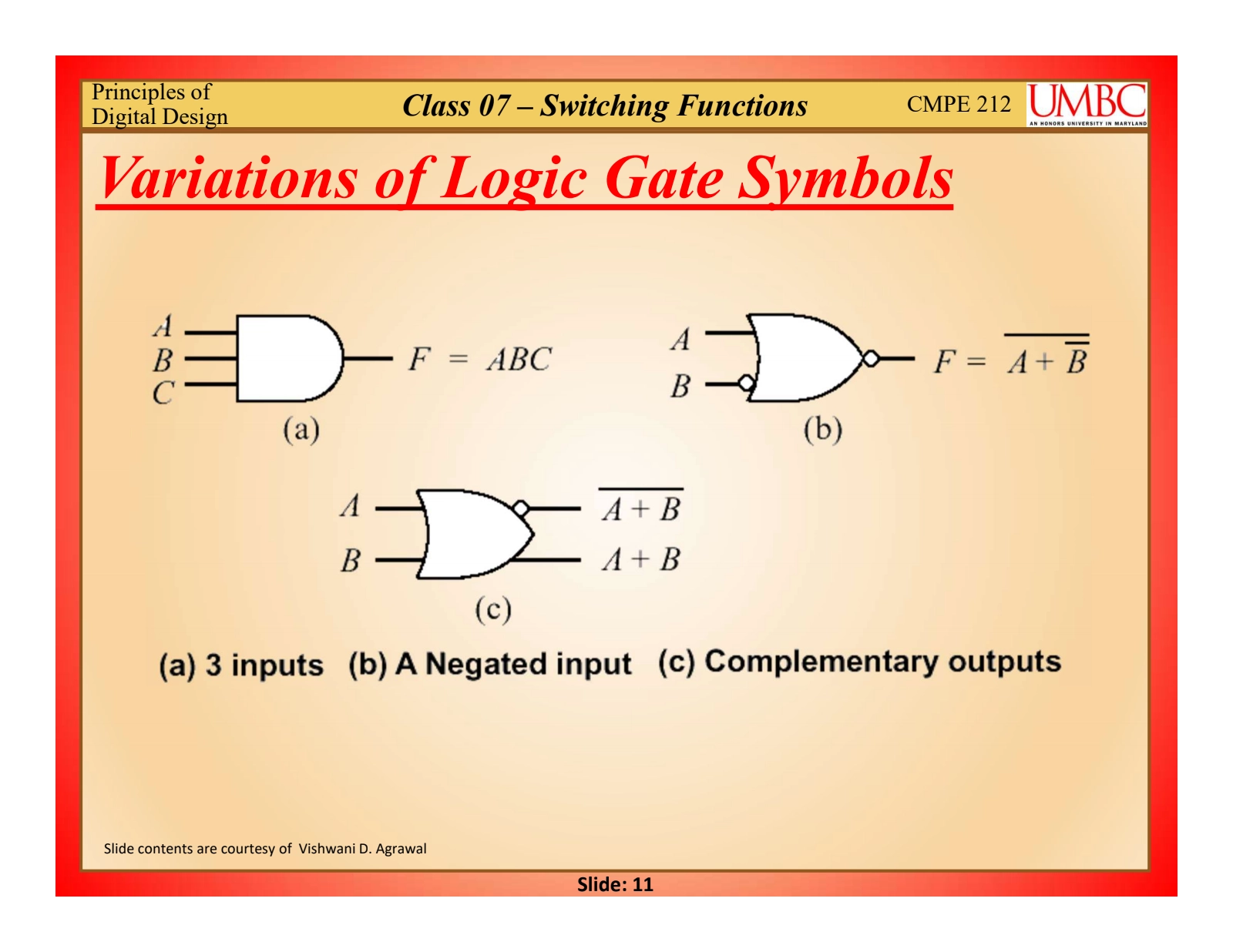

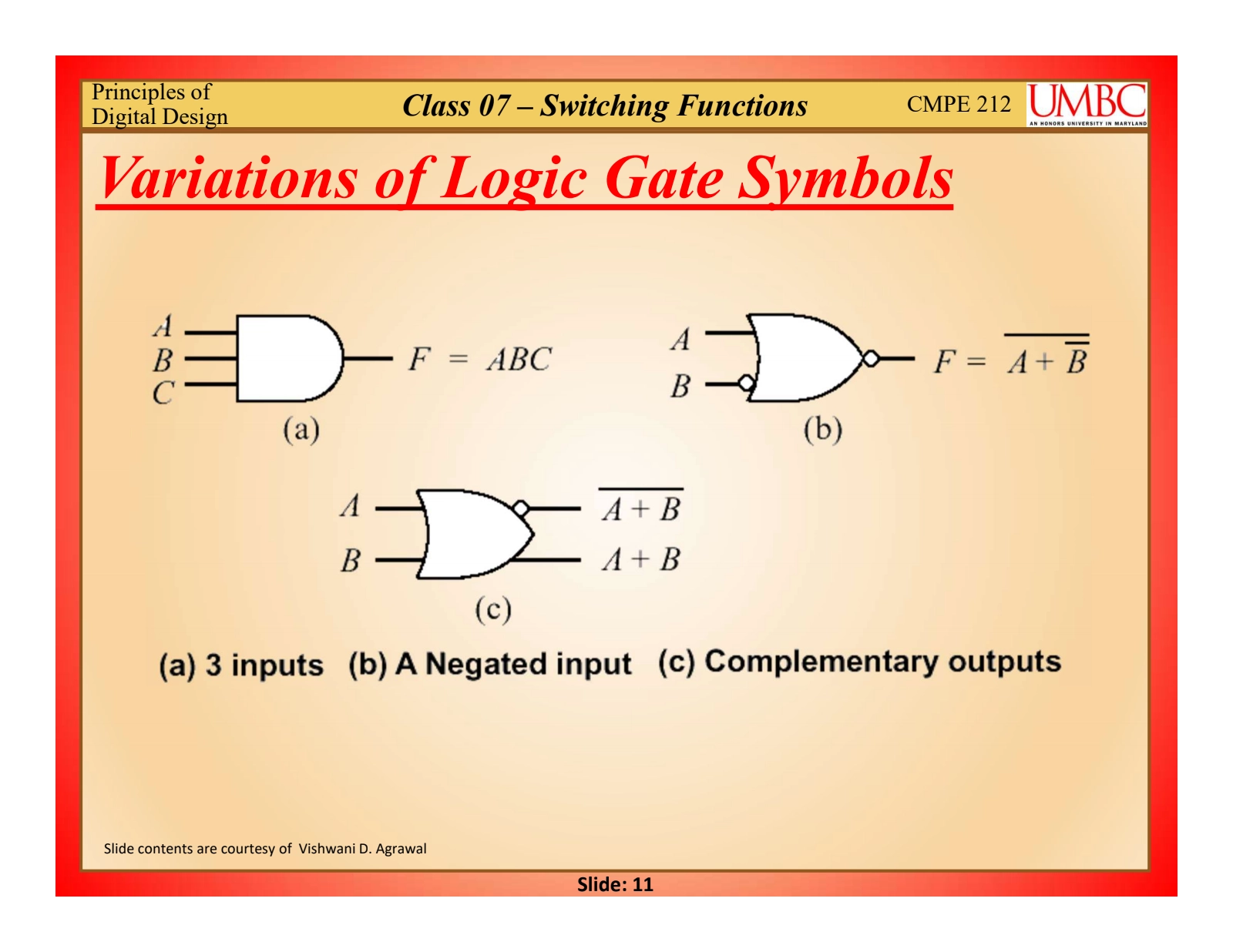

Class: 7, slide: 11 → Variants of Logic Symbols

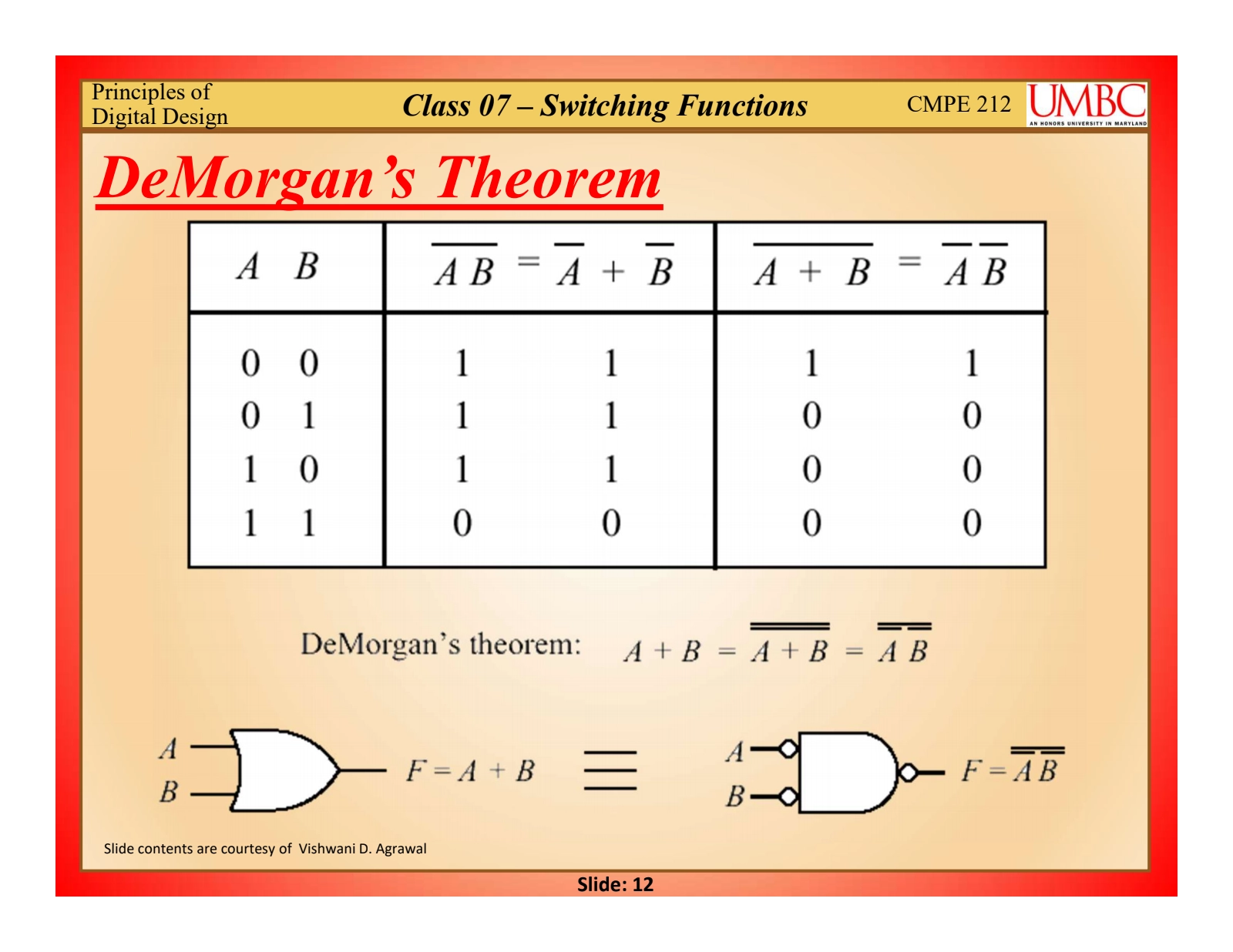

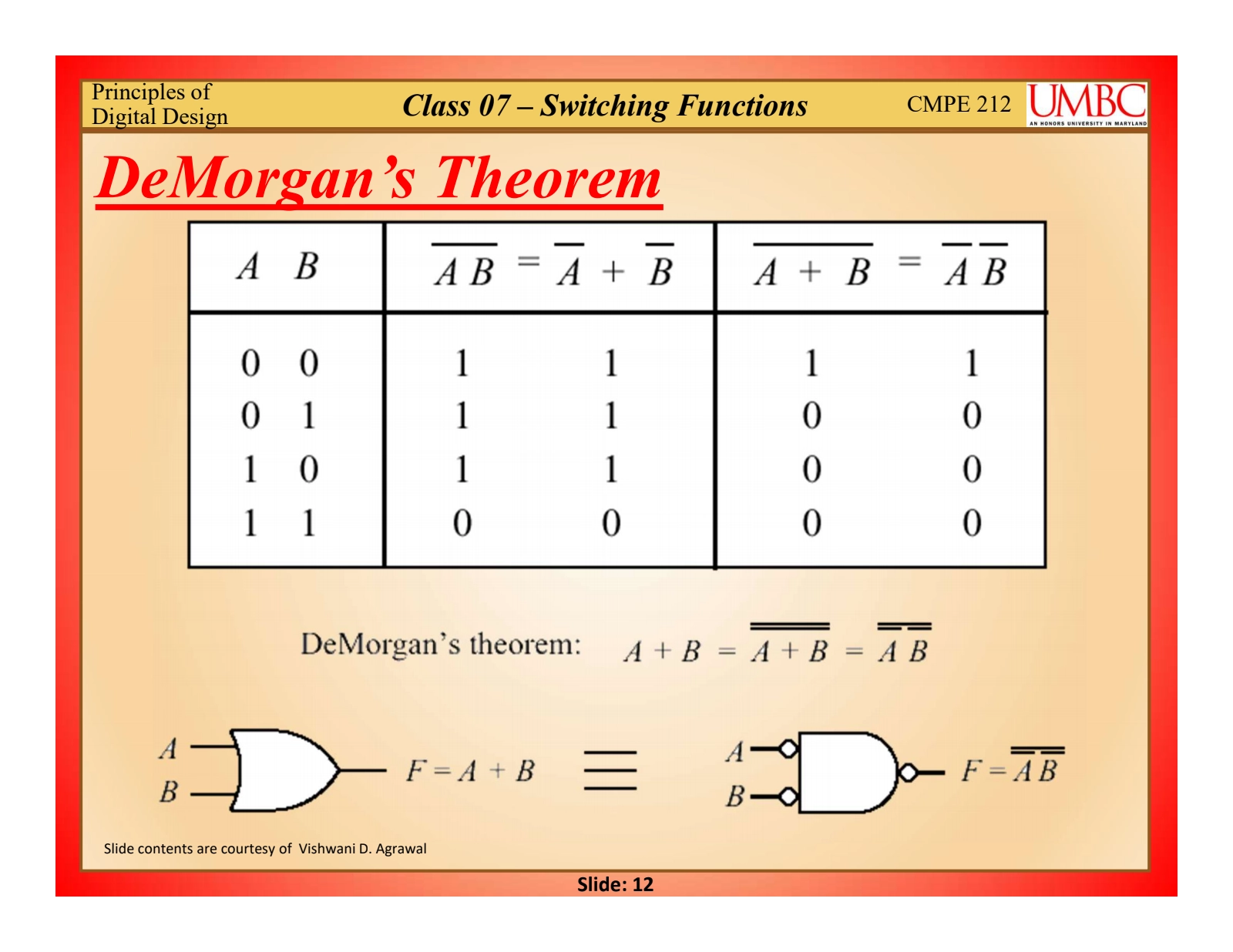

Class: 7, slide: 12 → Demorgan's Make an OR from an NAND gate

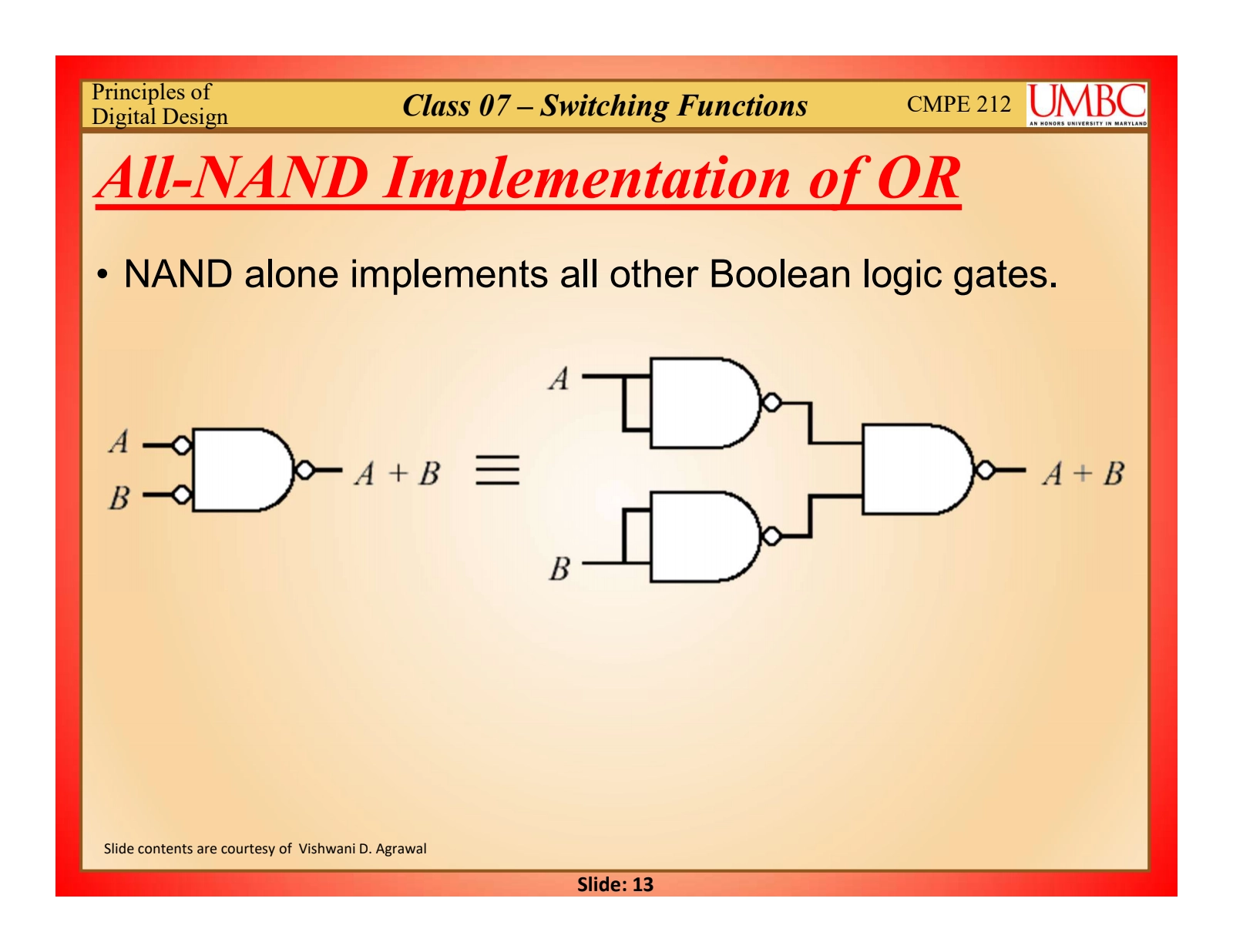

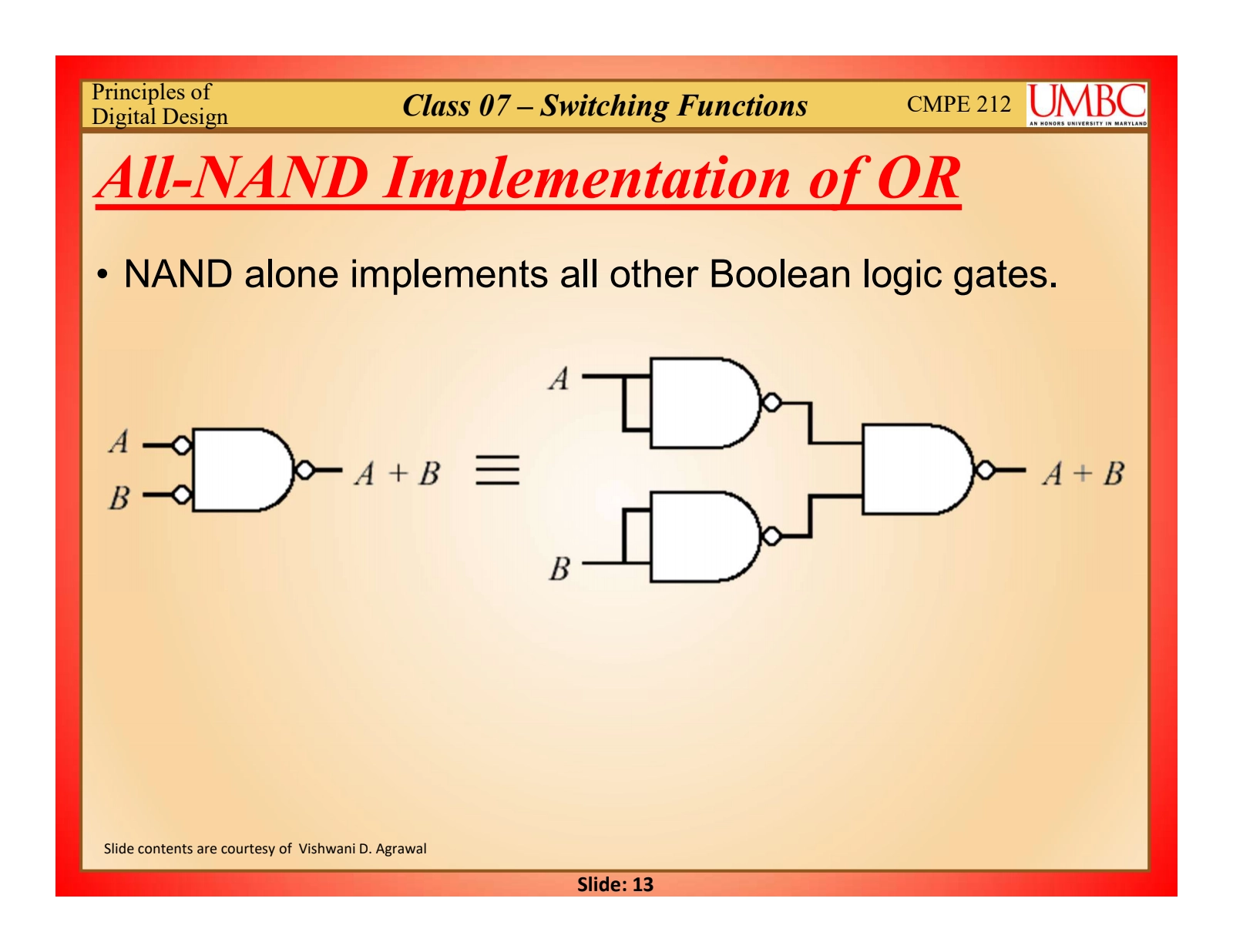

Class: 7, slide: 13 → Build a gate using just NANDs

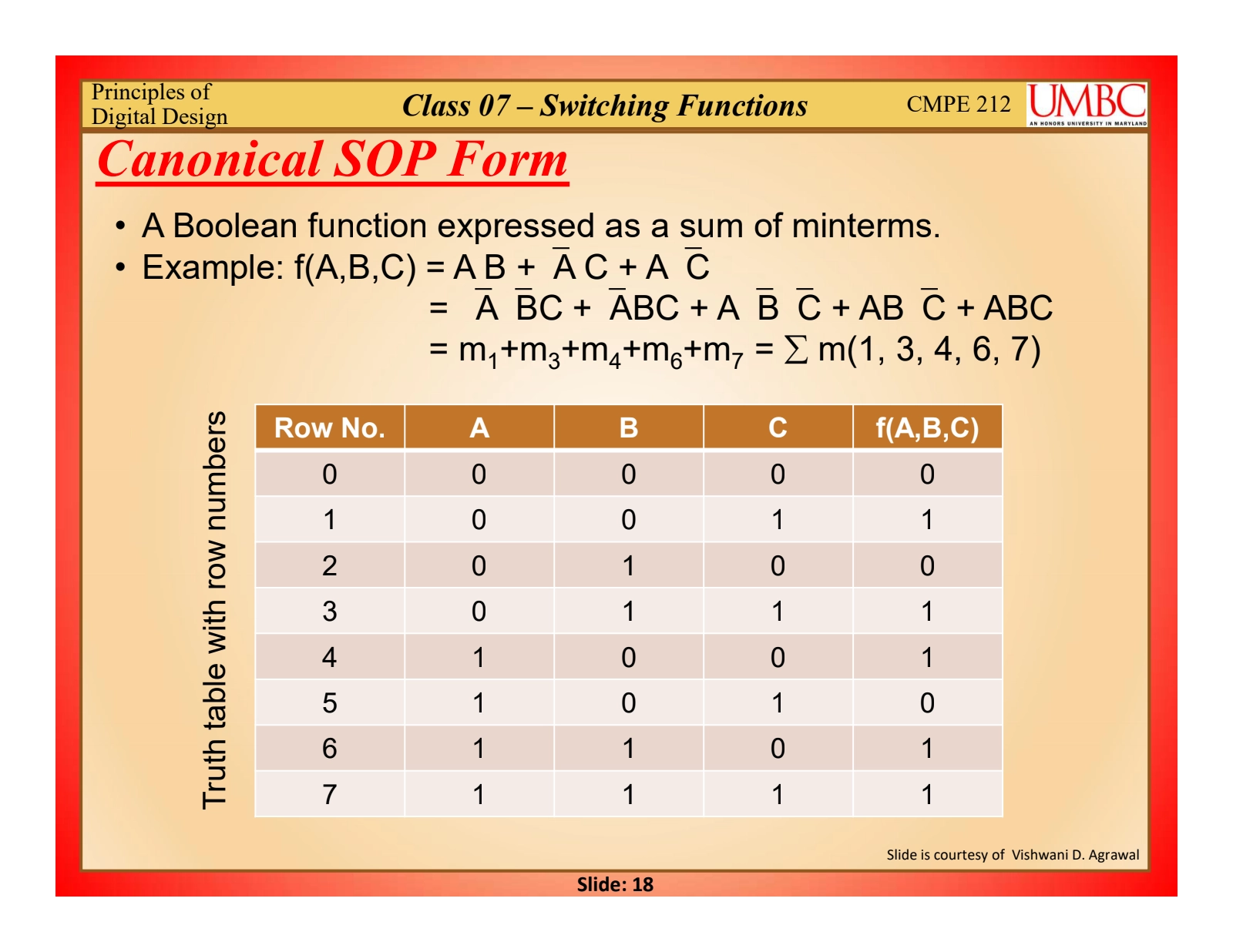

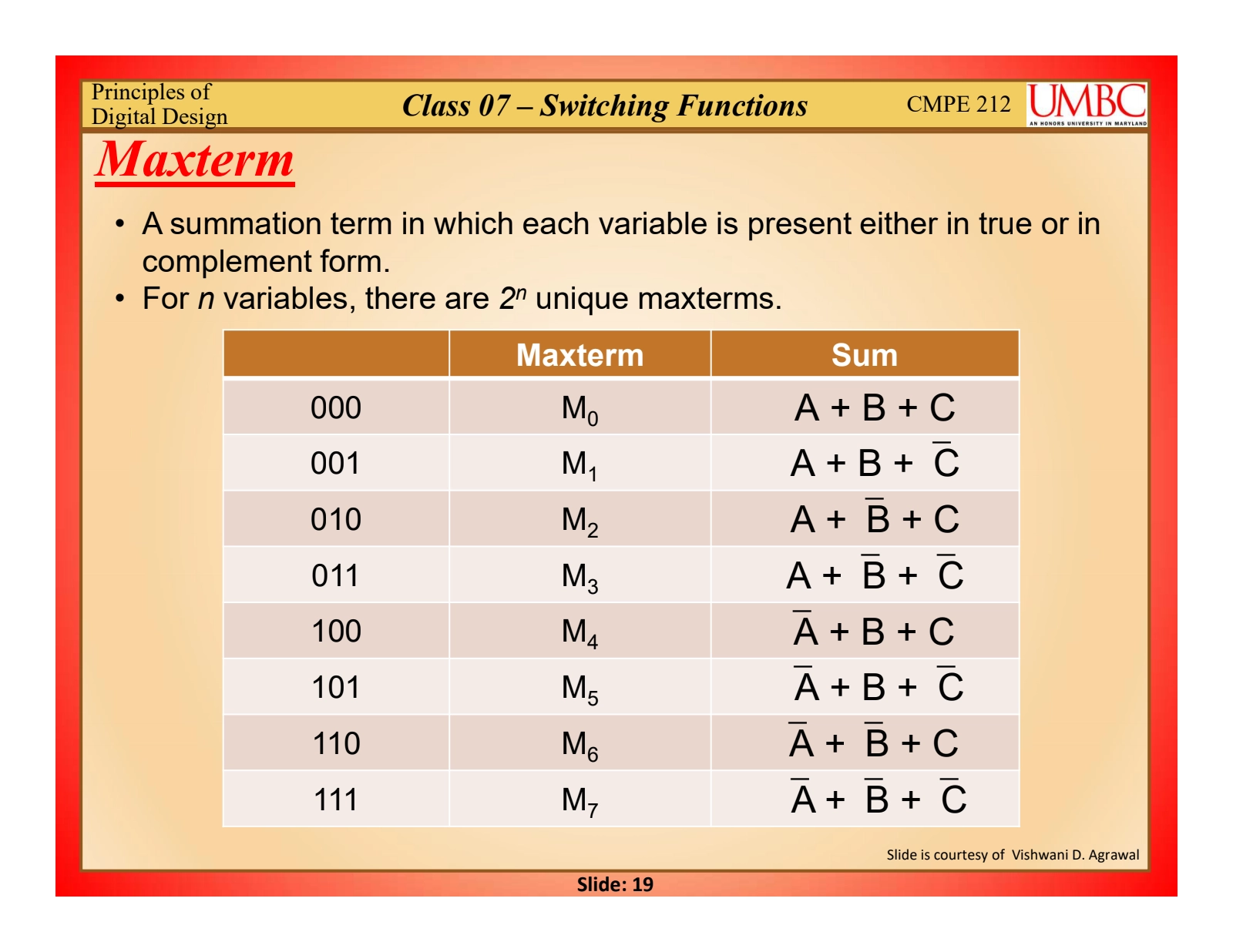

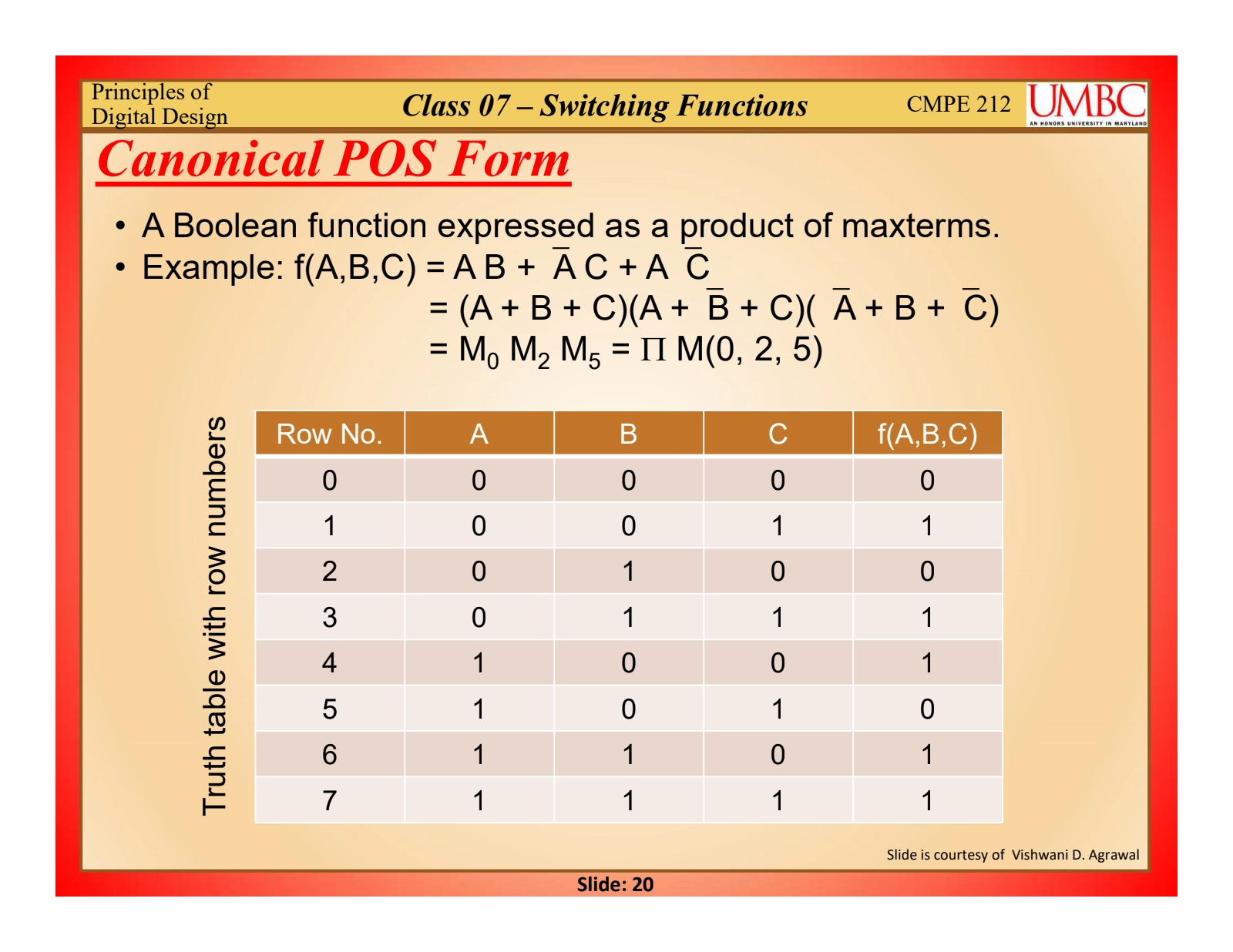

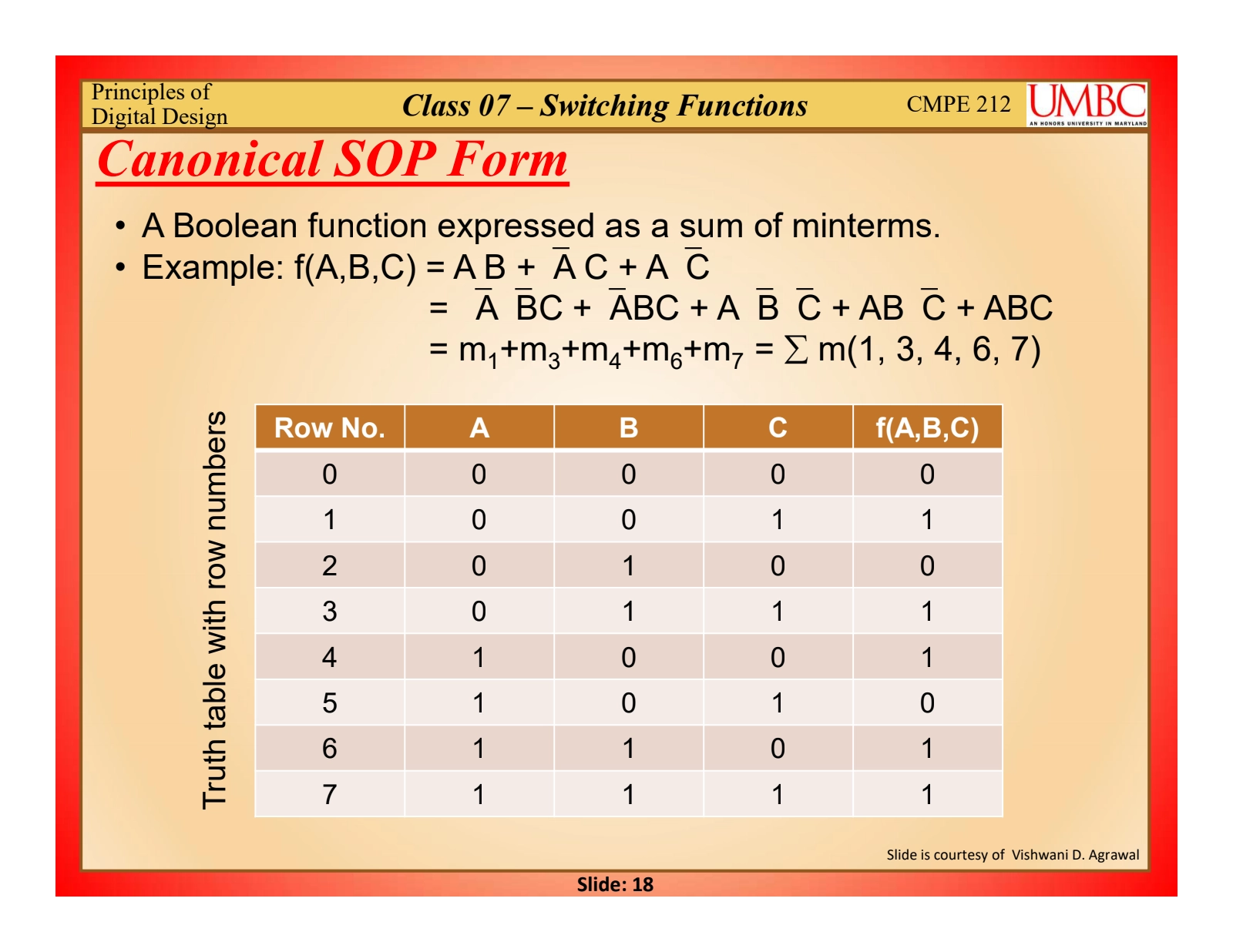

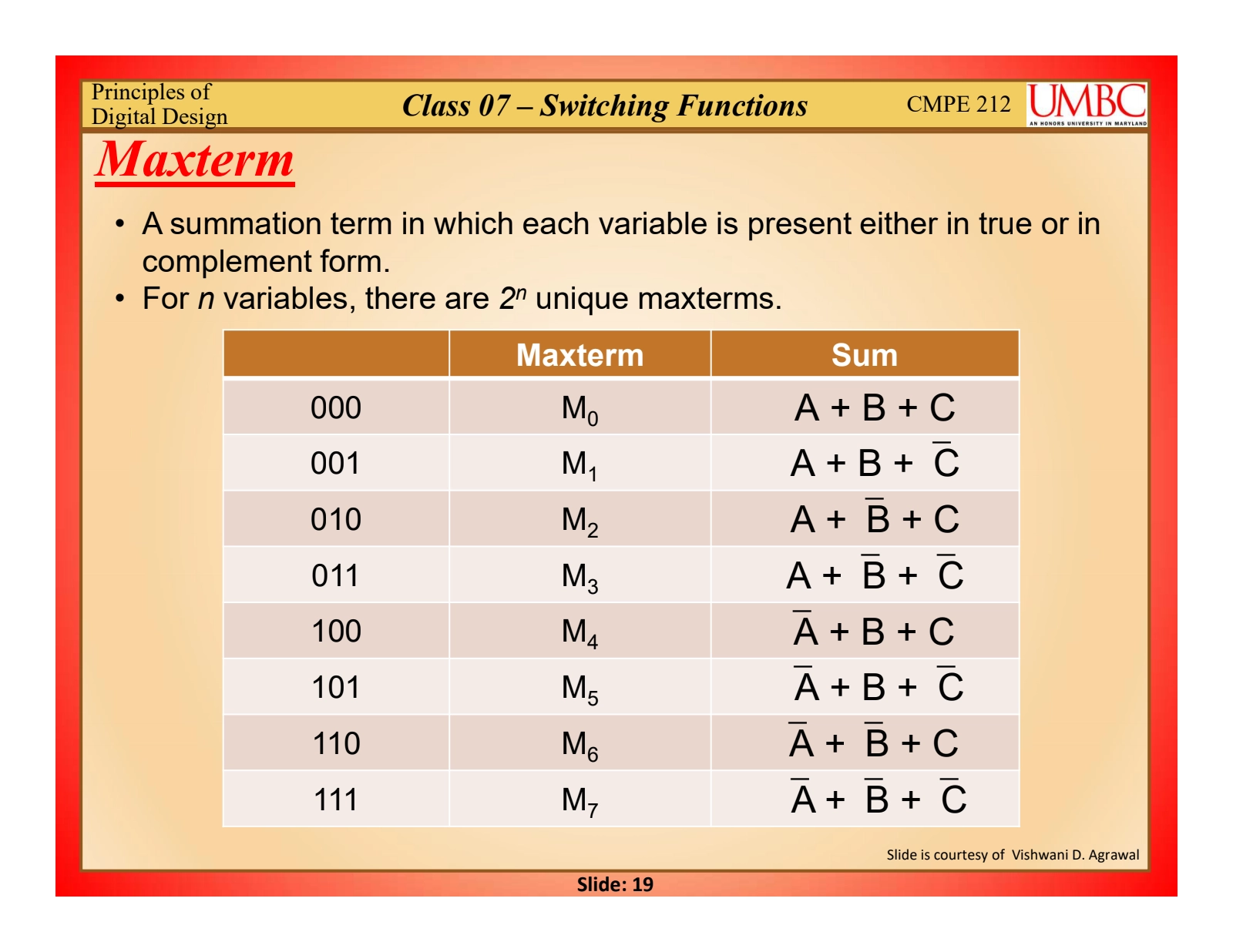

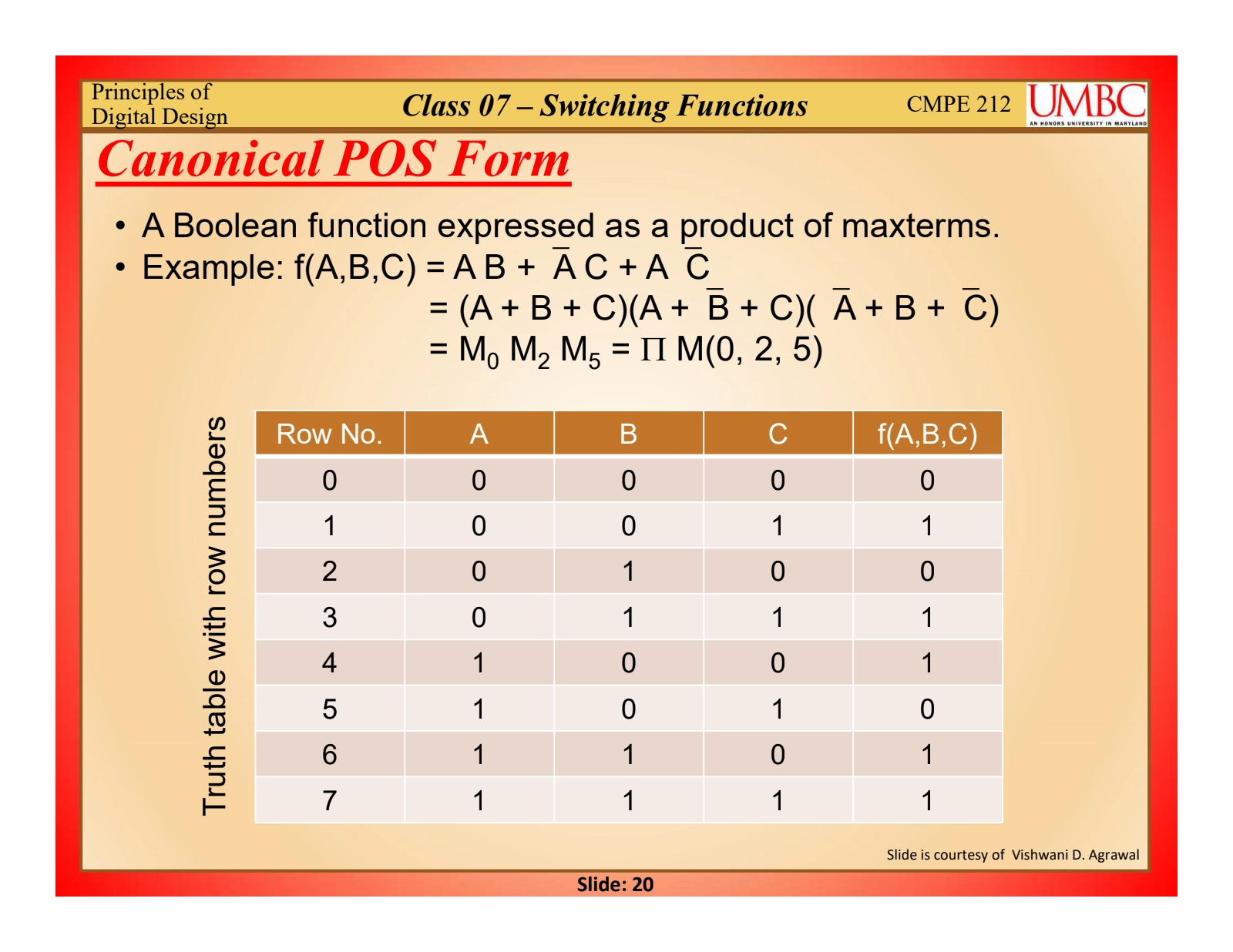

Class: 7, slide: 18-20 → Canonical SOP or POS from Truth Tables

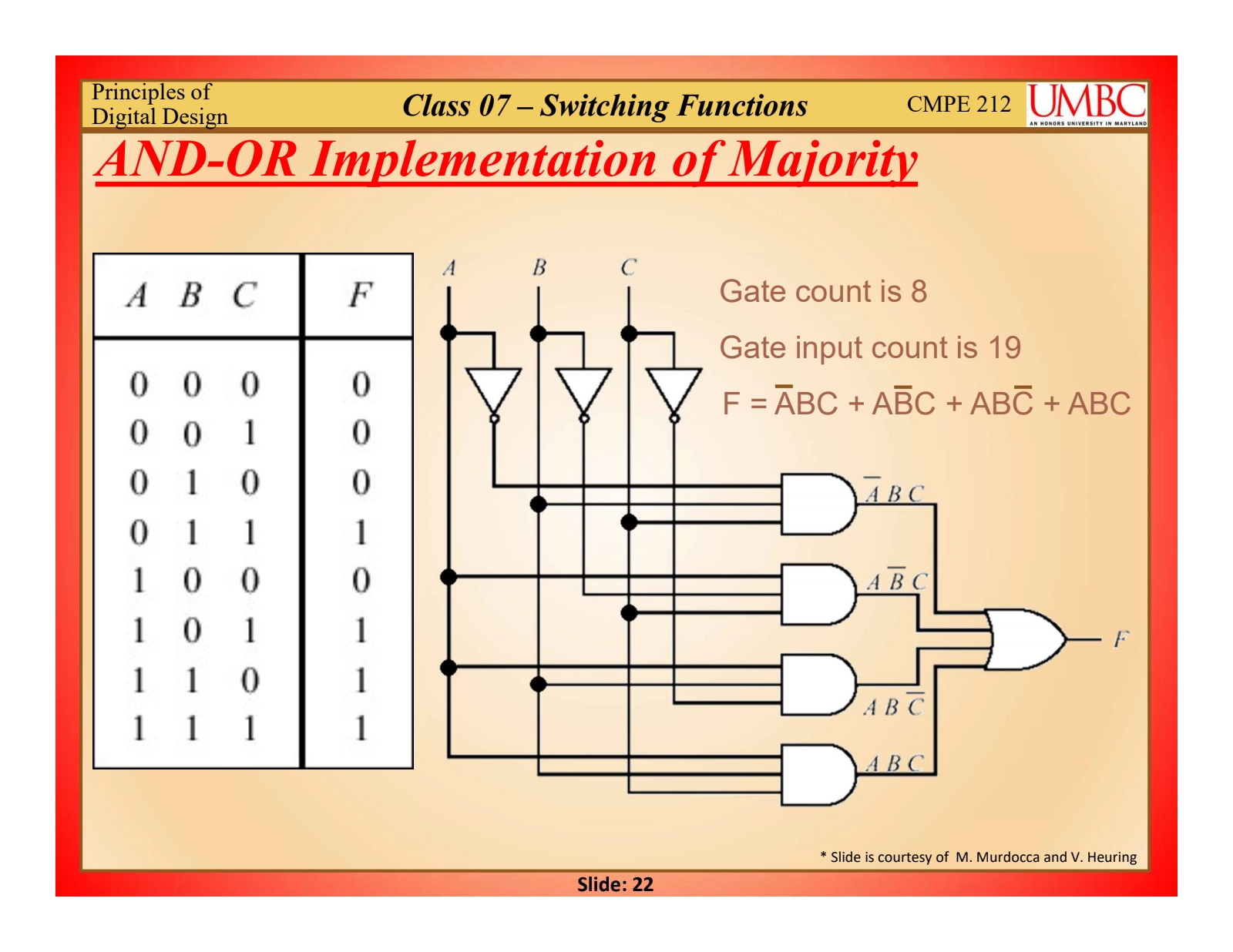

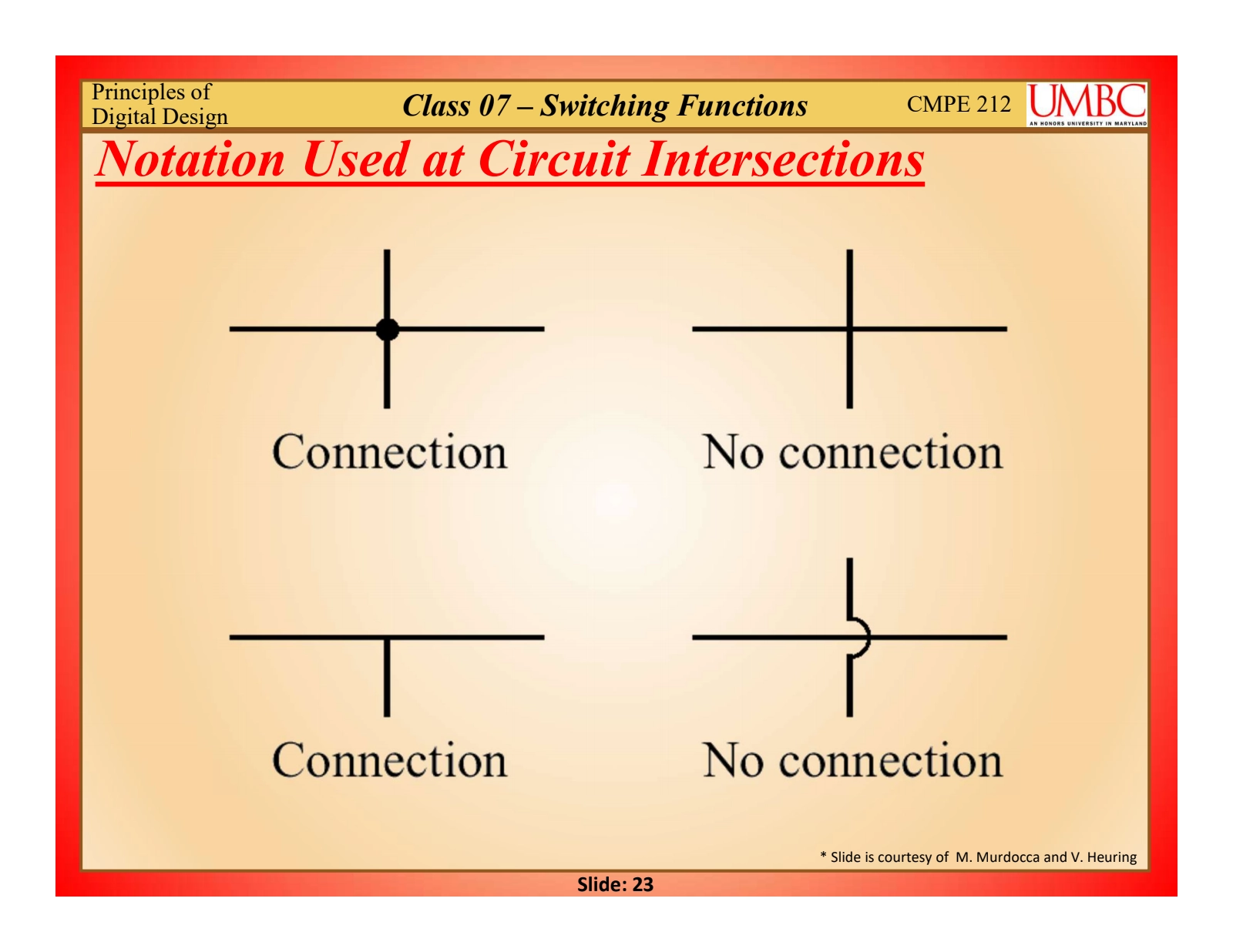

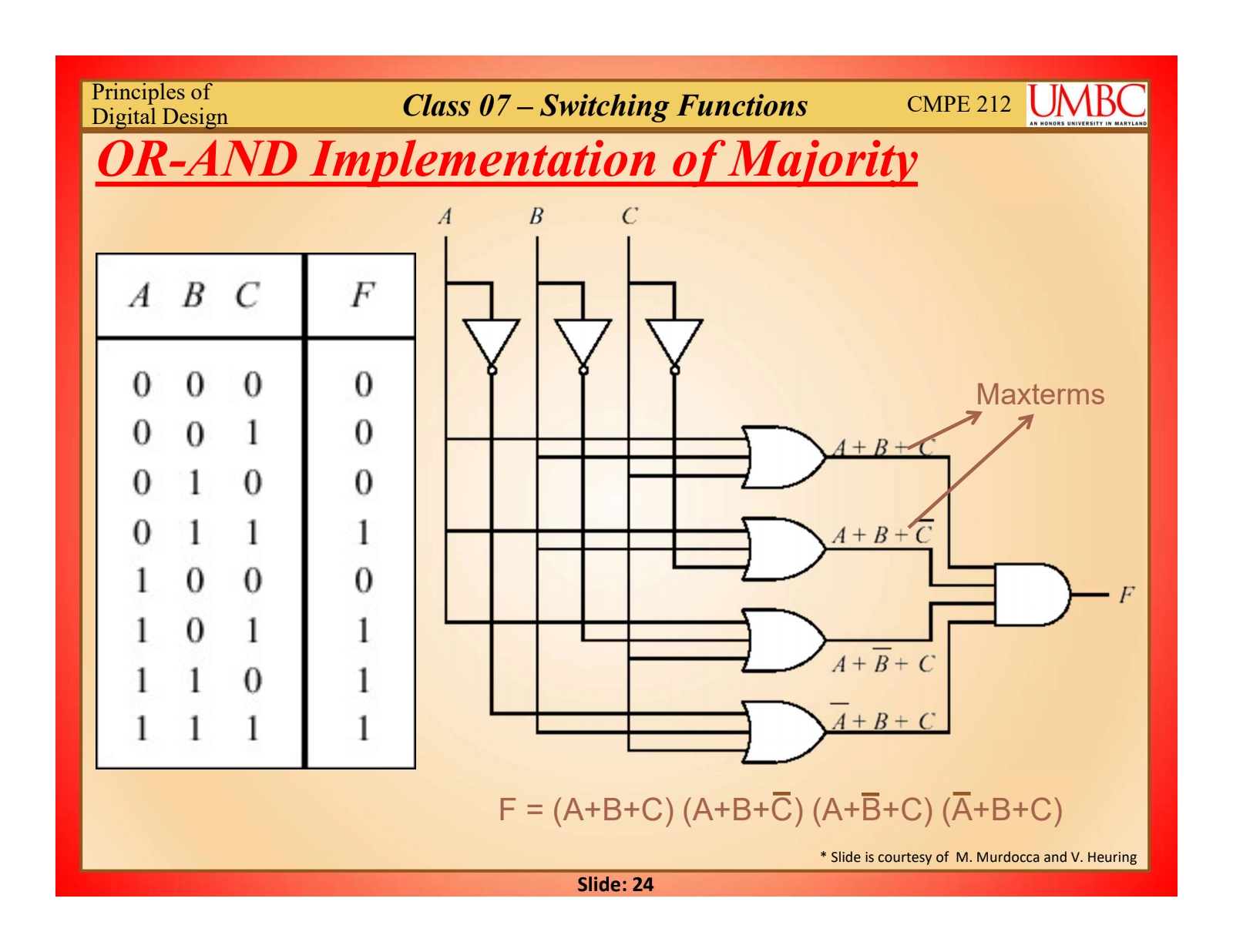

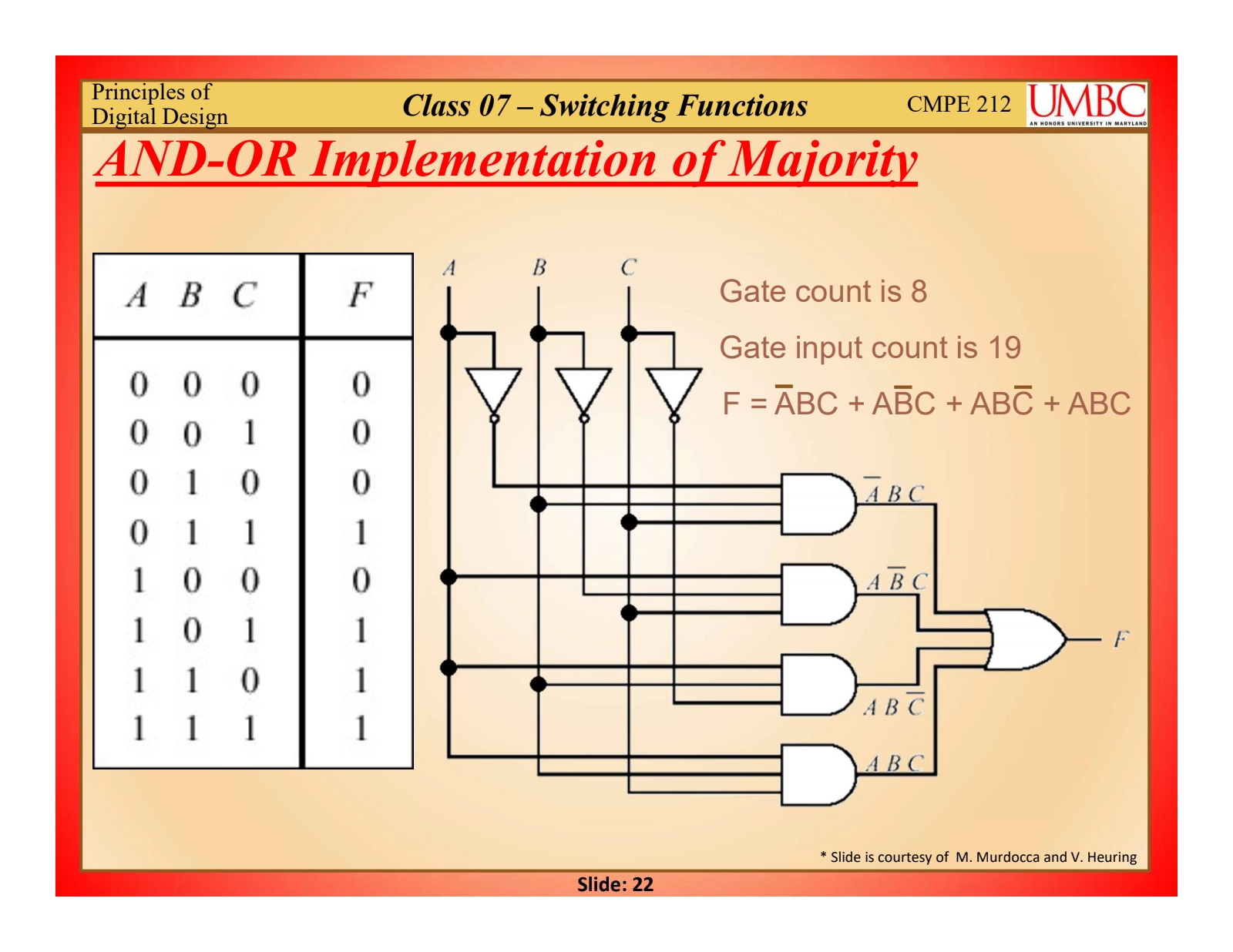

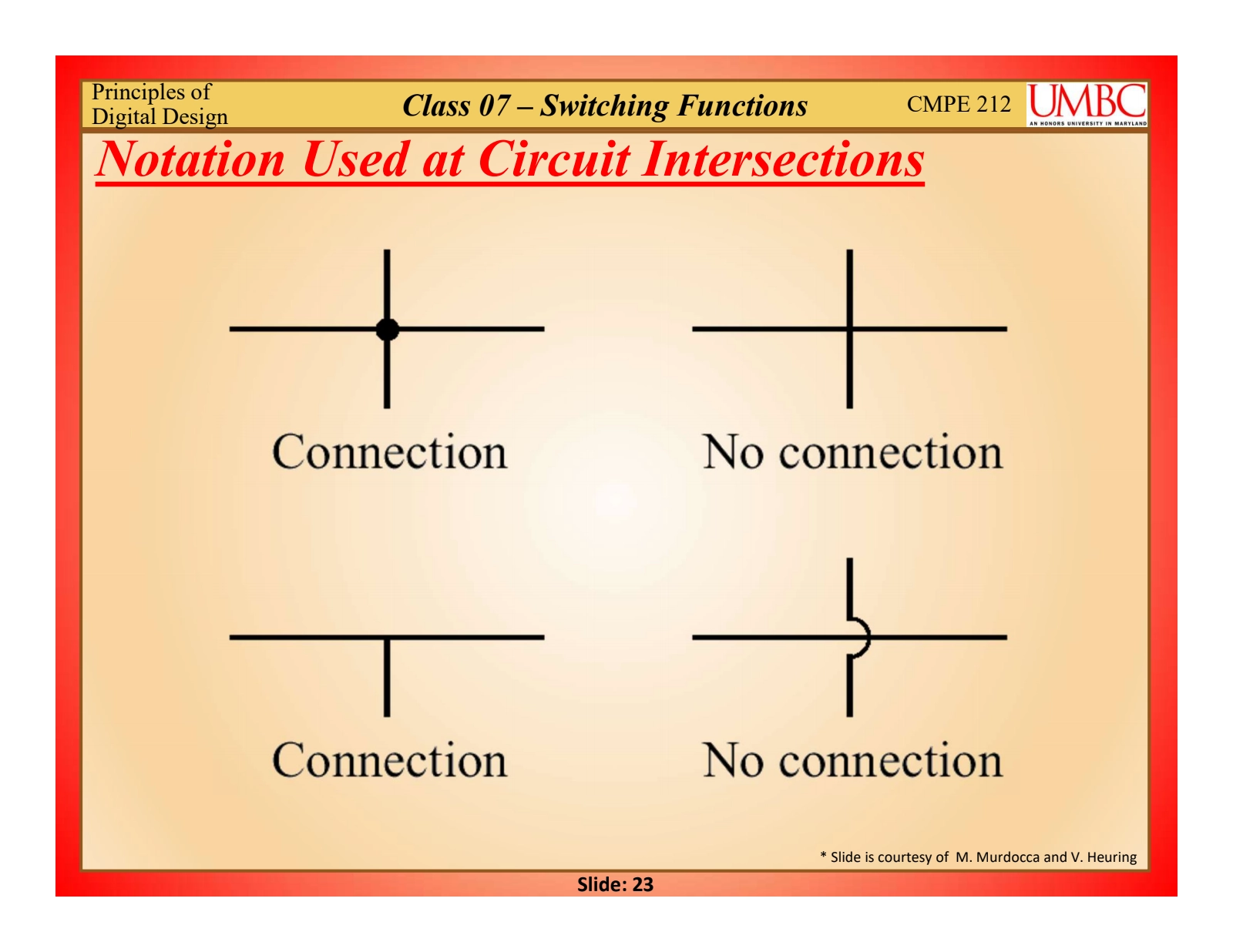

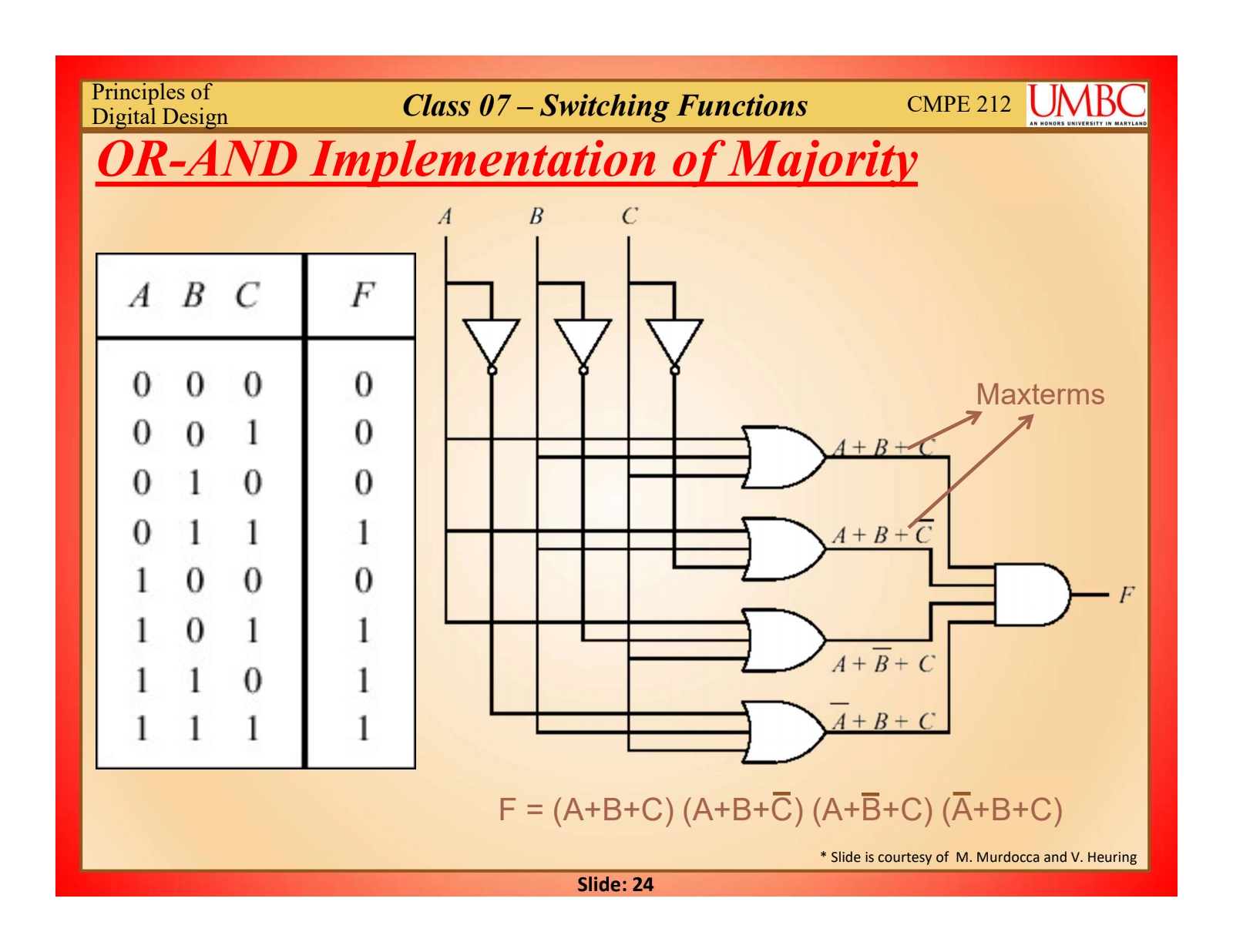

Class: 7, slide: 22-24 → OR-AND, AND-OR Implementation(s)

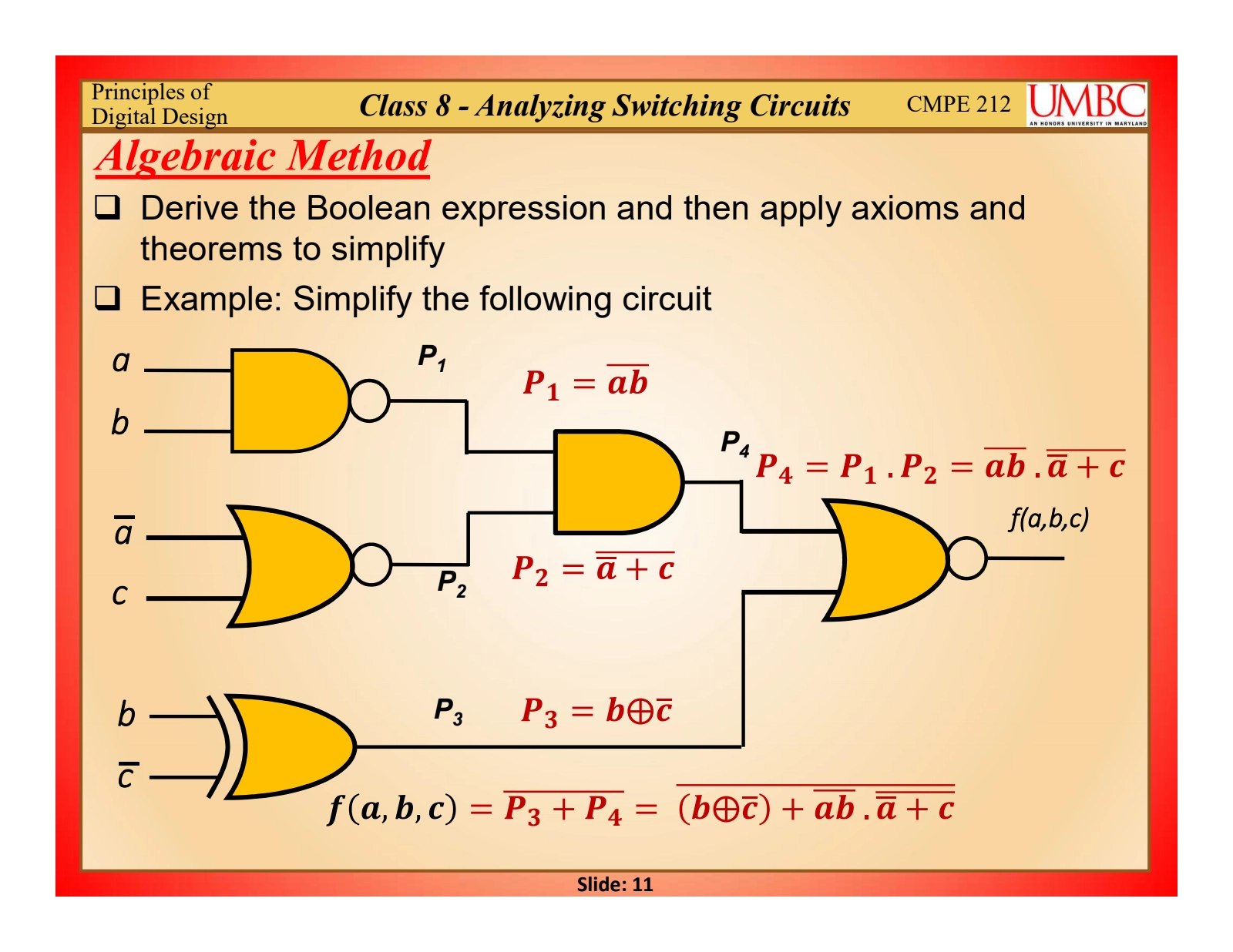

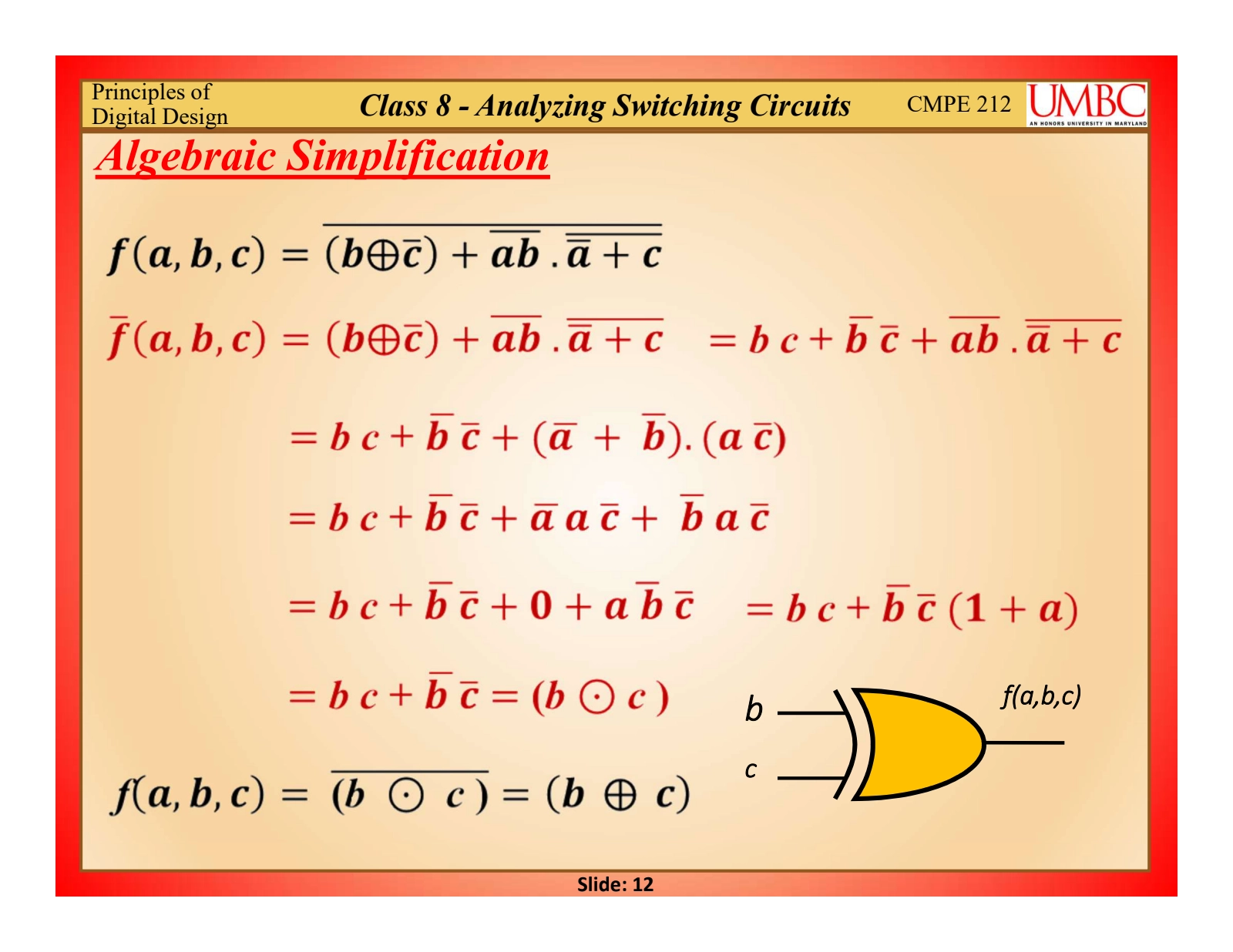

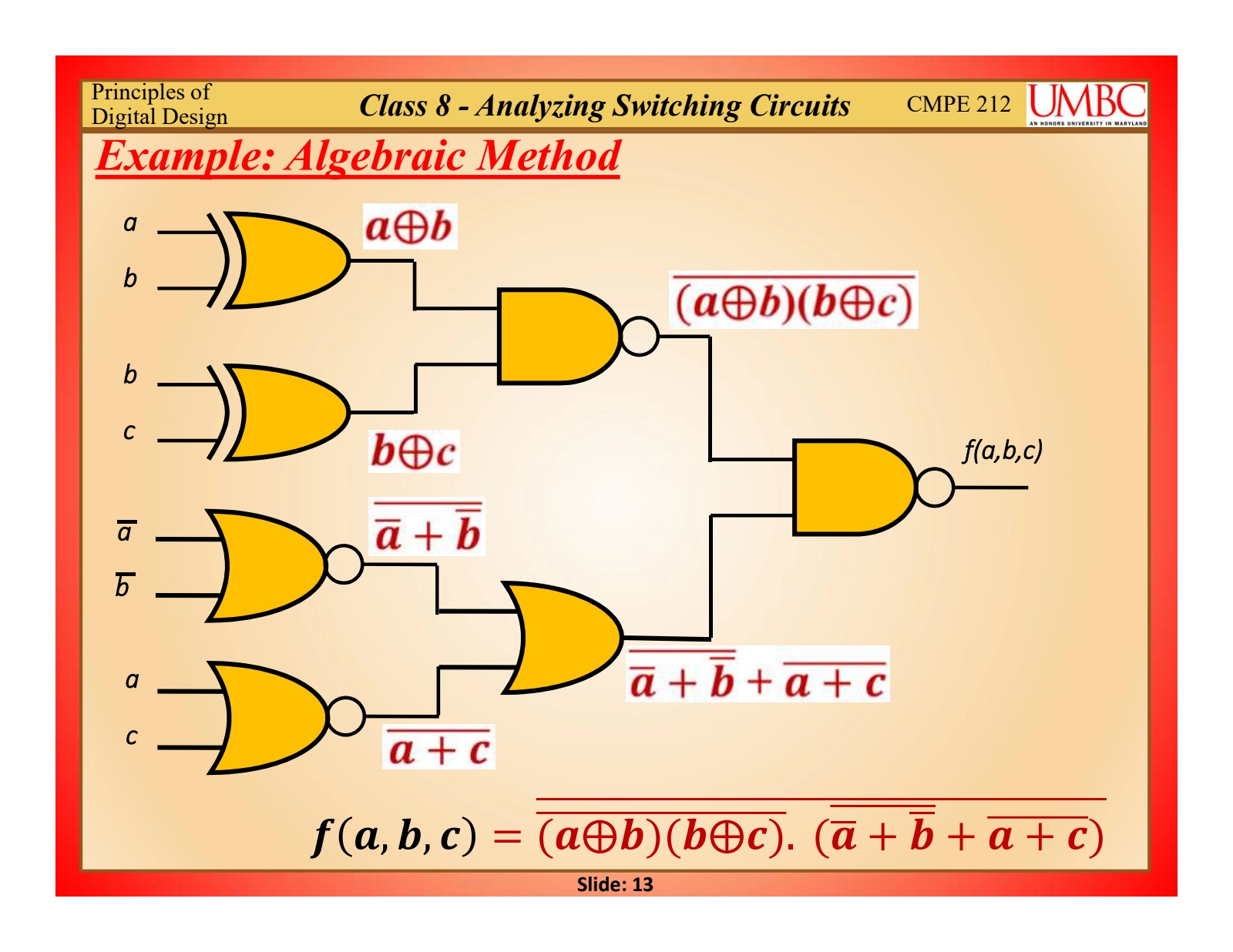

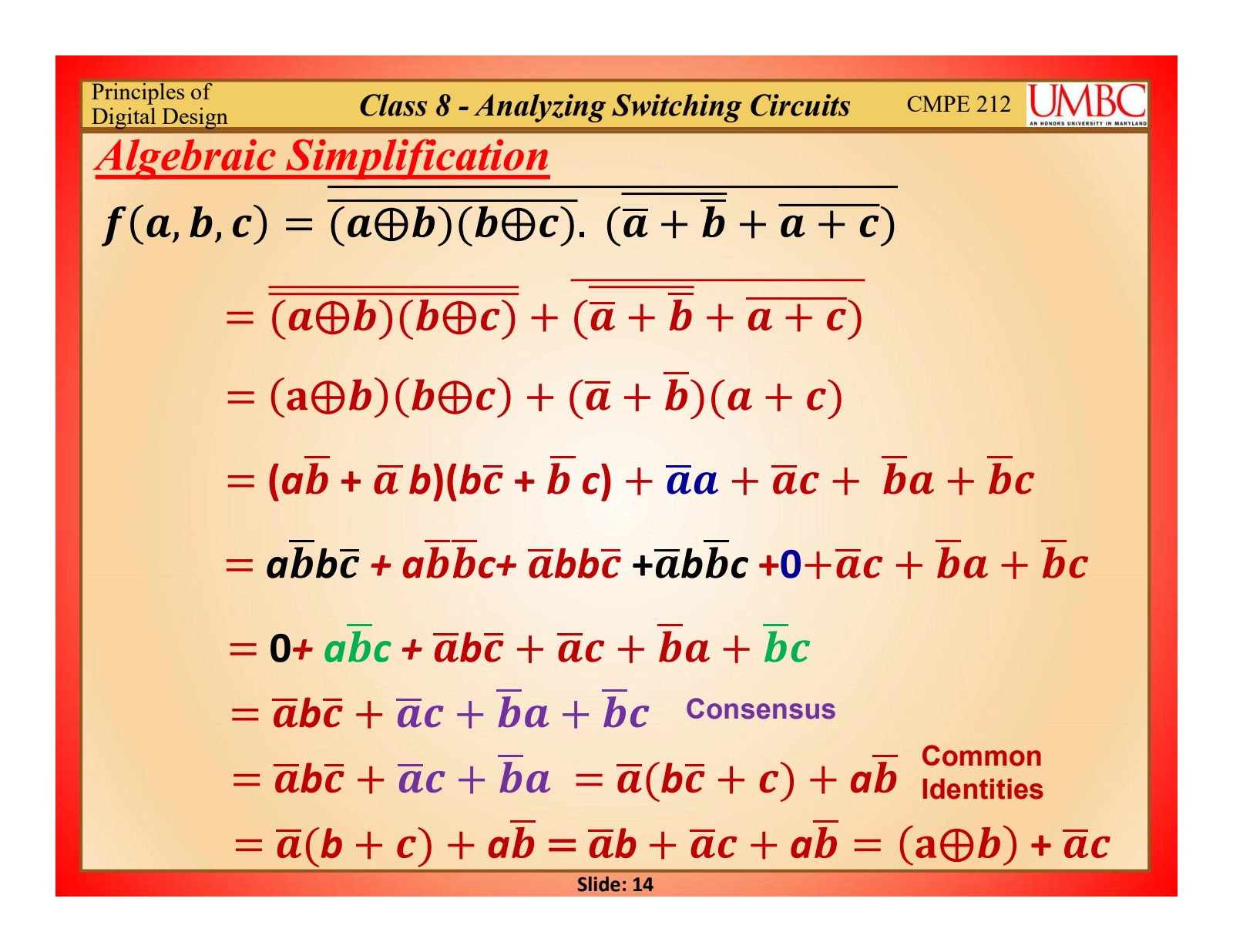

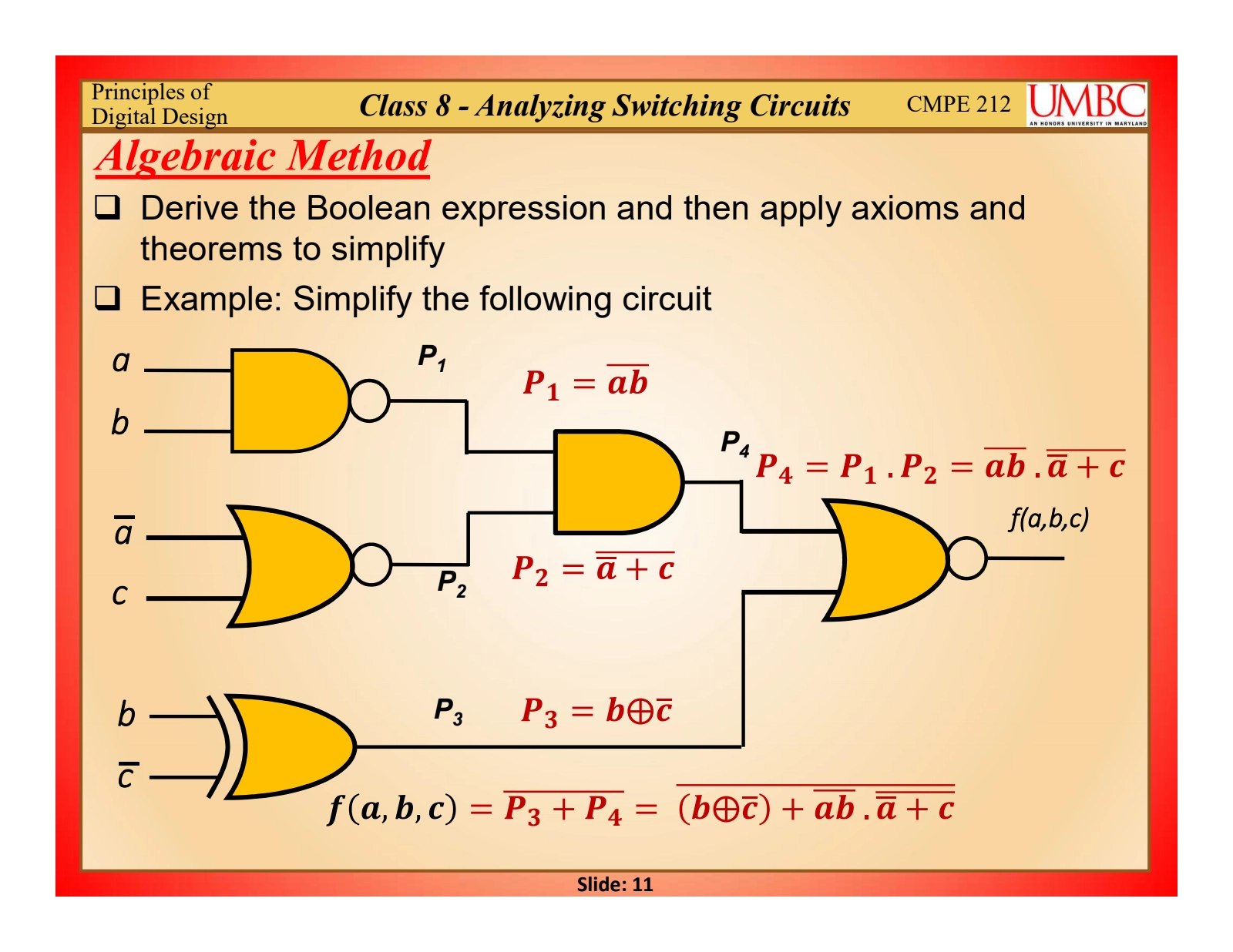

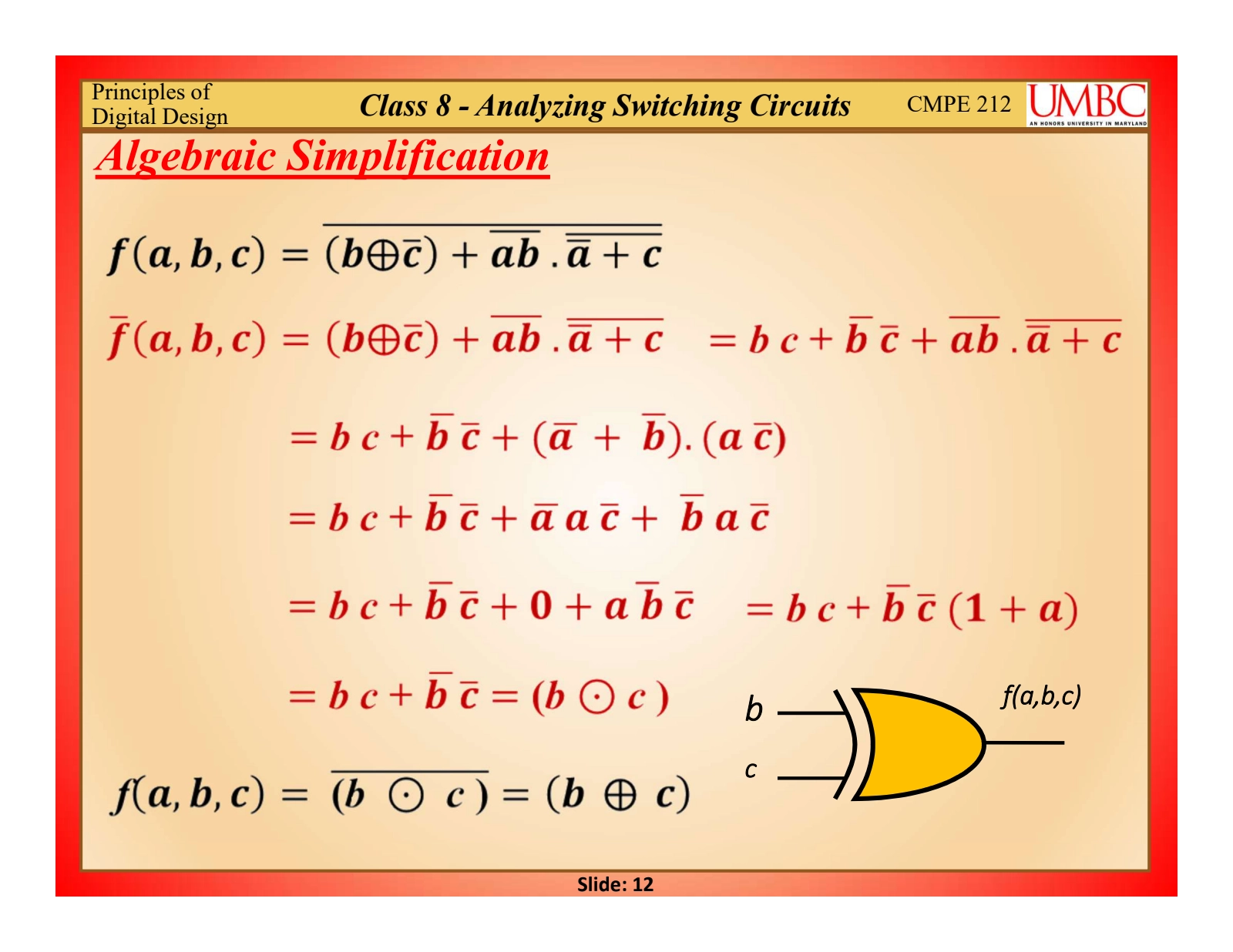

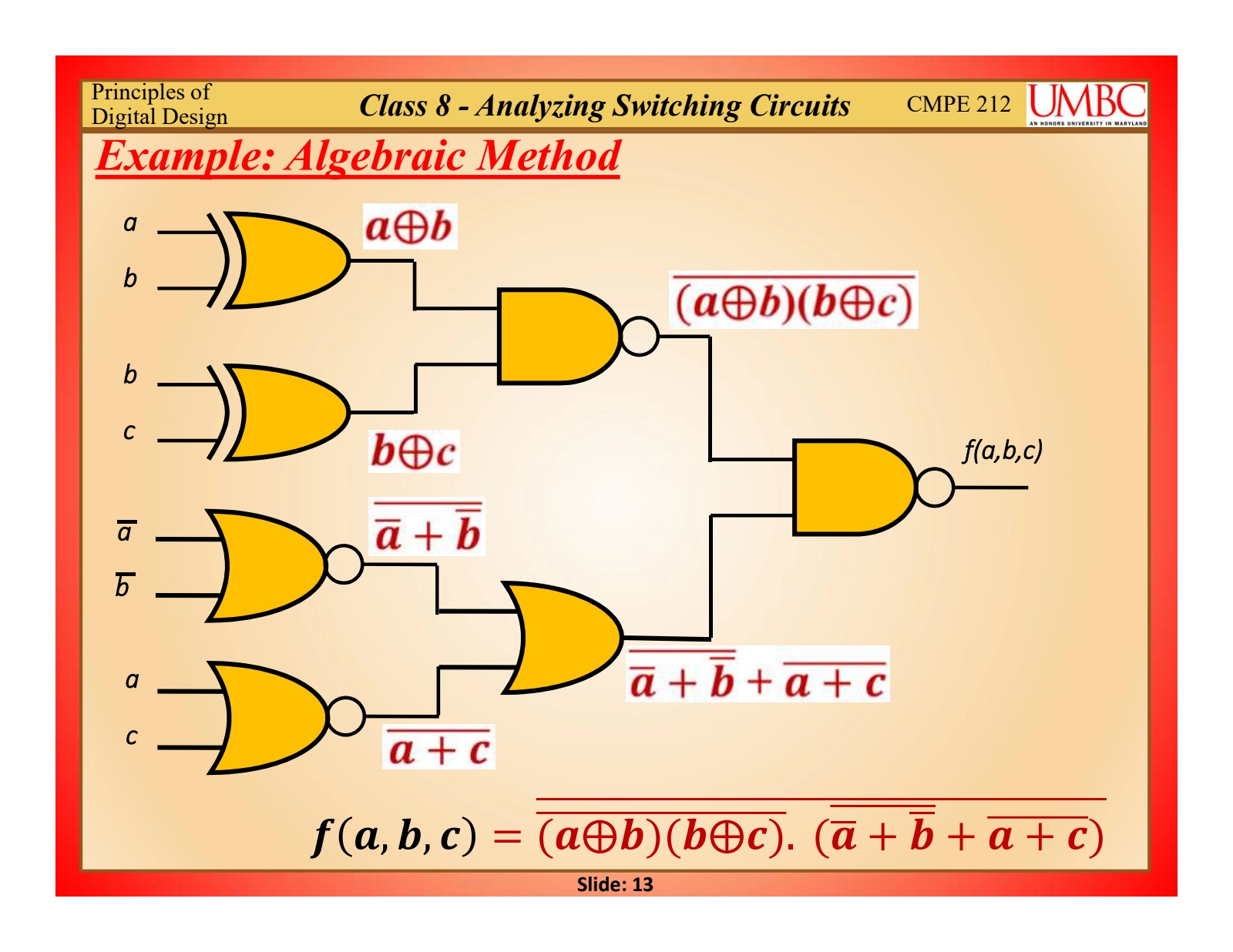

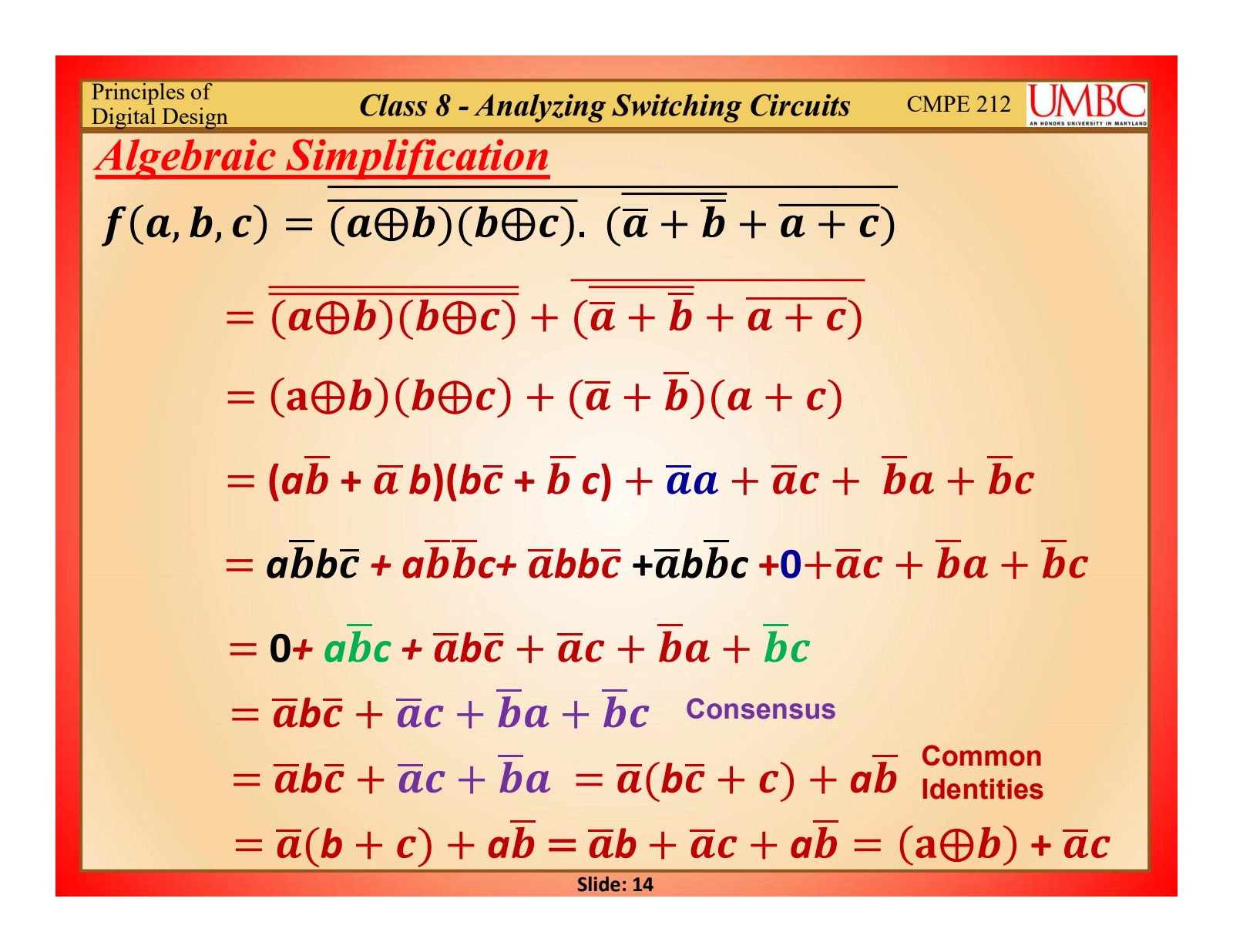

Class: 8, slide: 11-14 → Simplify a circuit w/ Boolean Algebra

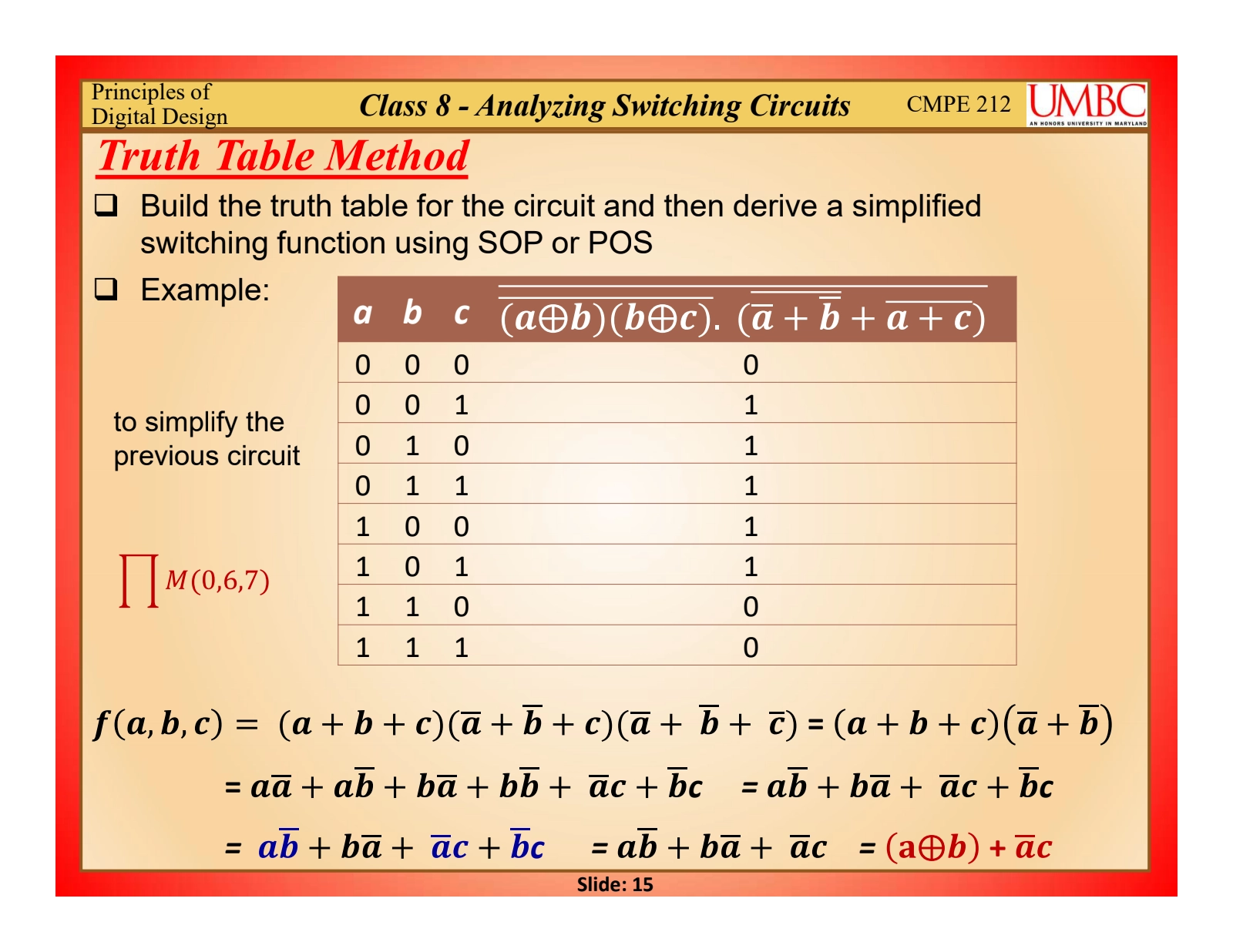

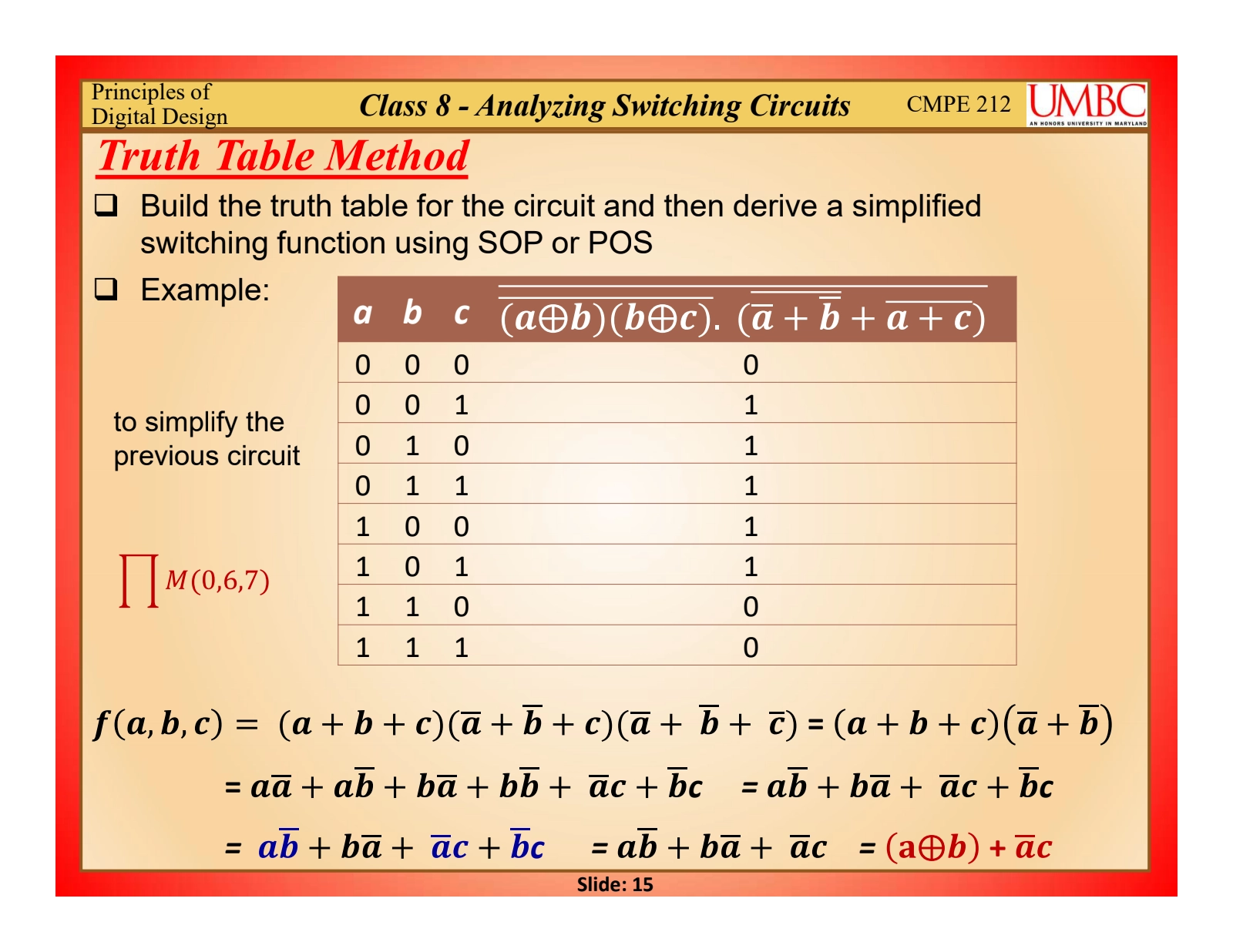

Class: 8, slide: 15 → Construct a circuit from a Truth Table

Additional Materials to Review for The Midterm:

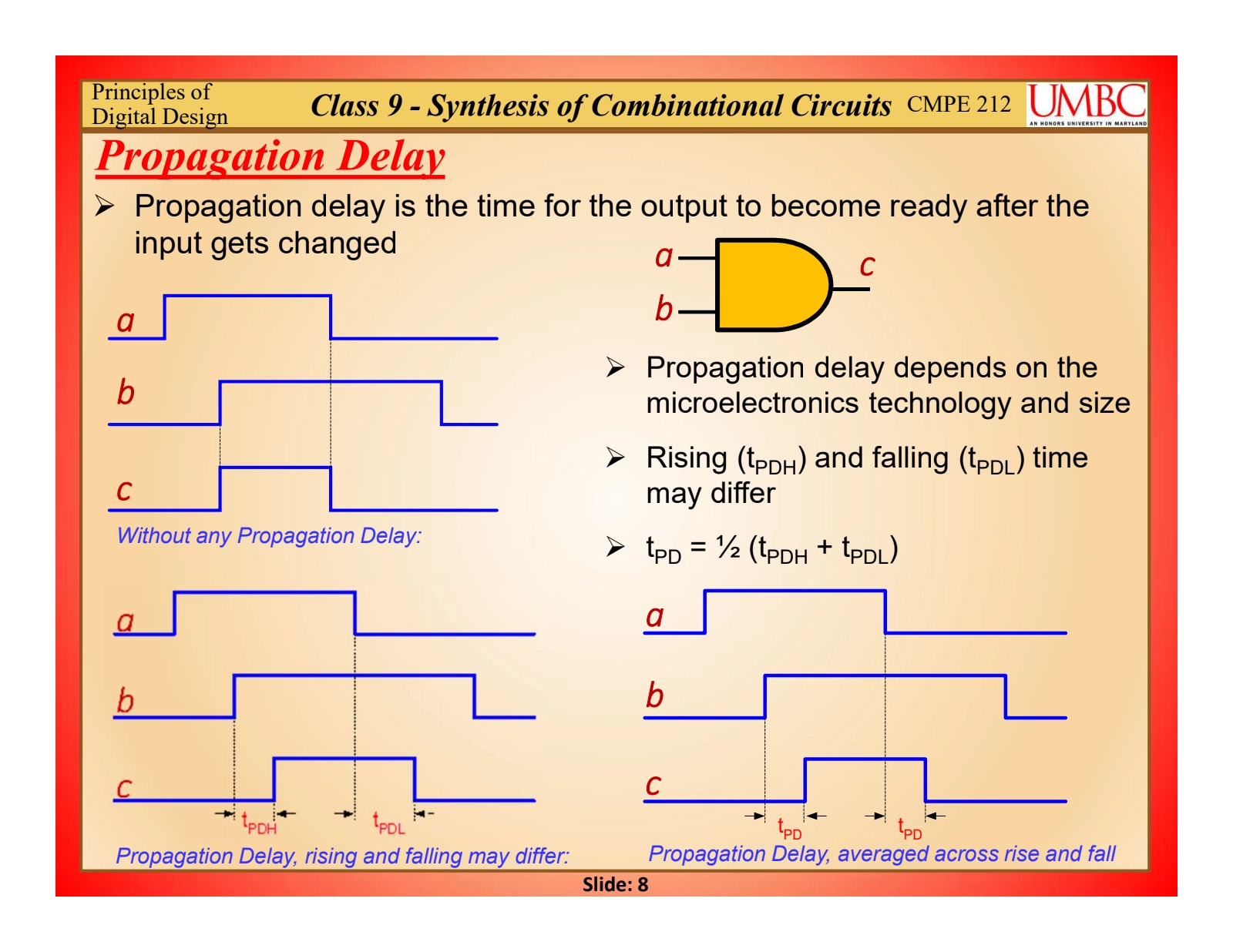

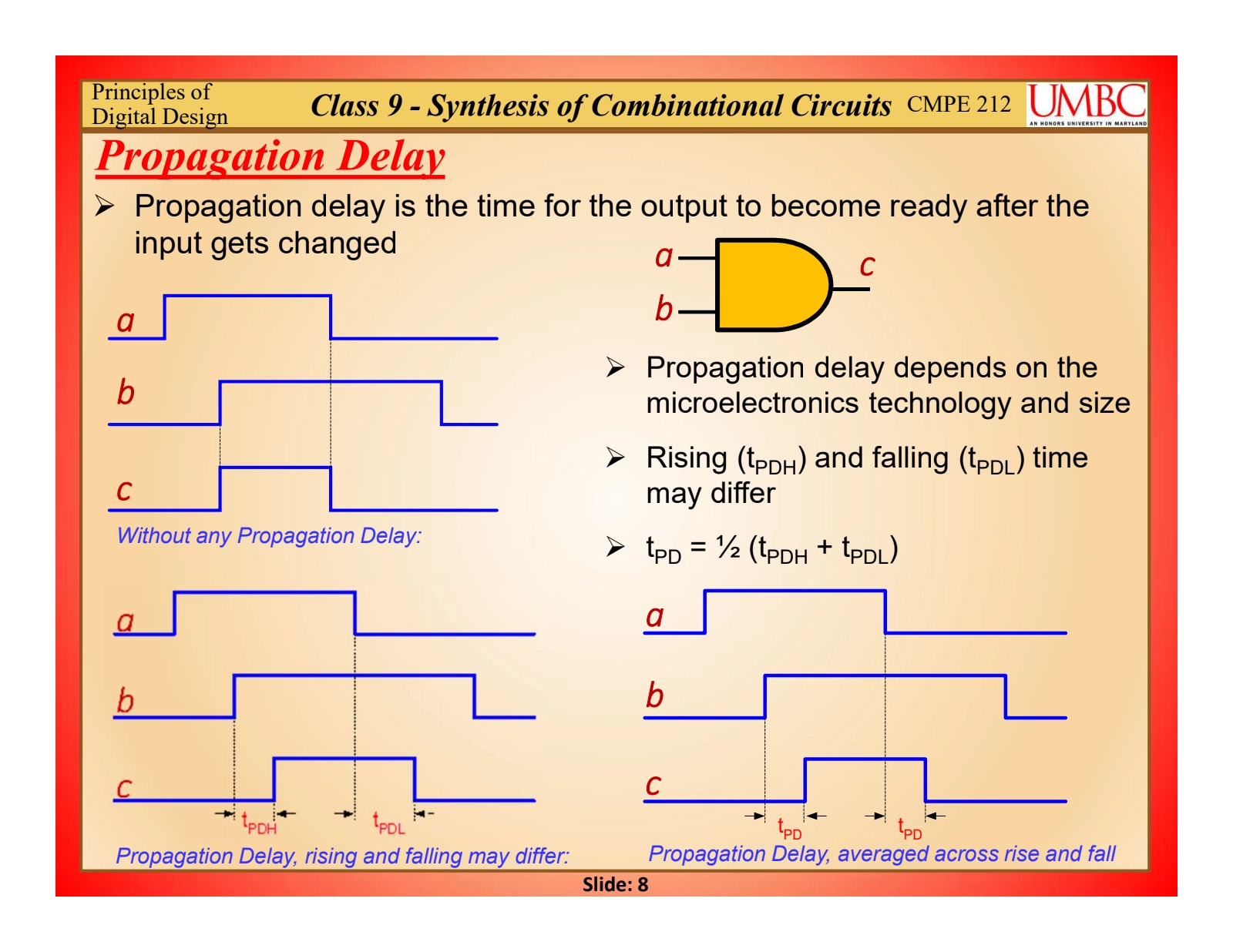

Class: 9, slide: 8 → Propagation Delay

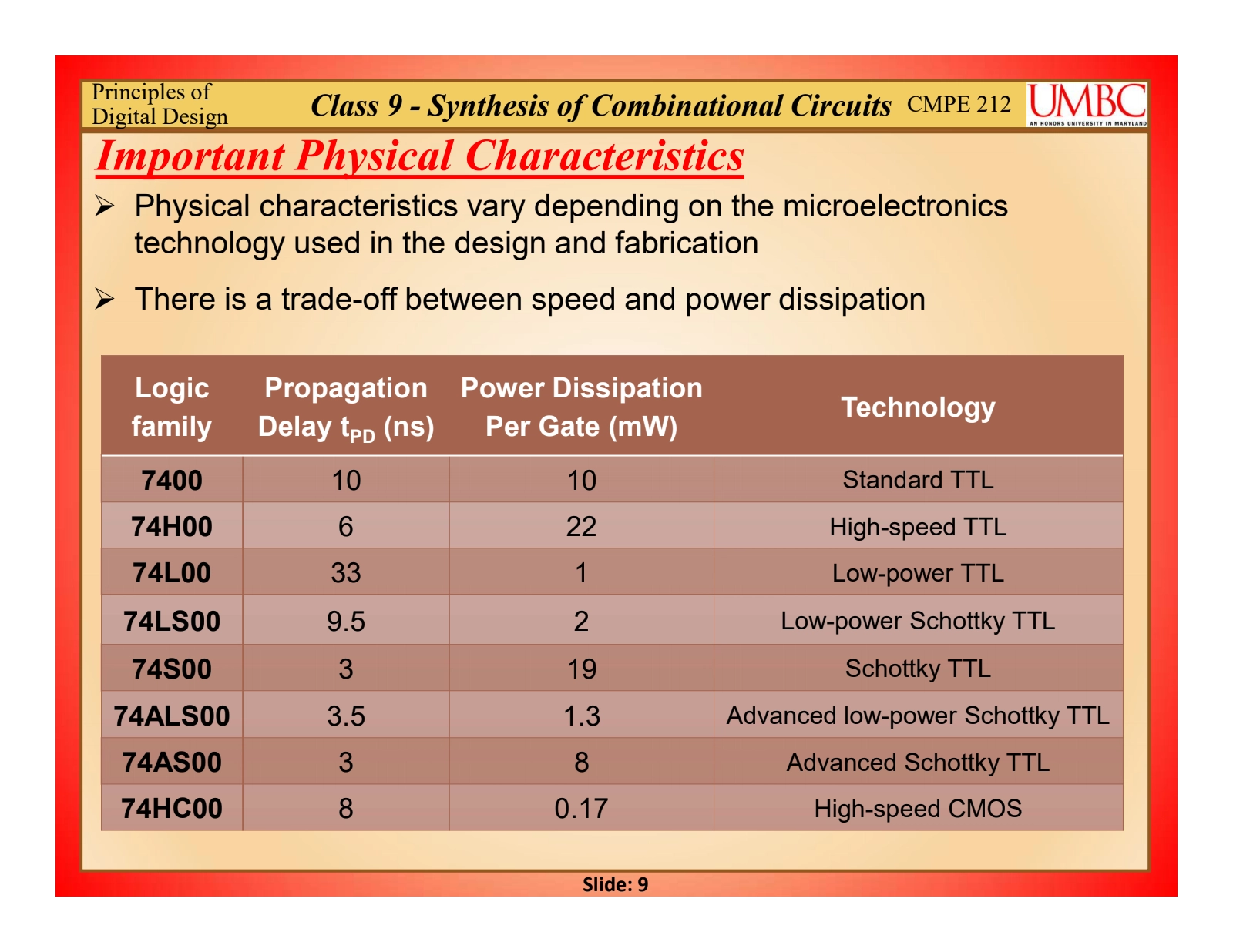

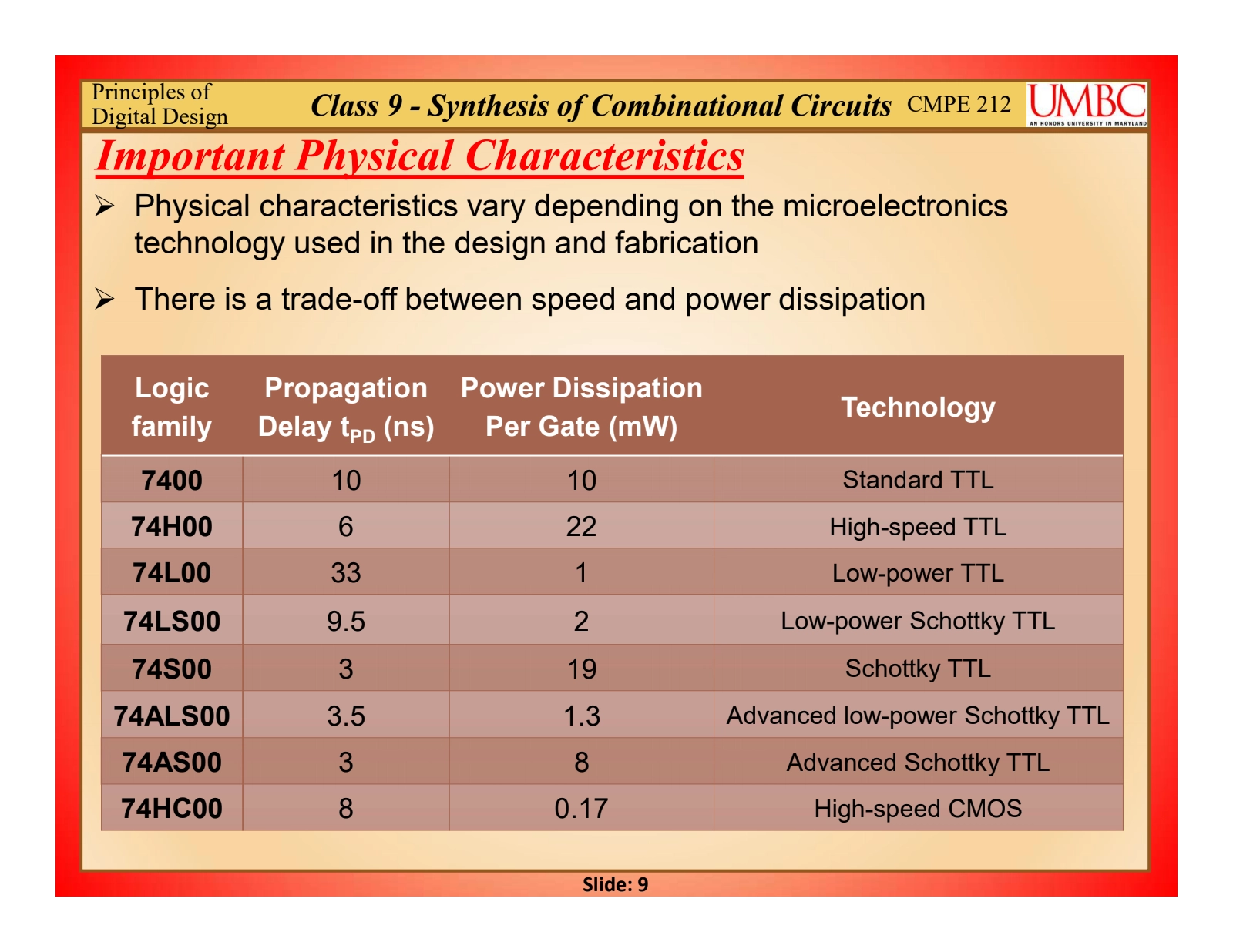

Class: 9, slide: 9 → Speed-Power trade-off

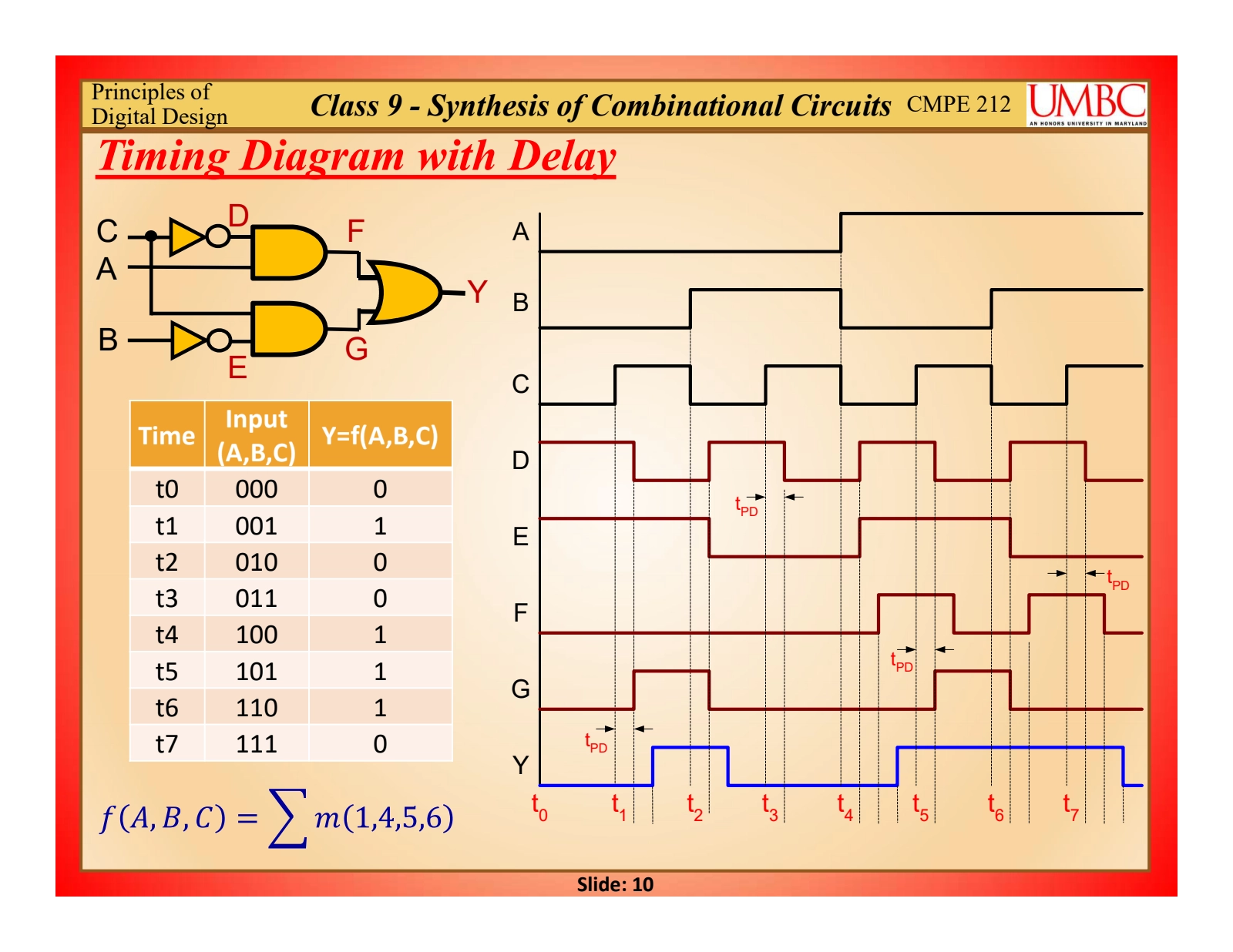

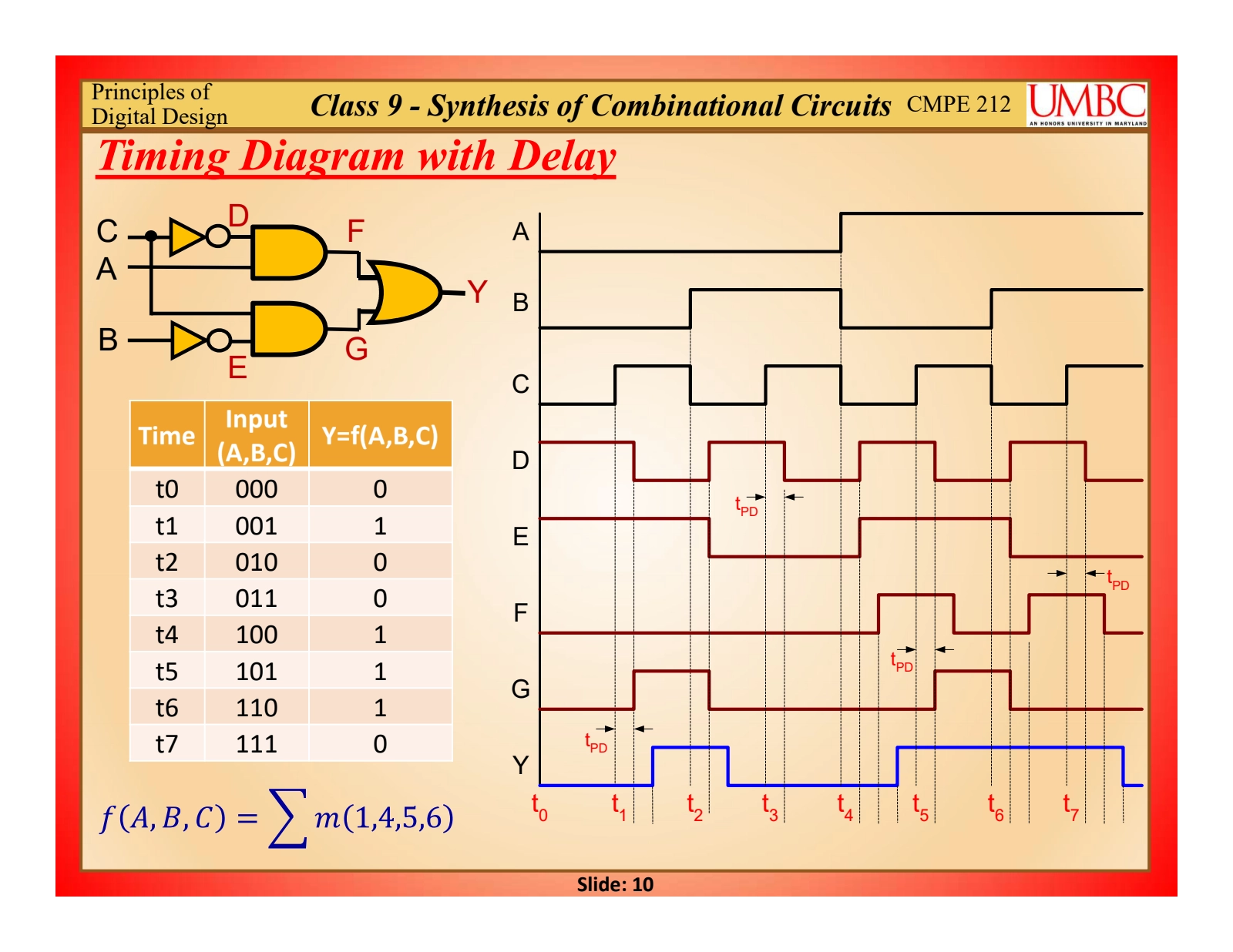

Class: 9, slide: 10 → Timing Diagram with Delay

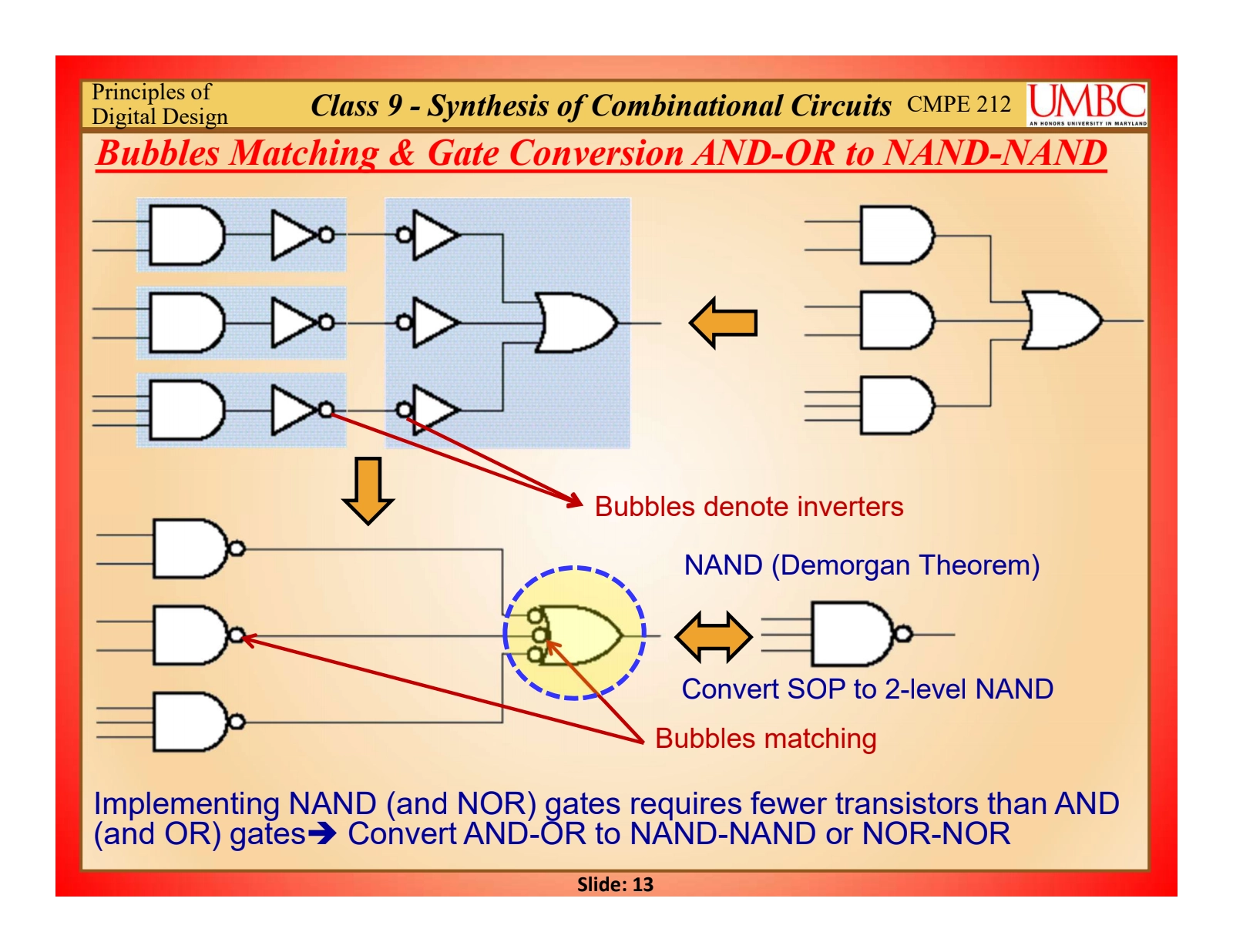

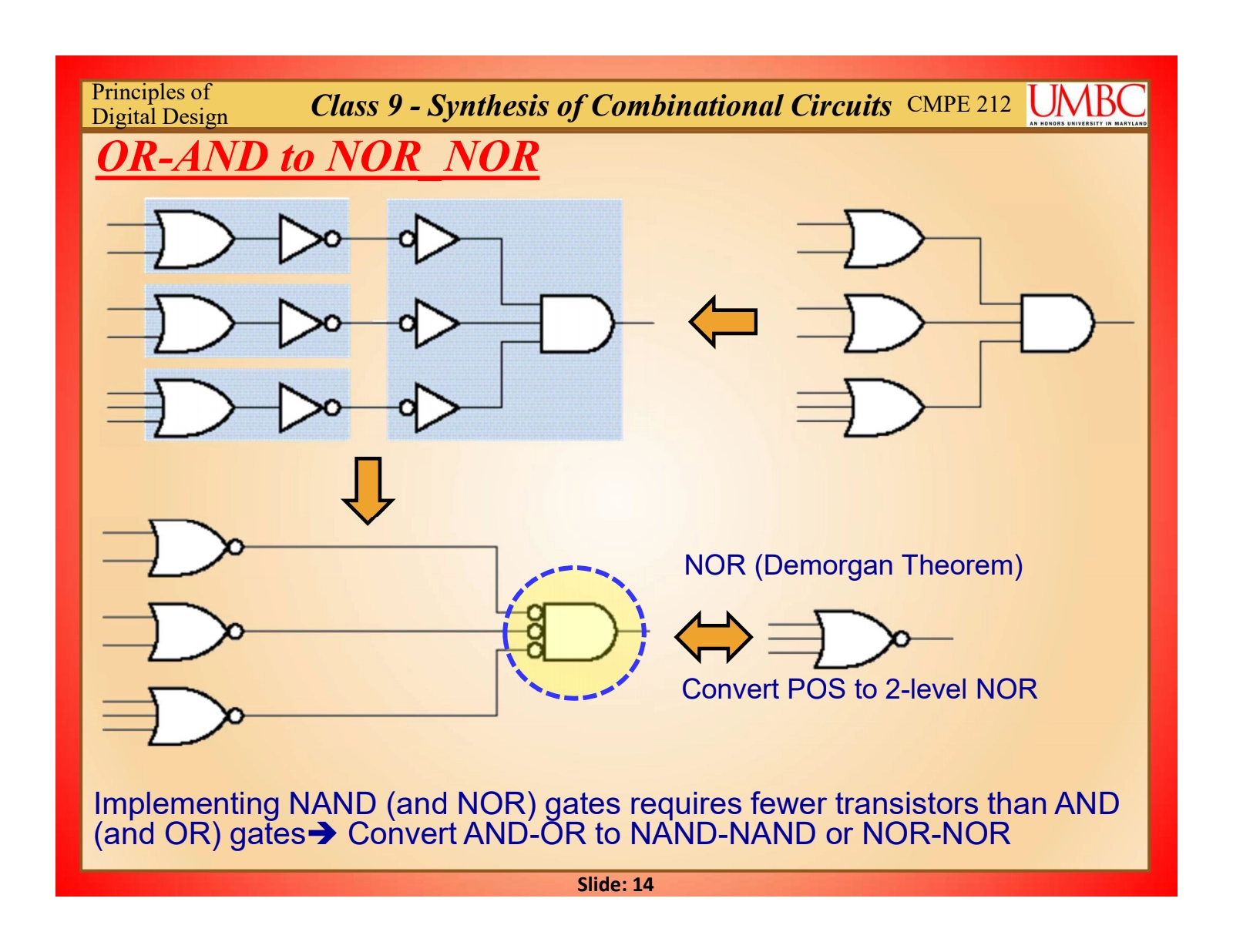

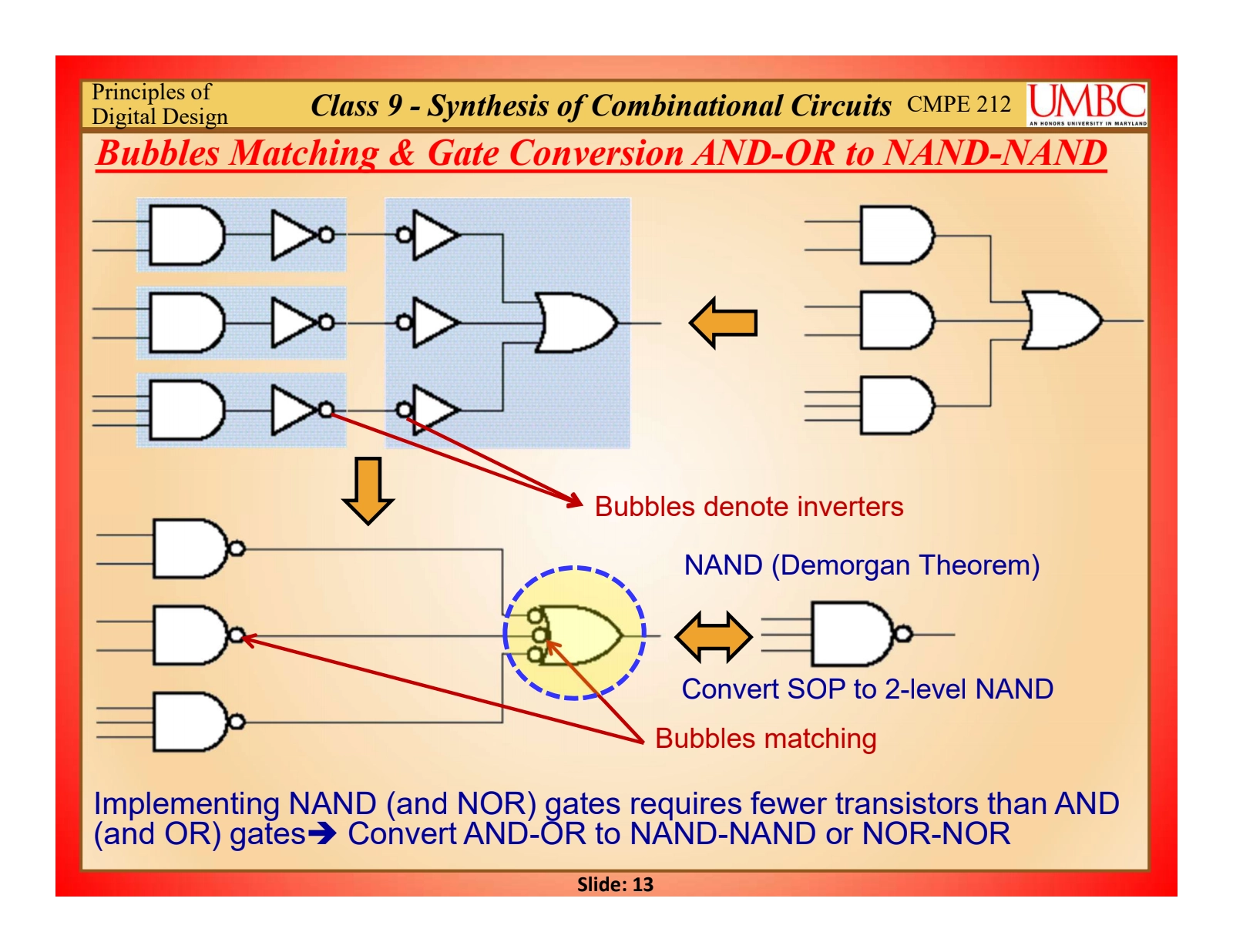

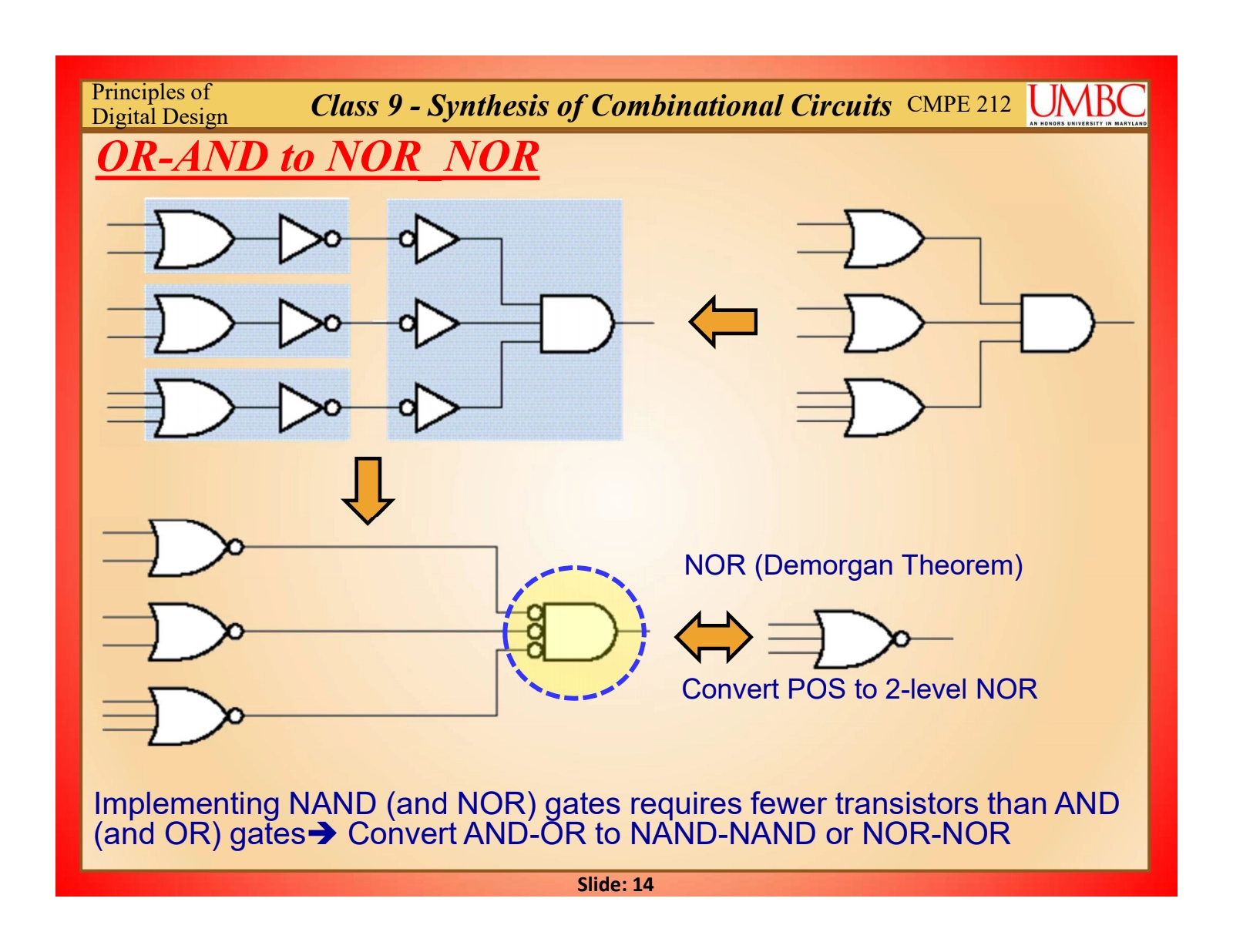

Class: 9, slide: 13-14 → Bubles Matching & Gate Conversion

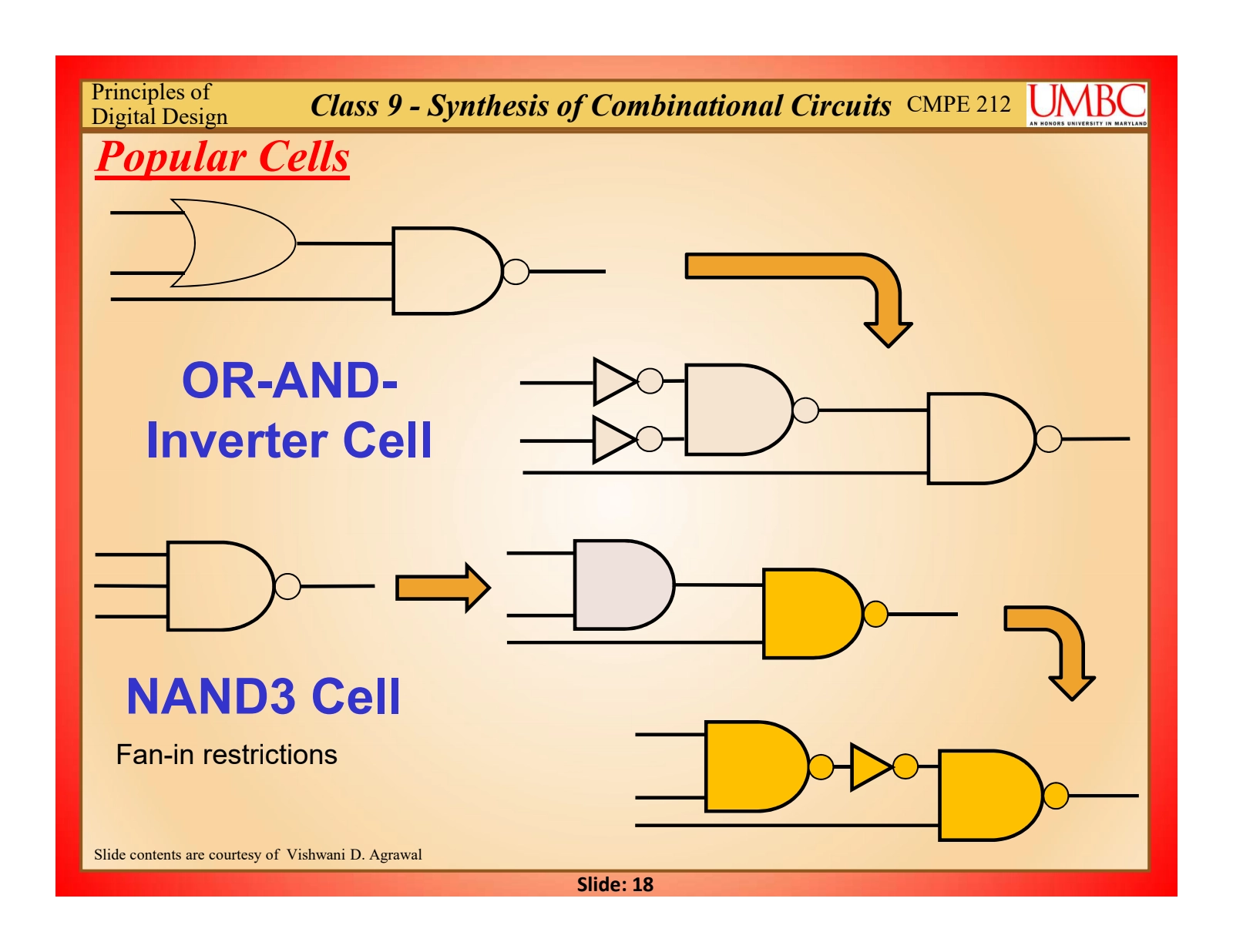

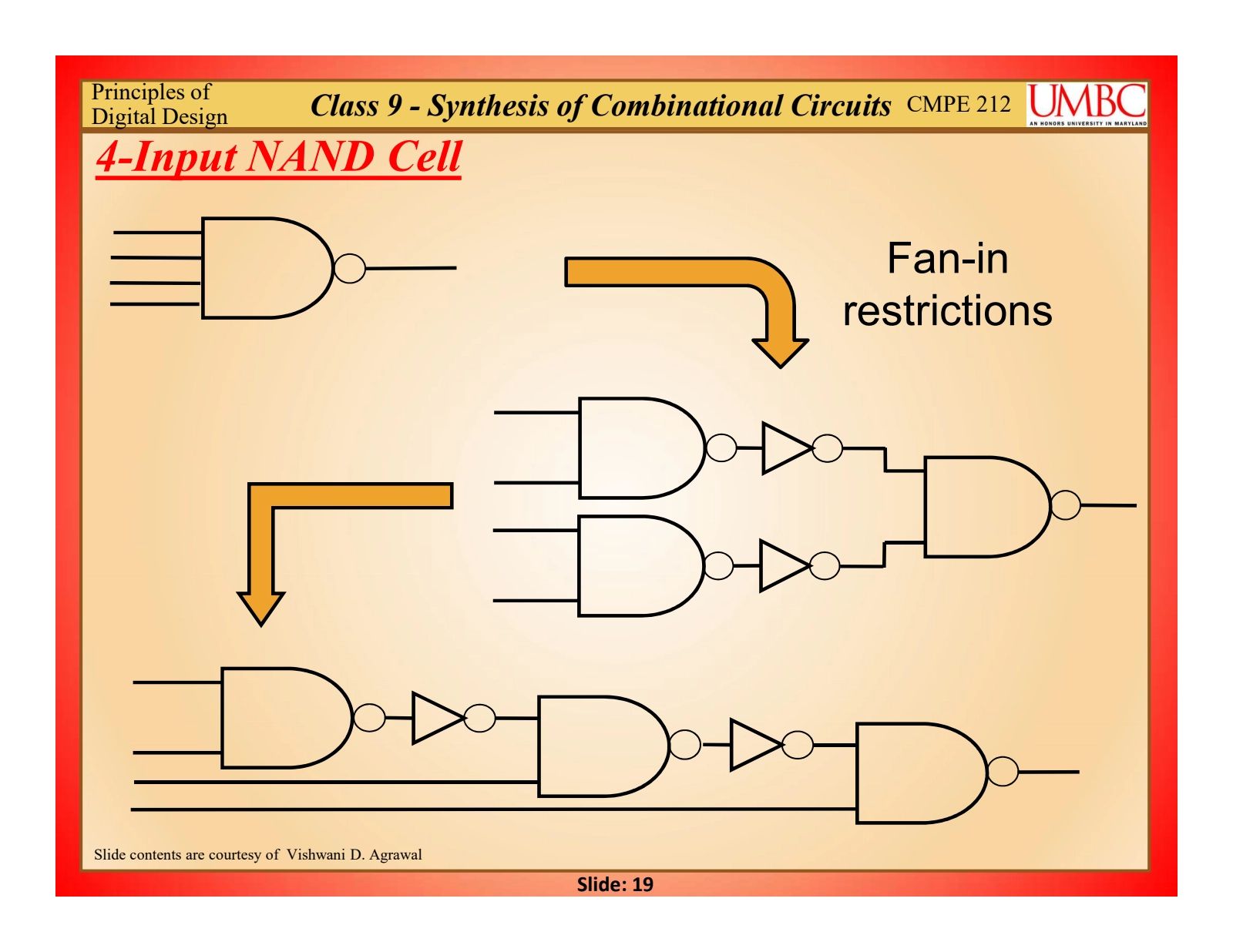

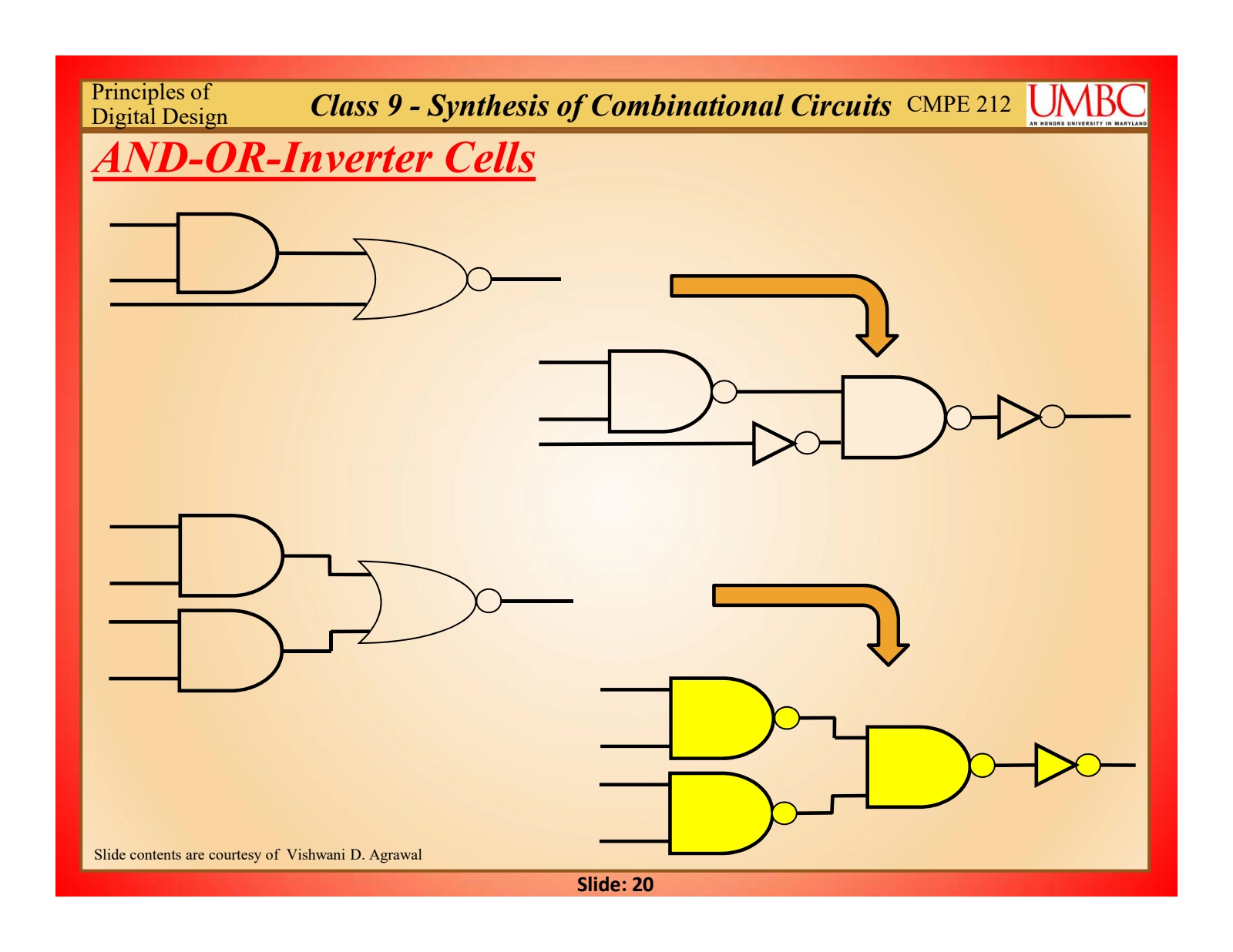

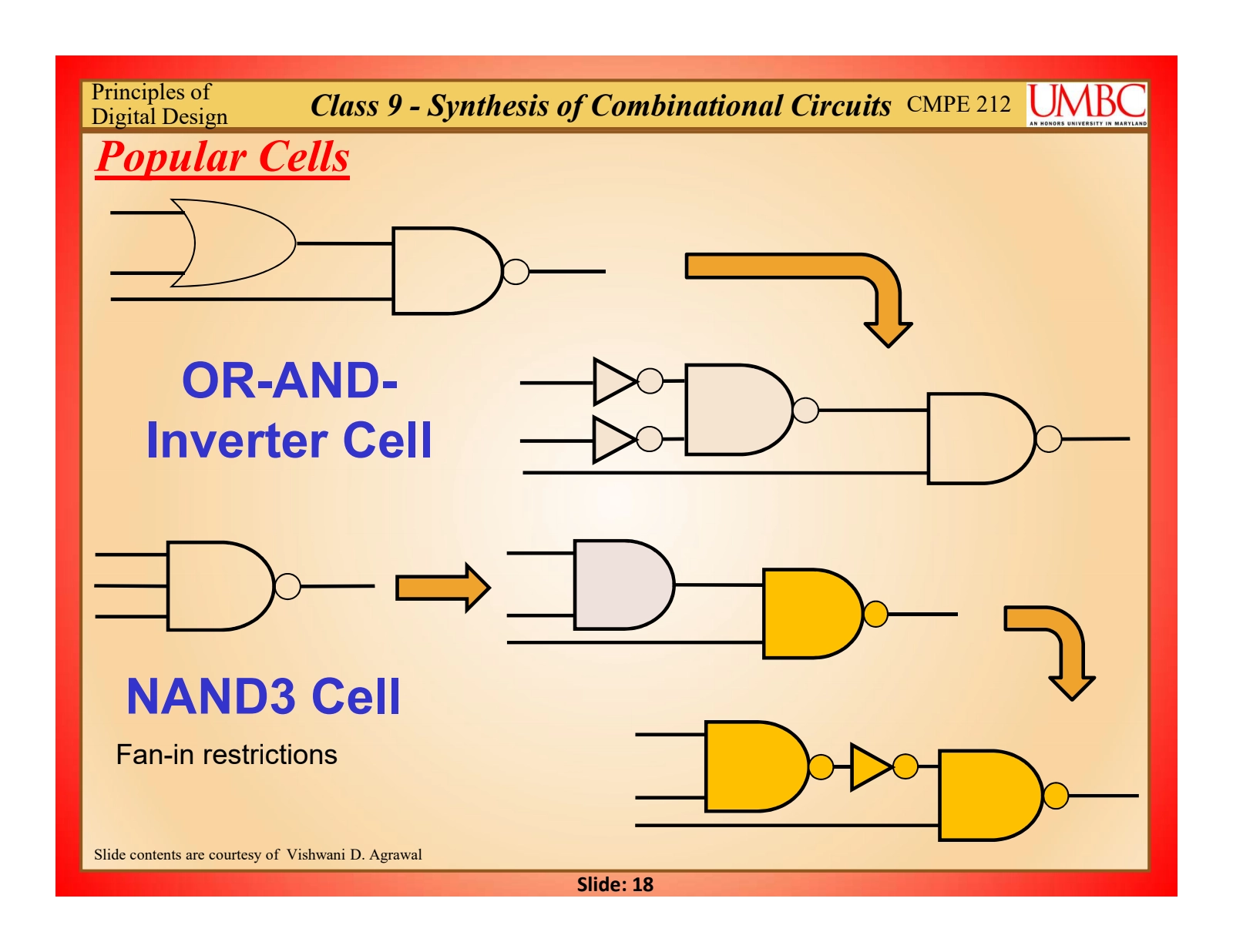

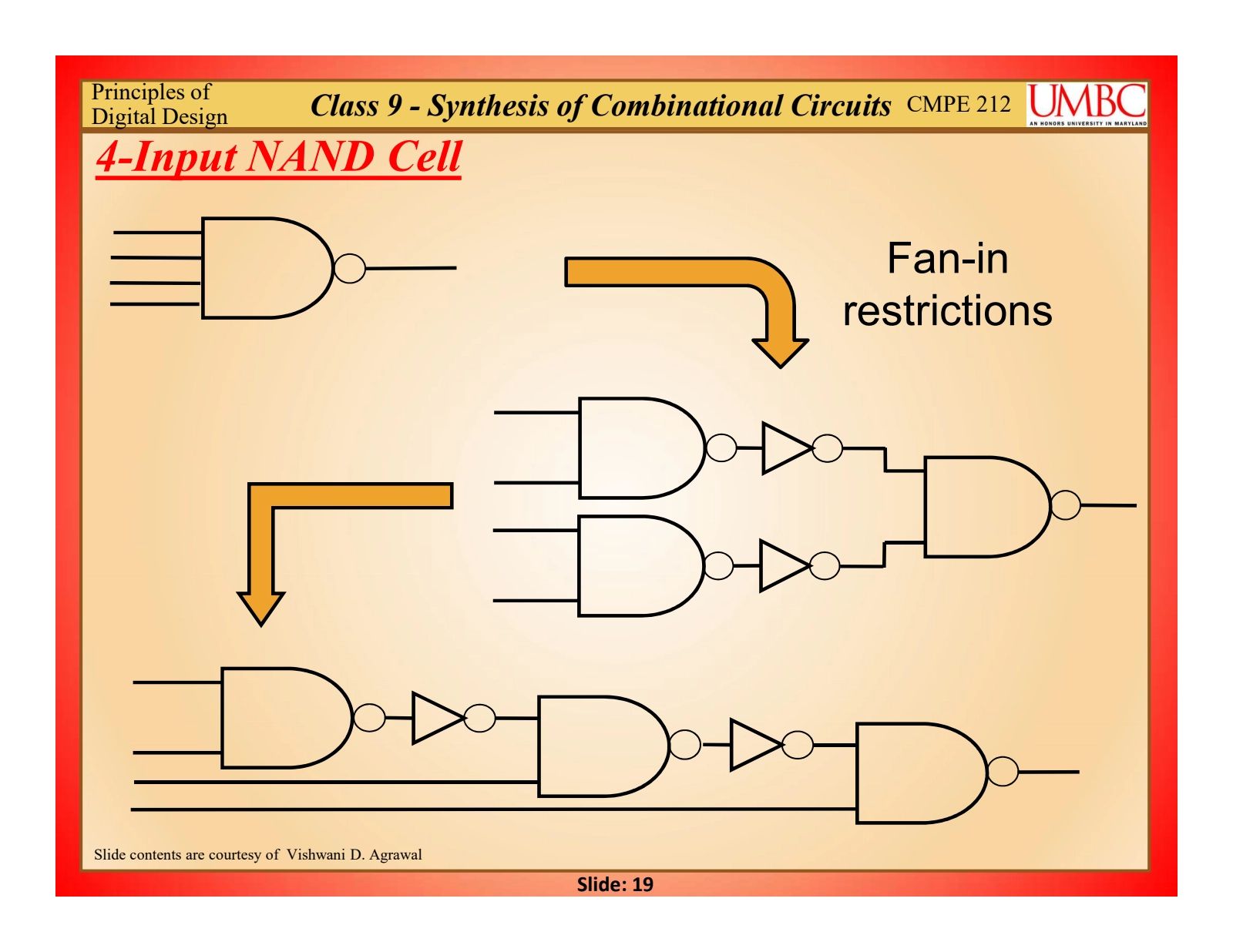

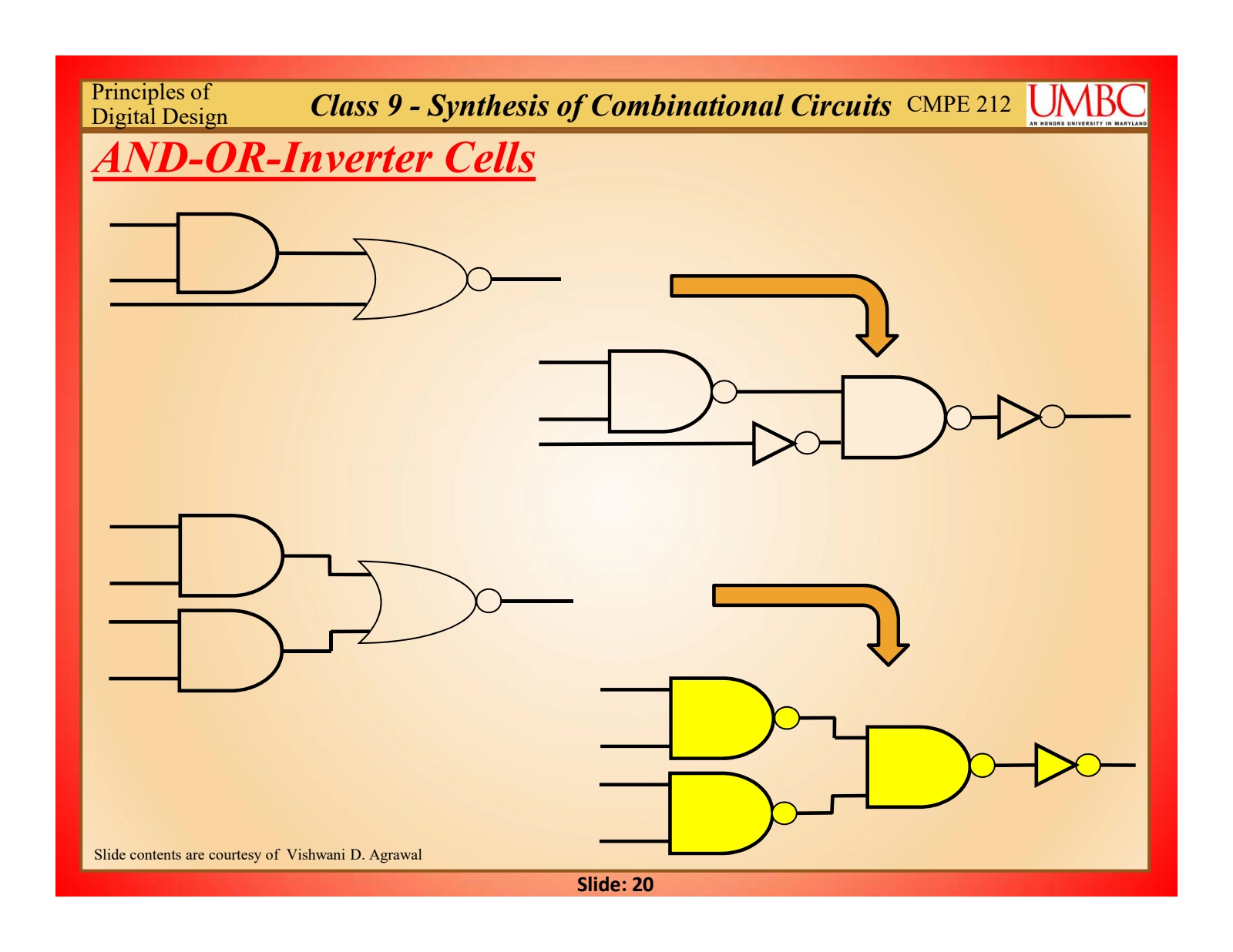

Class: 9, slide: 18-20 → Converting Popular Cells to 2 Input Nands

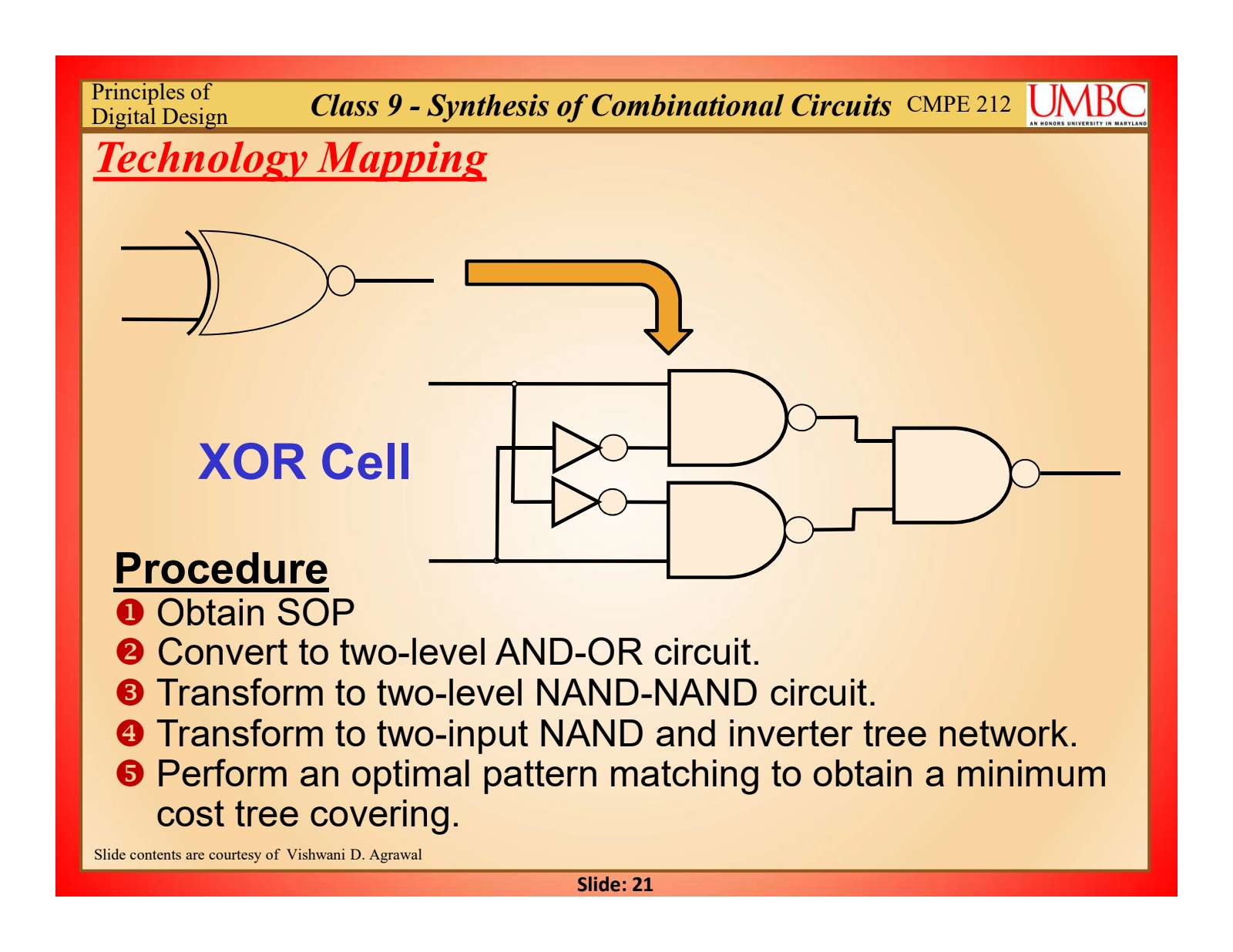

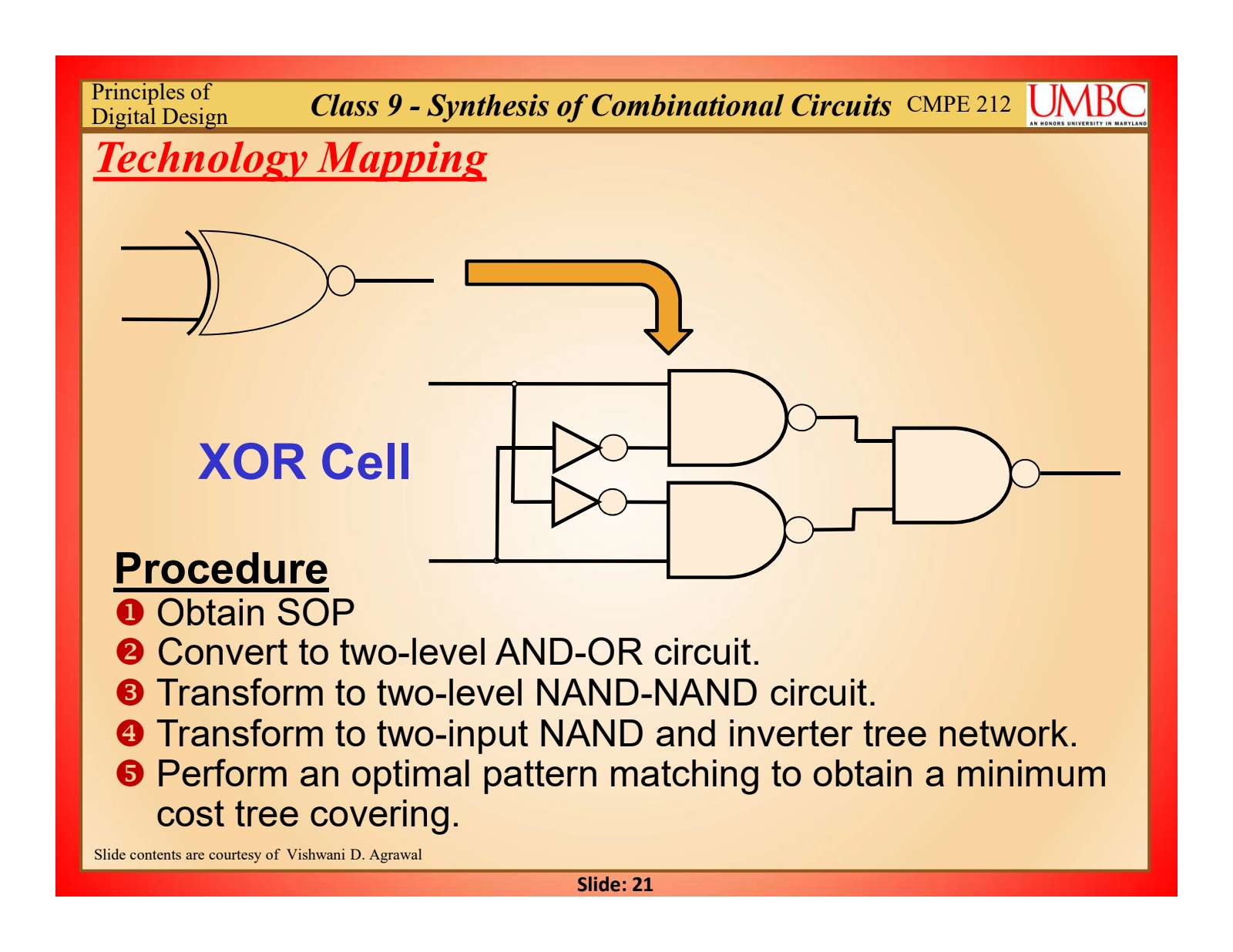

Class: 9, slide: 21 → Technology Mapping - XOR

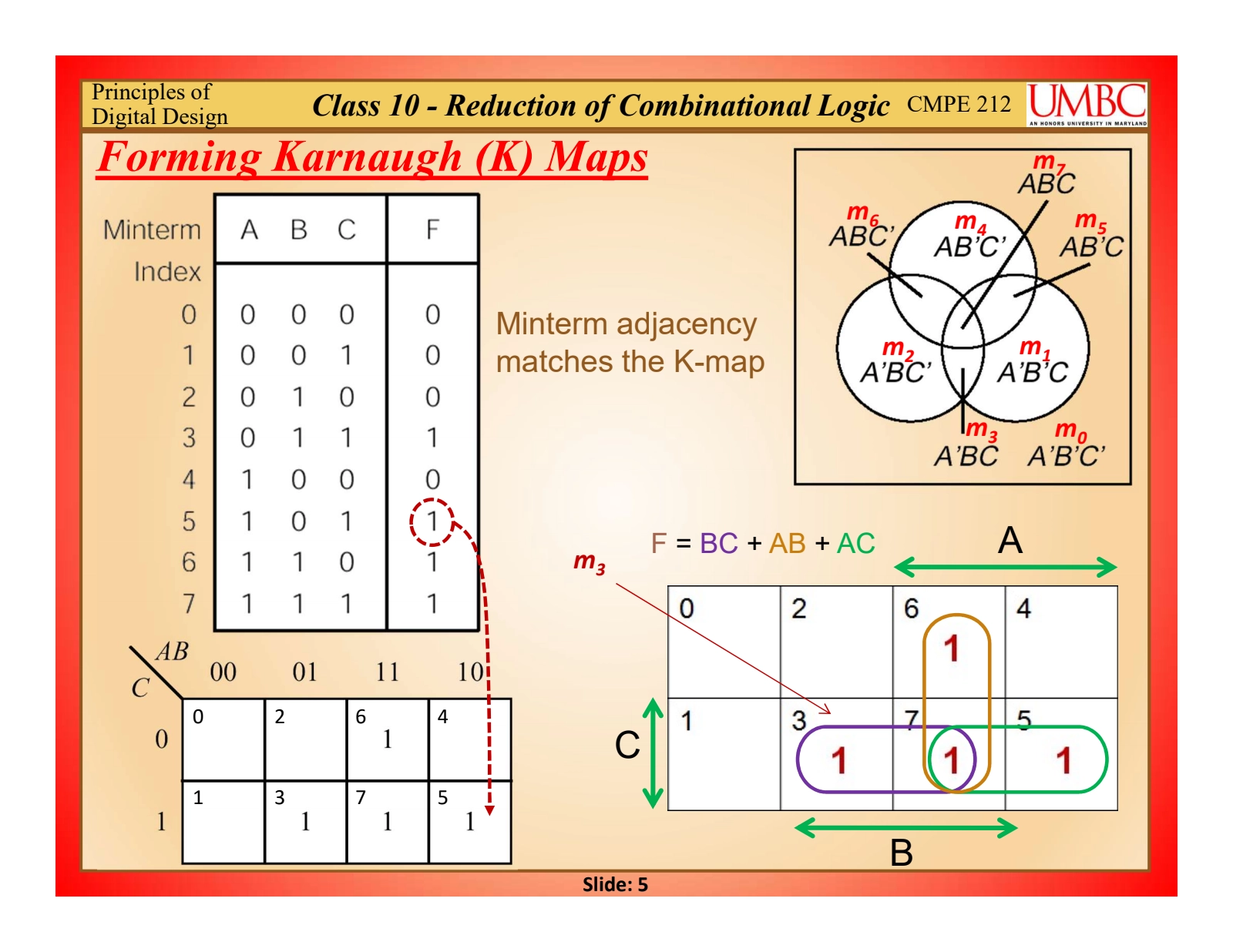

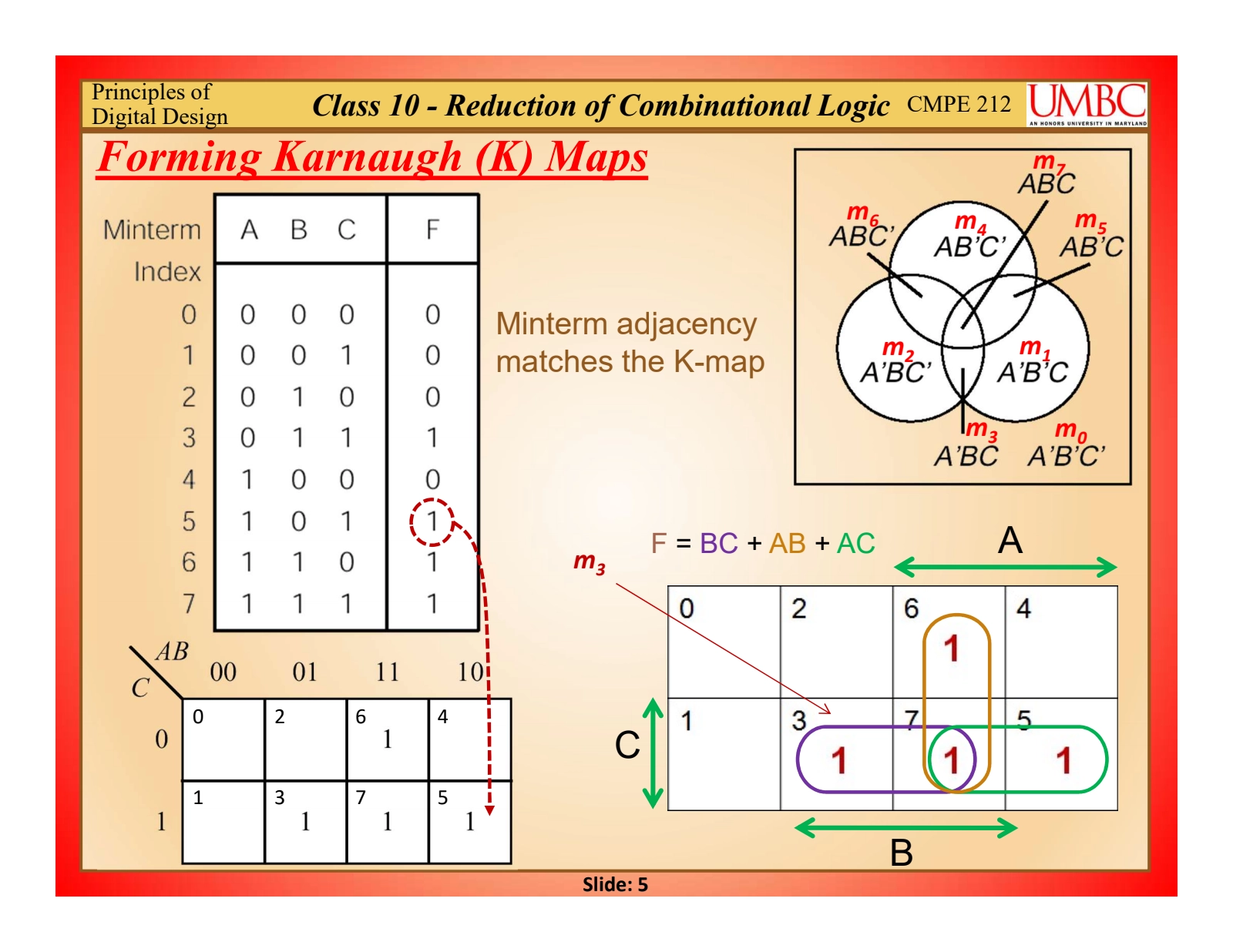

Class: 10, slide: 5 → Forming Karnaugh Maps

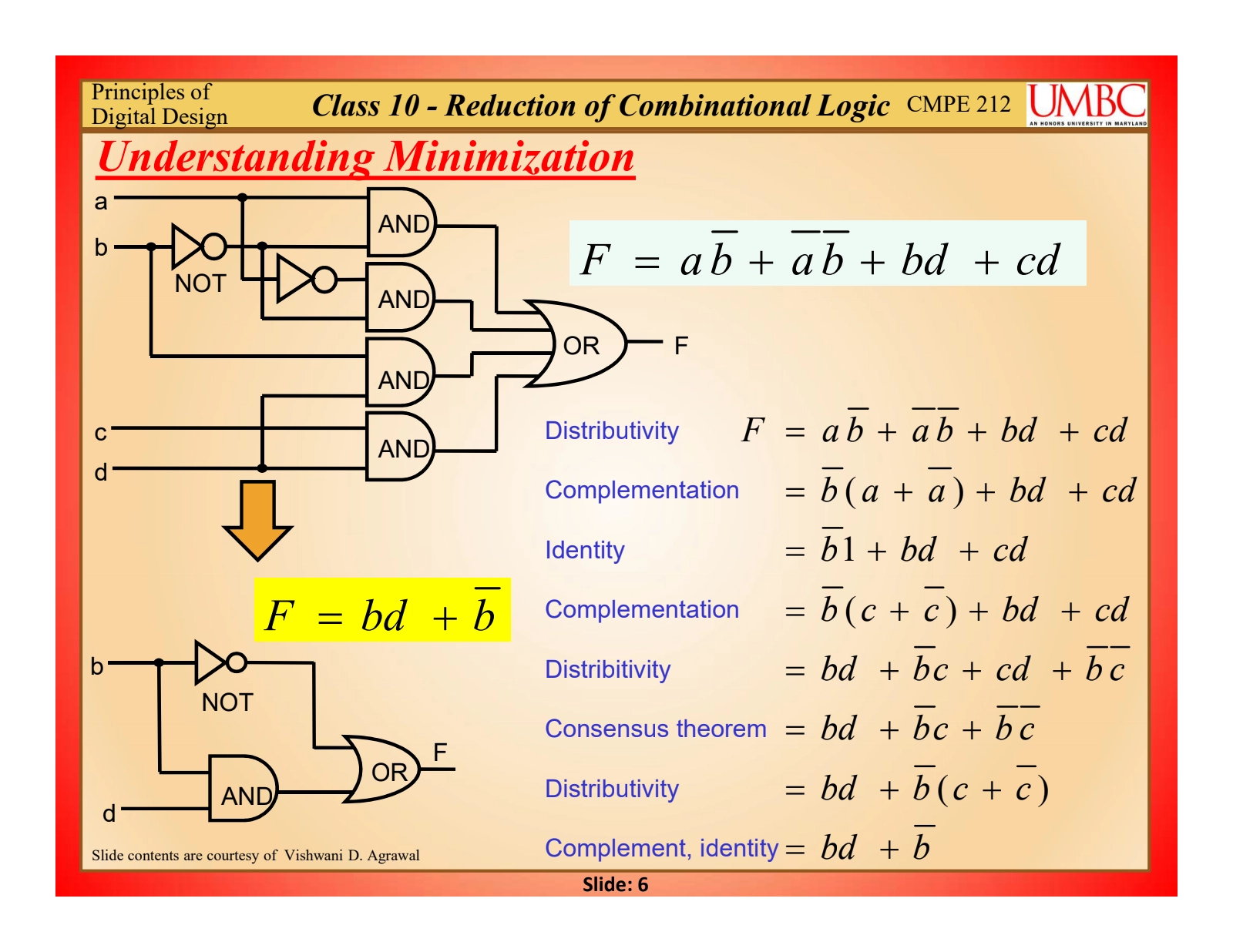

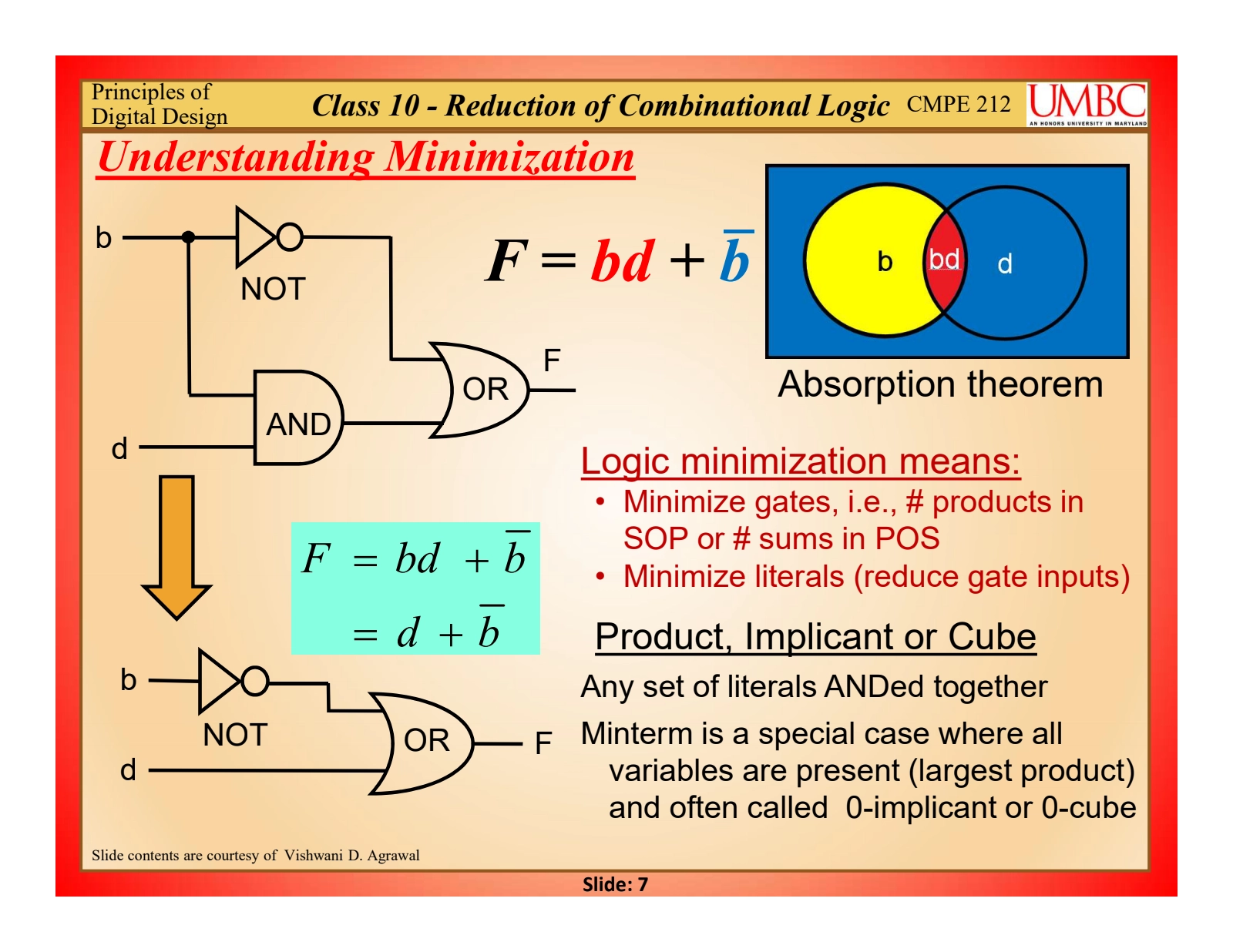

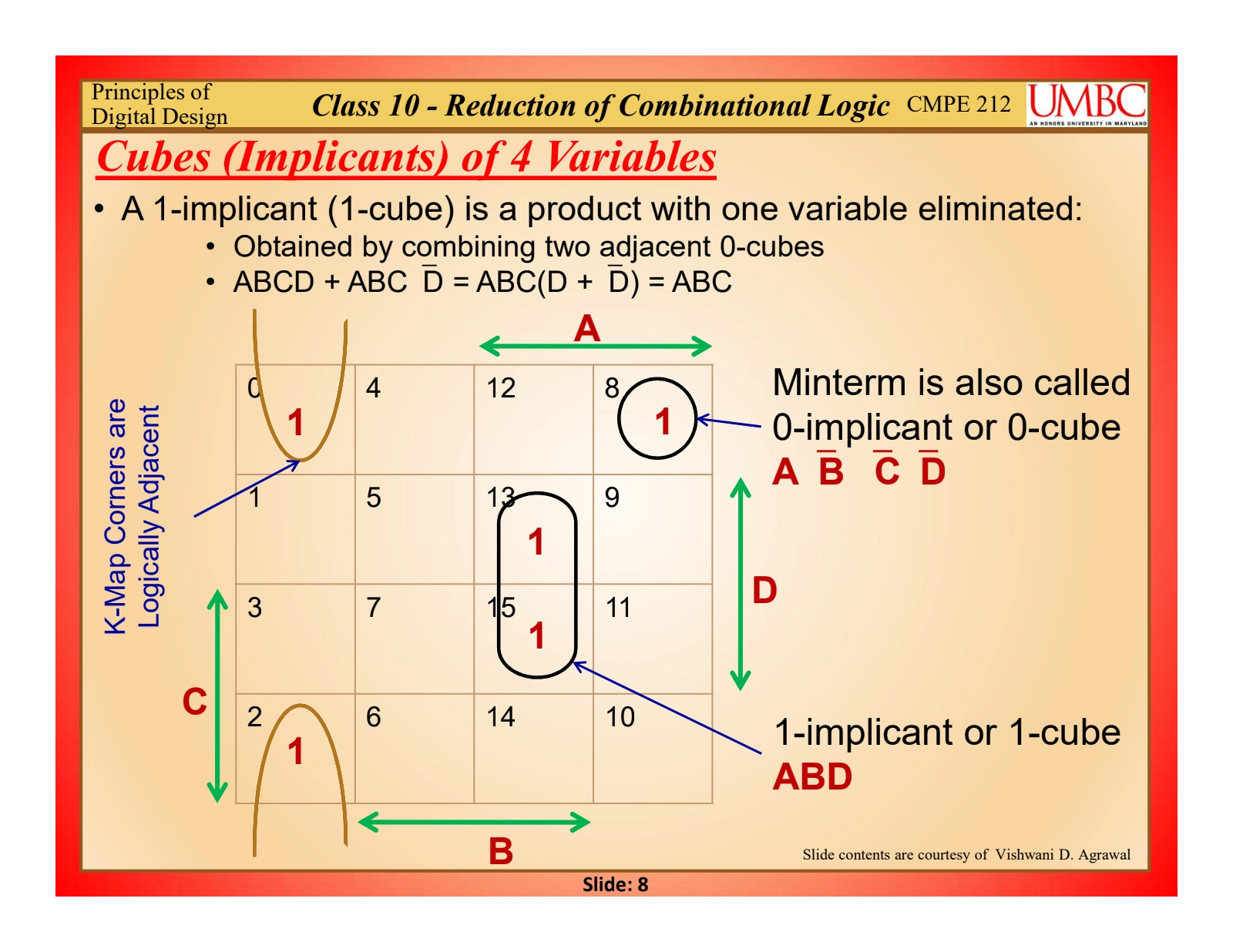

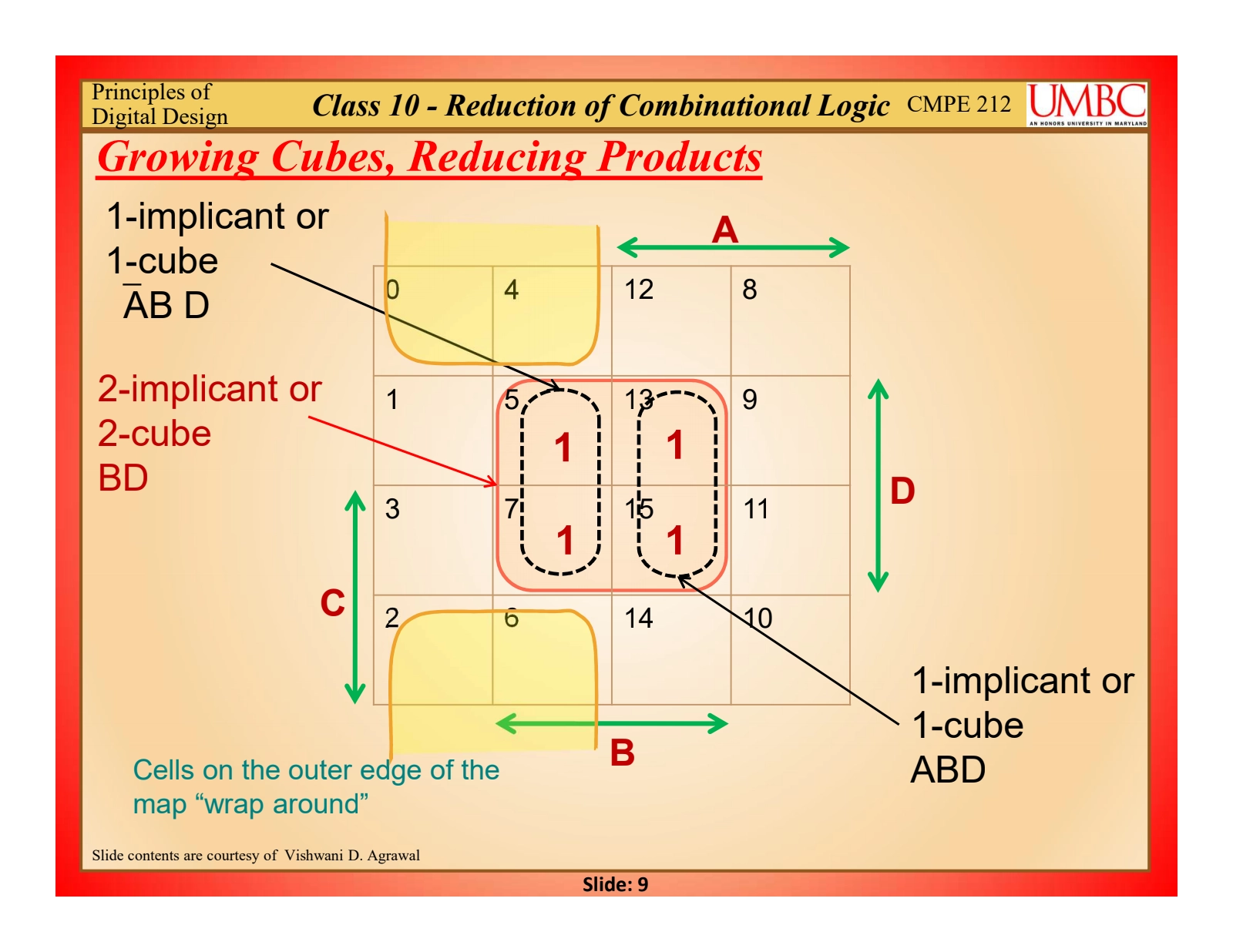

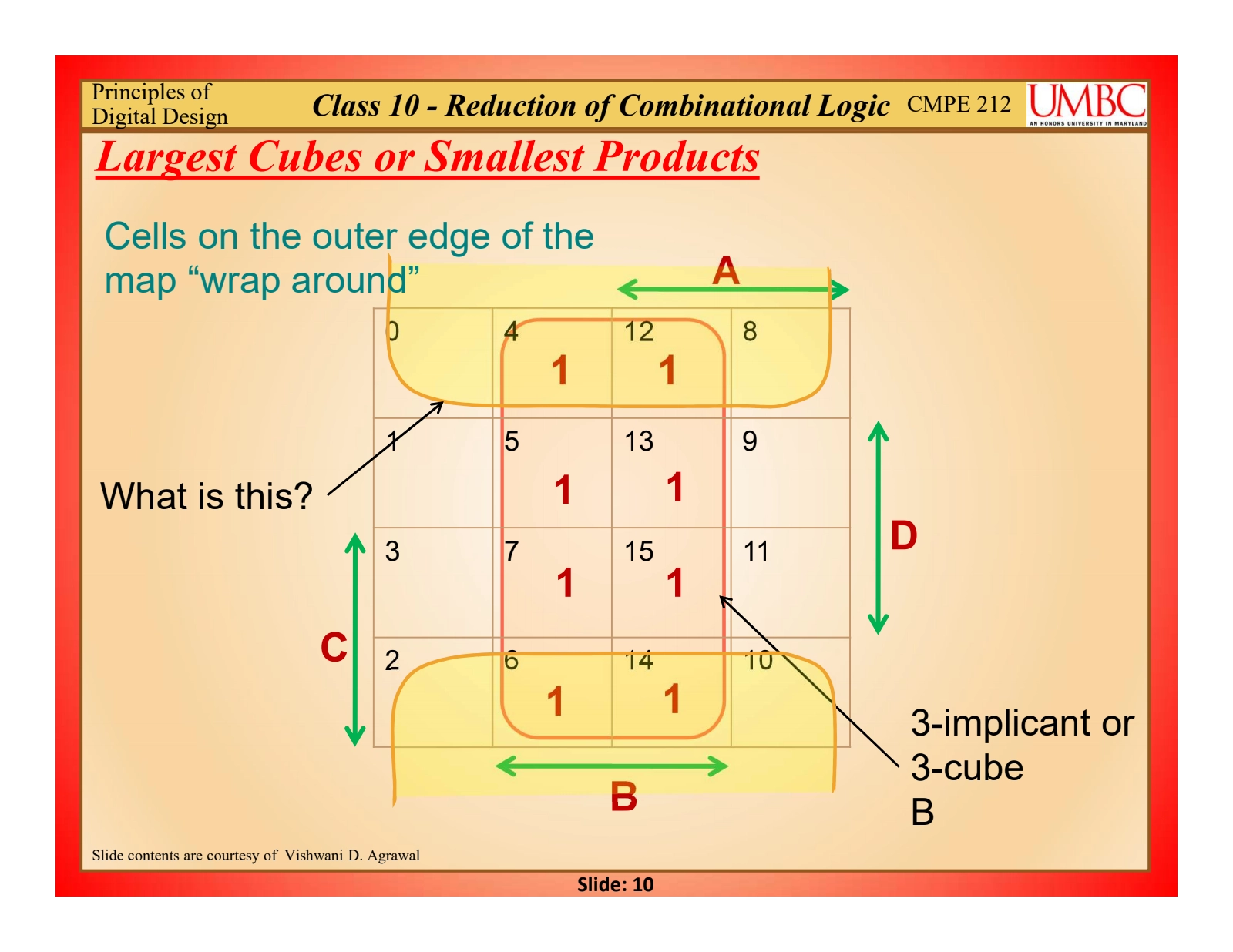

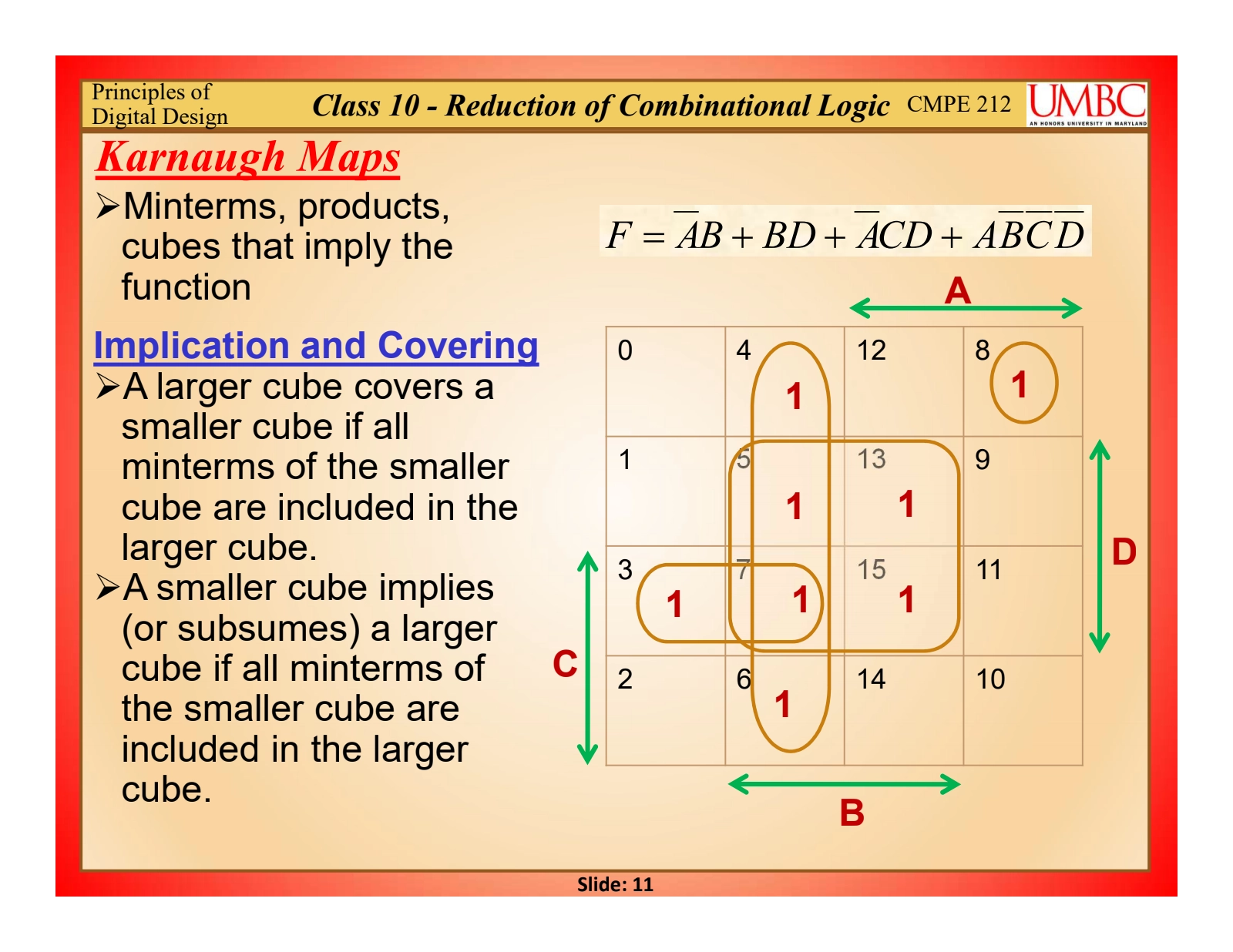

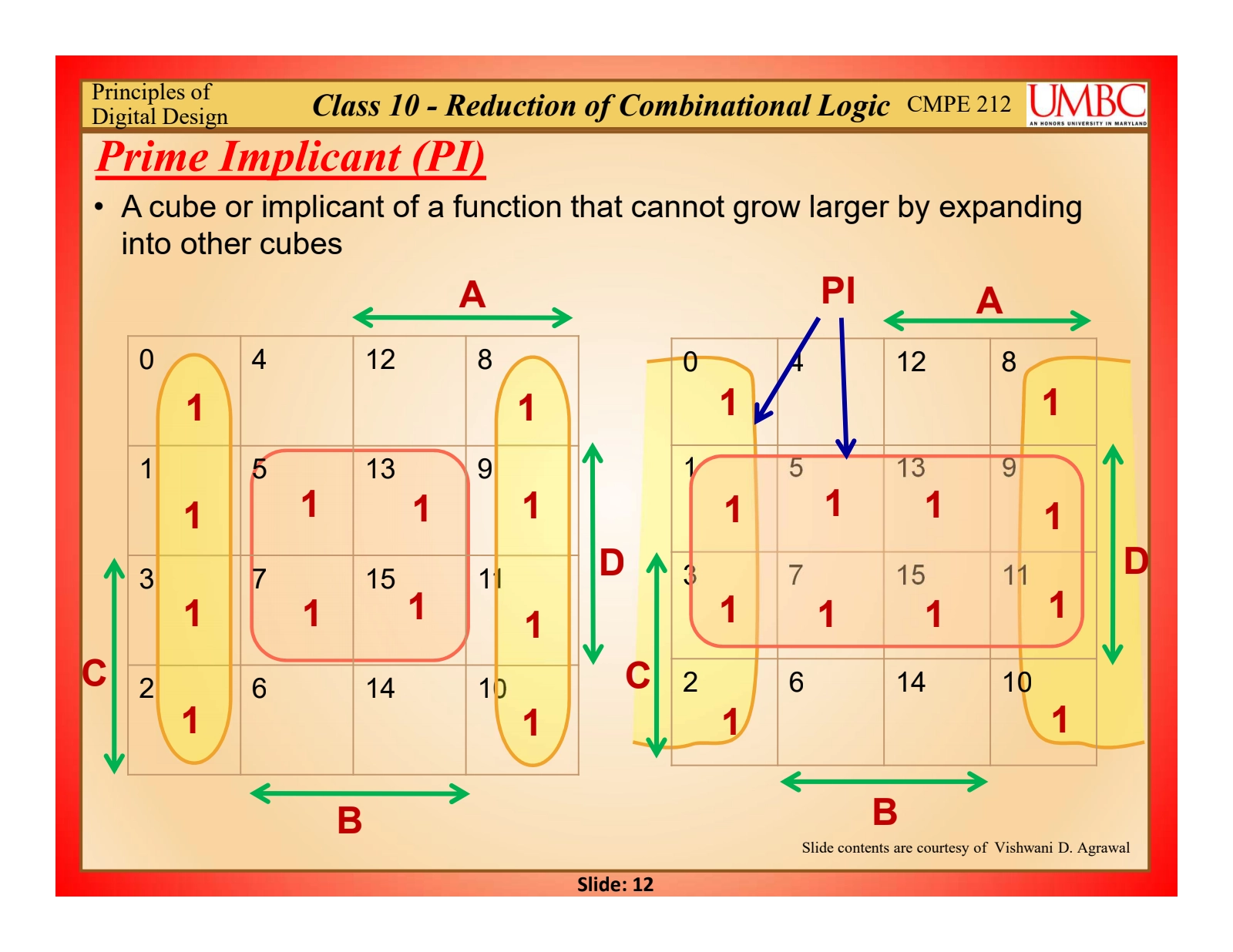

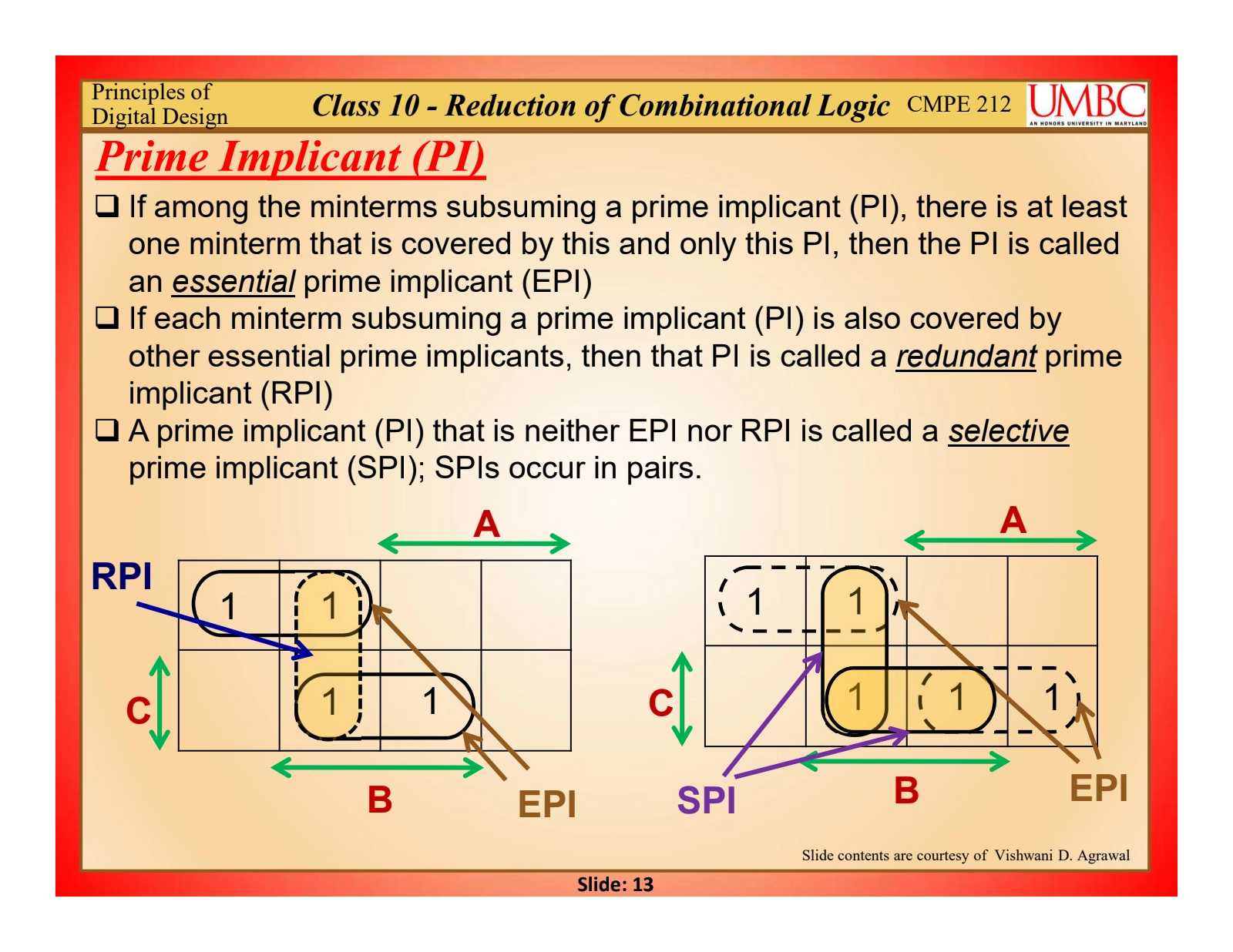

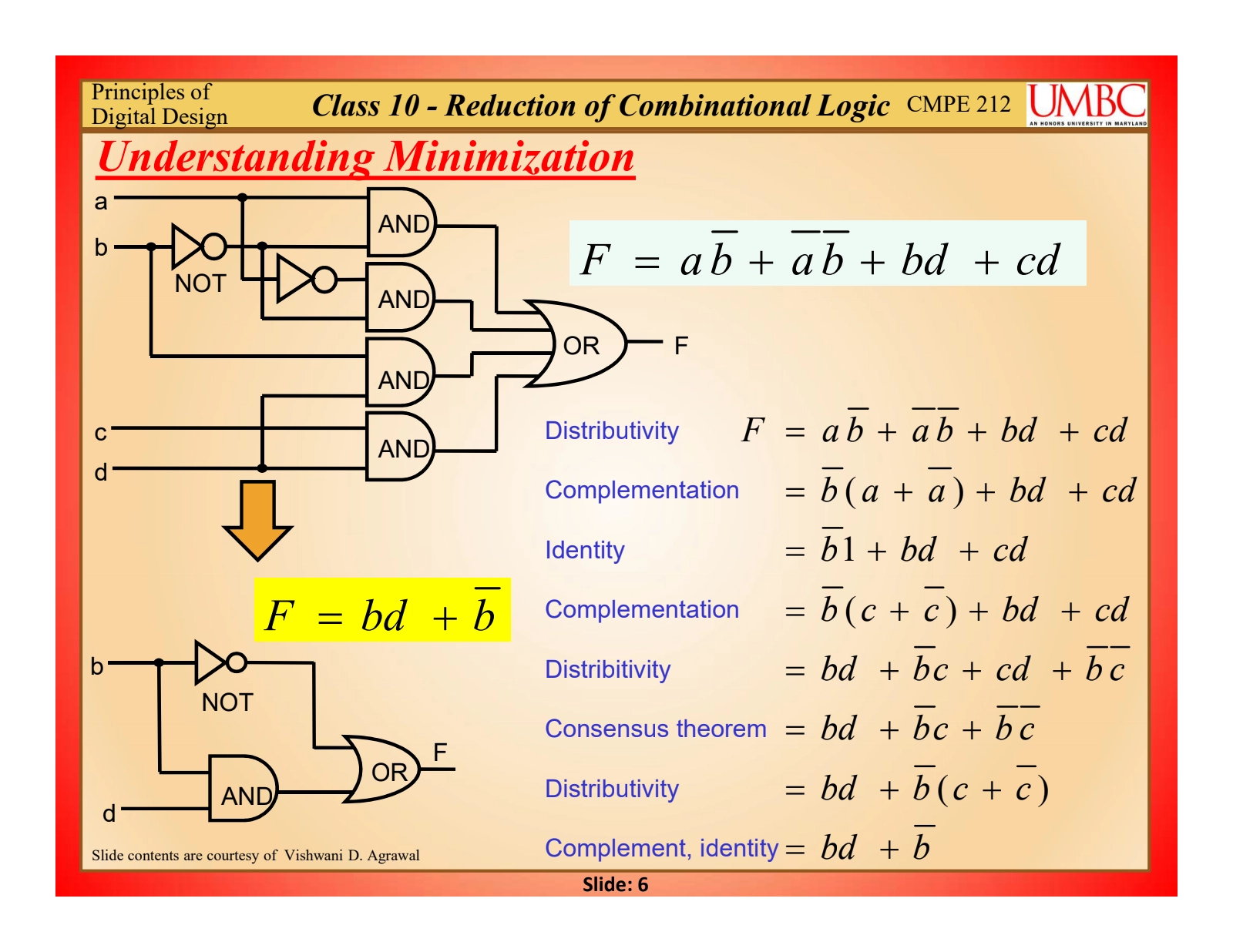

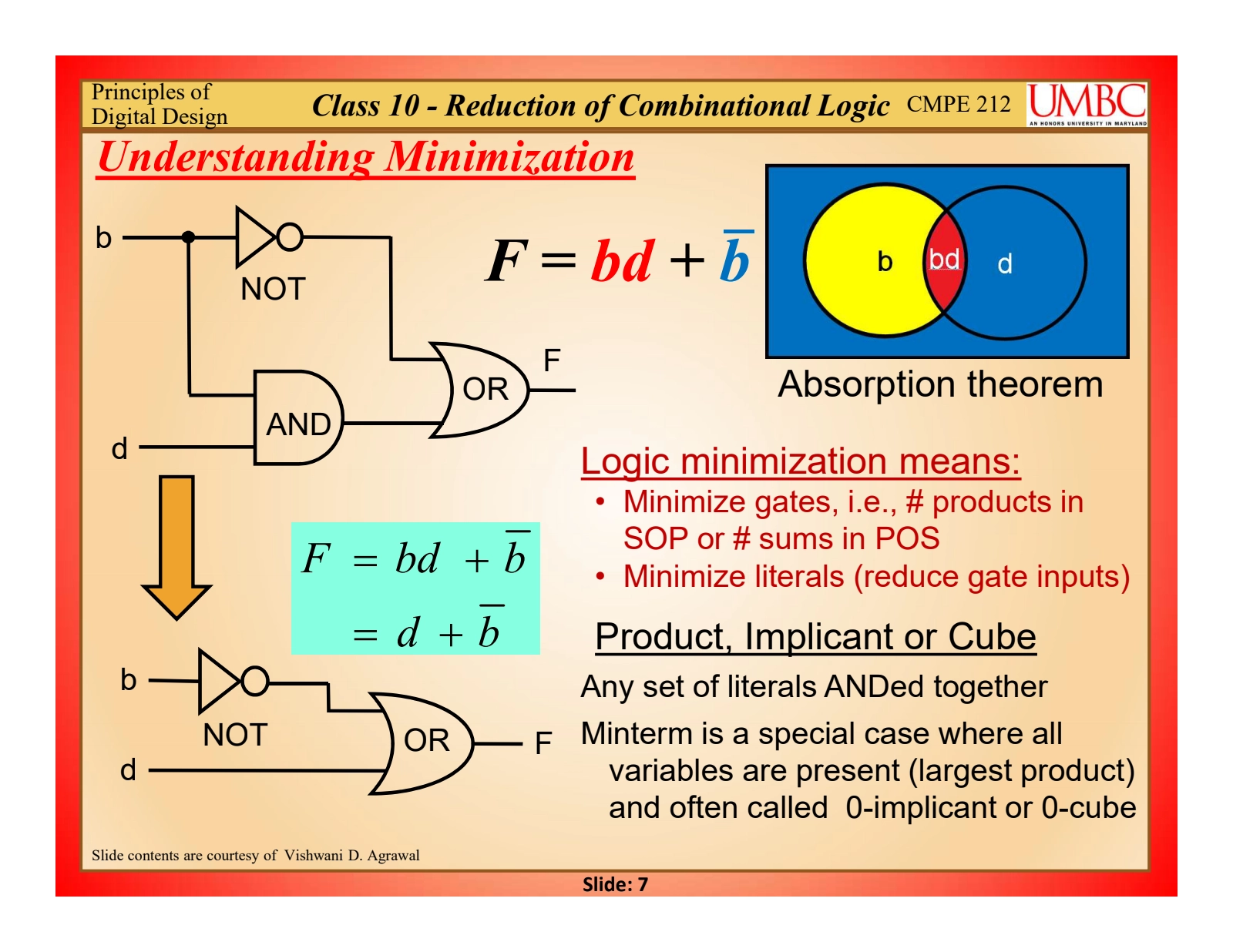

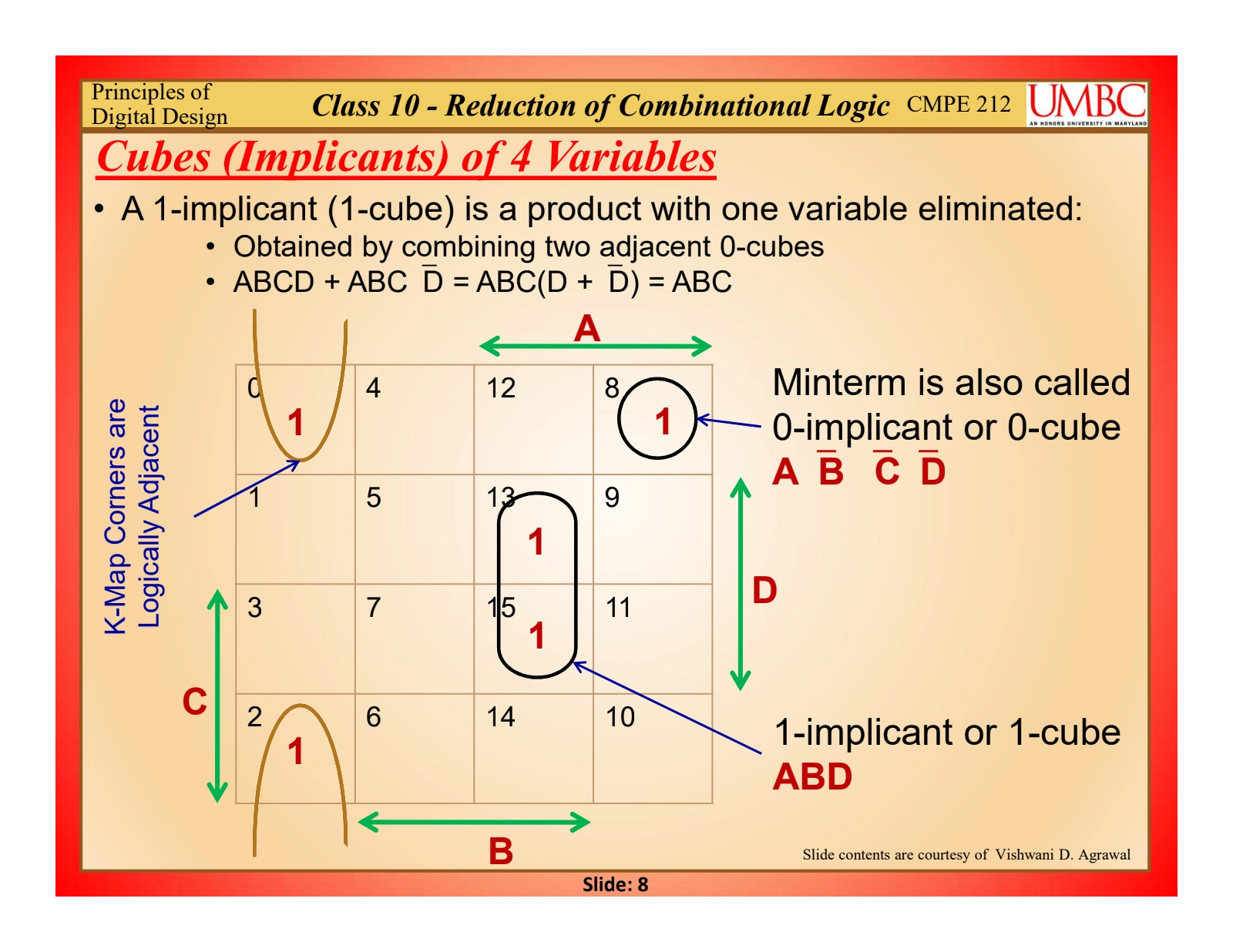

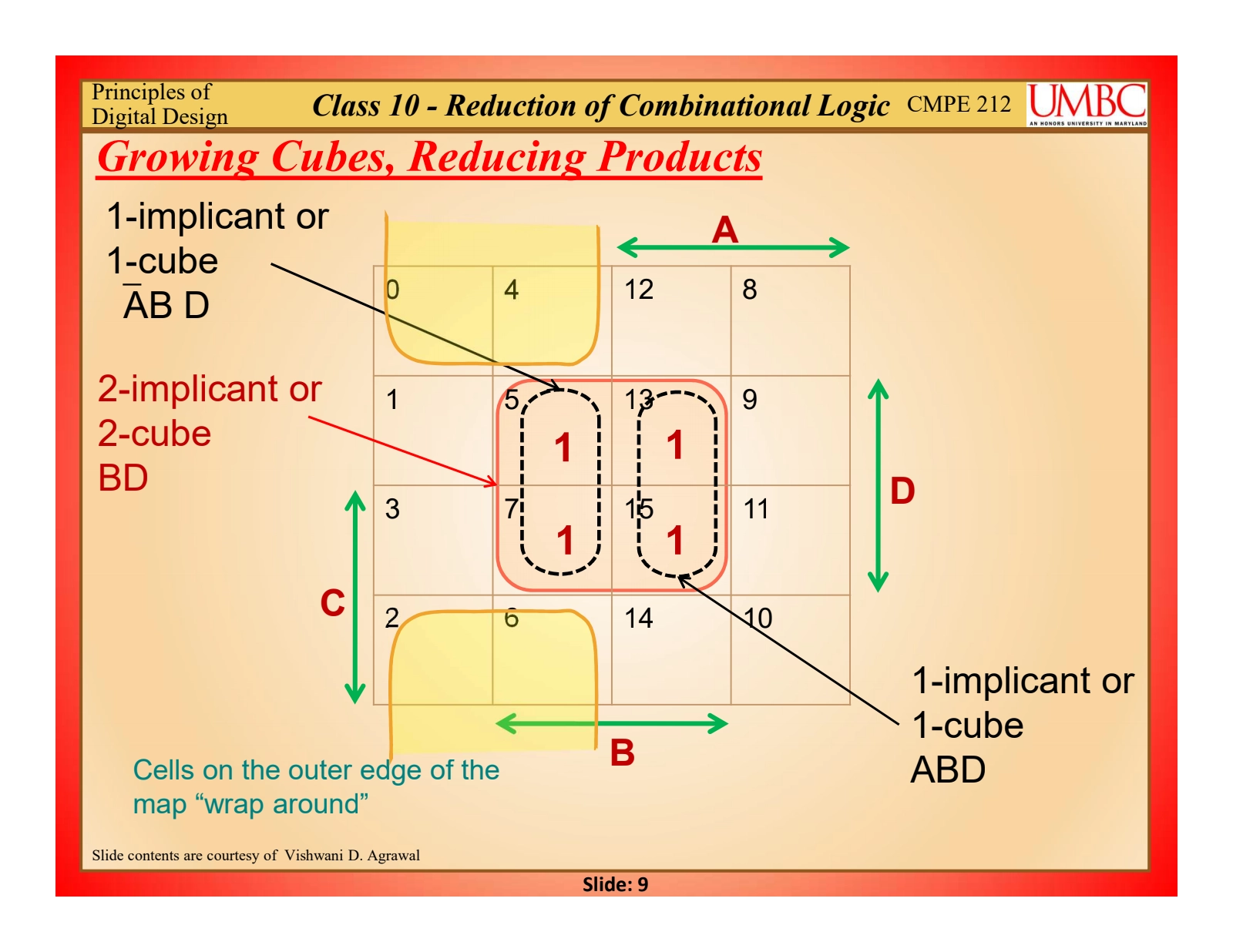

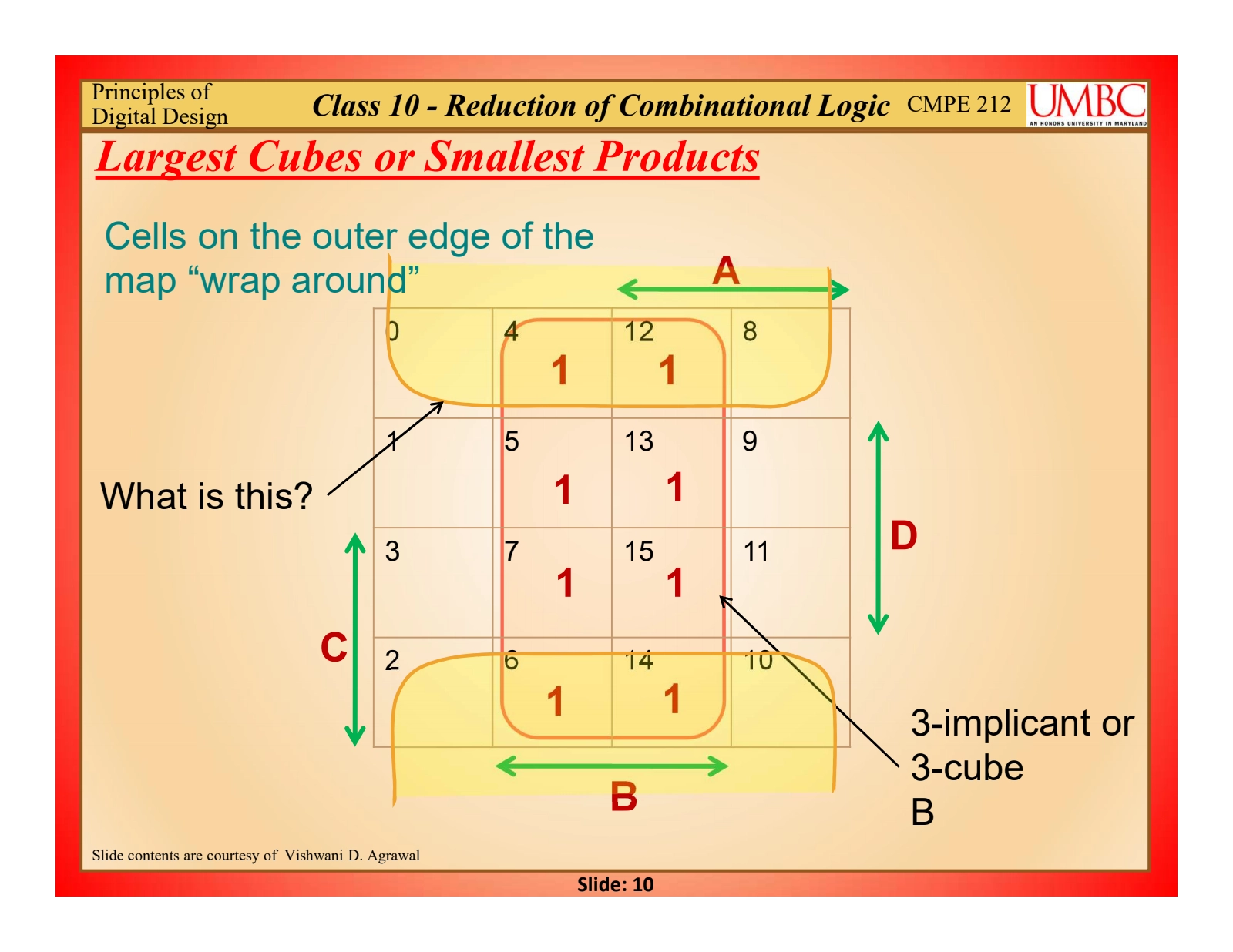

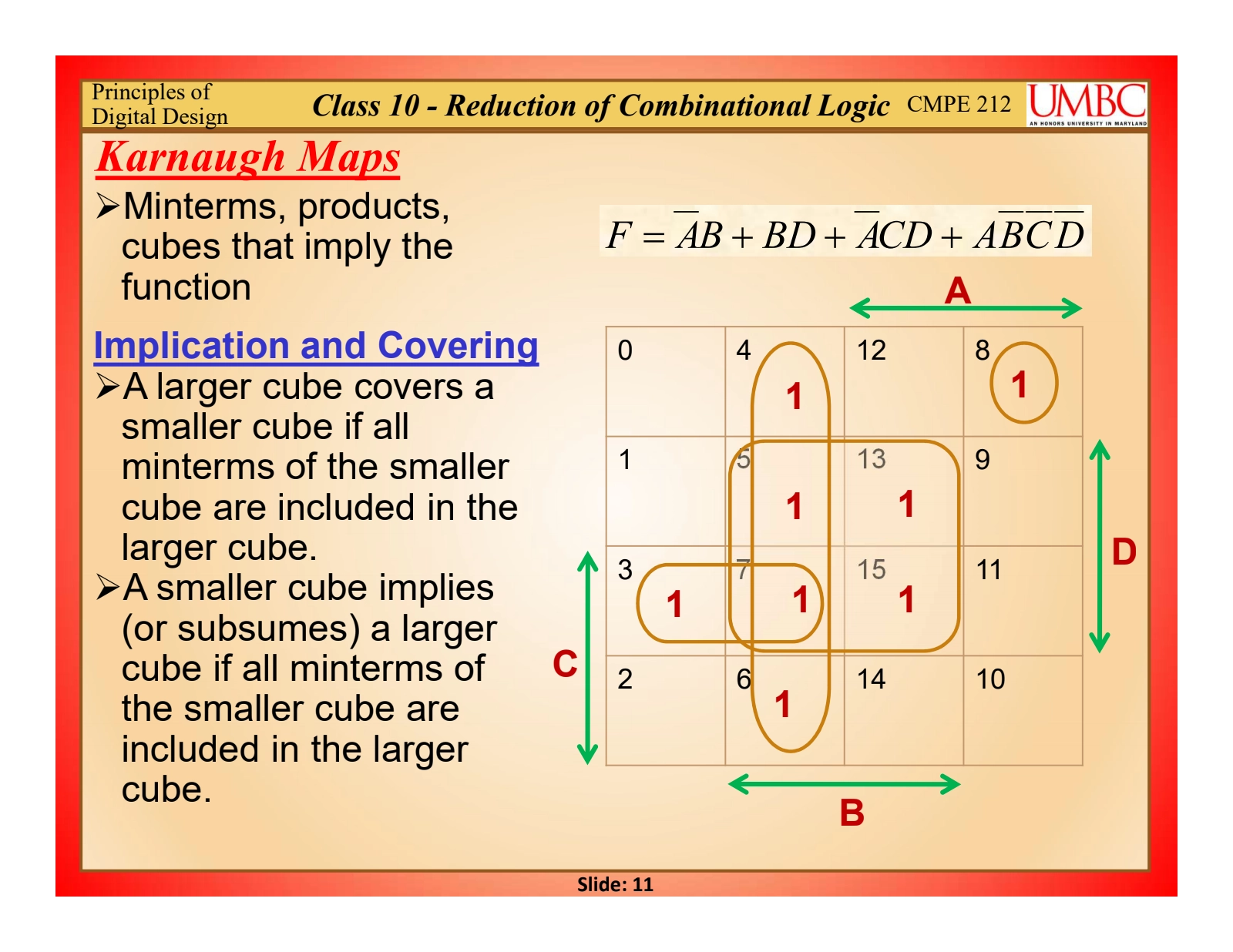

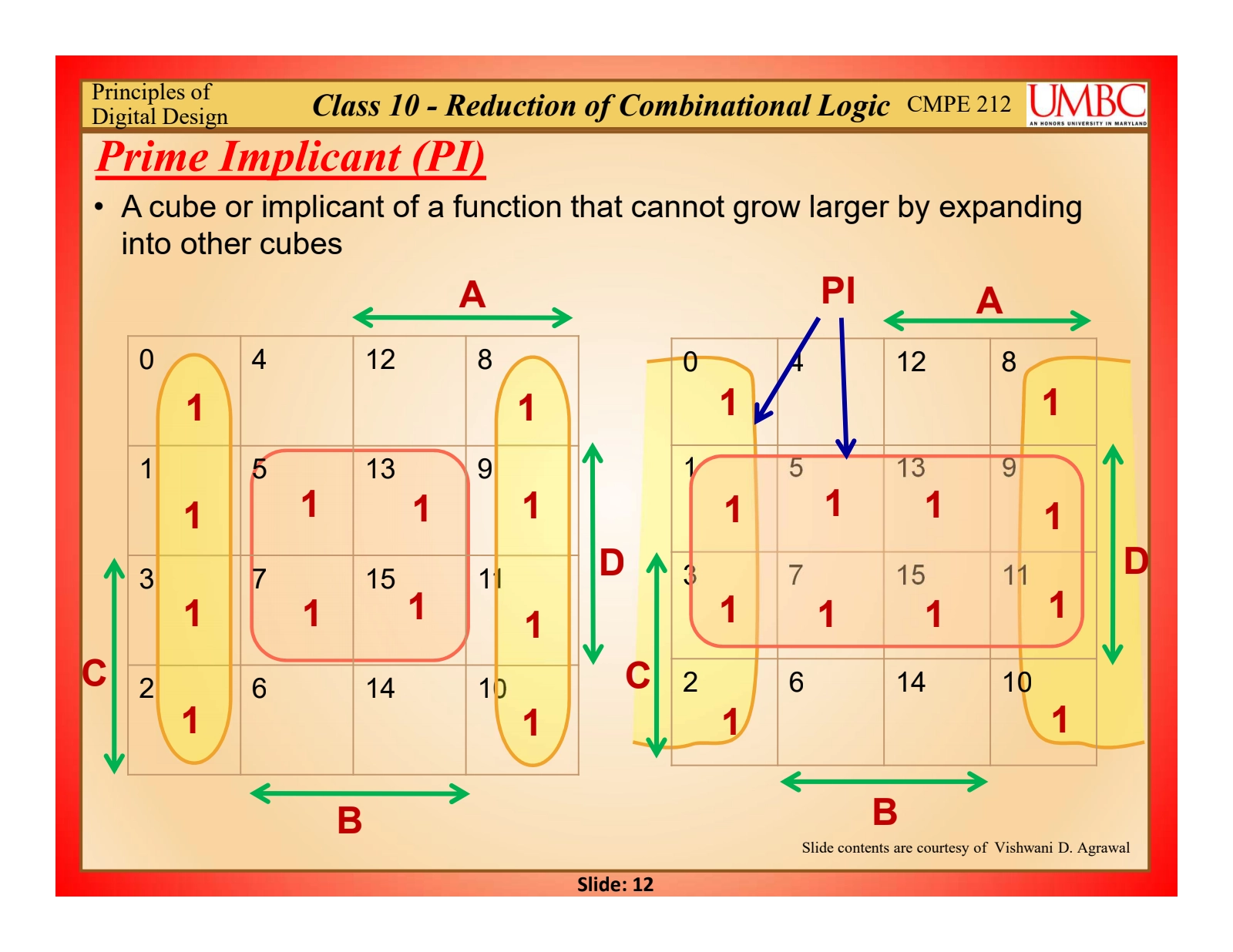

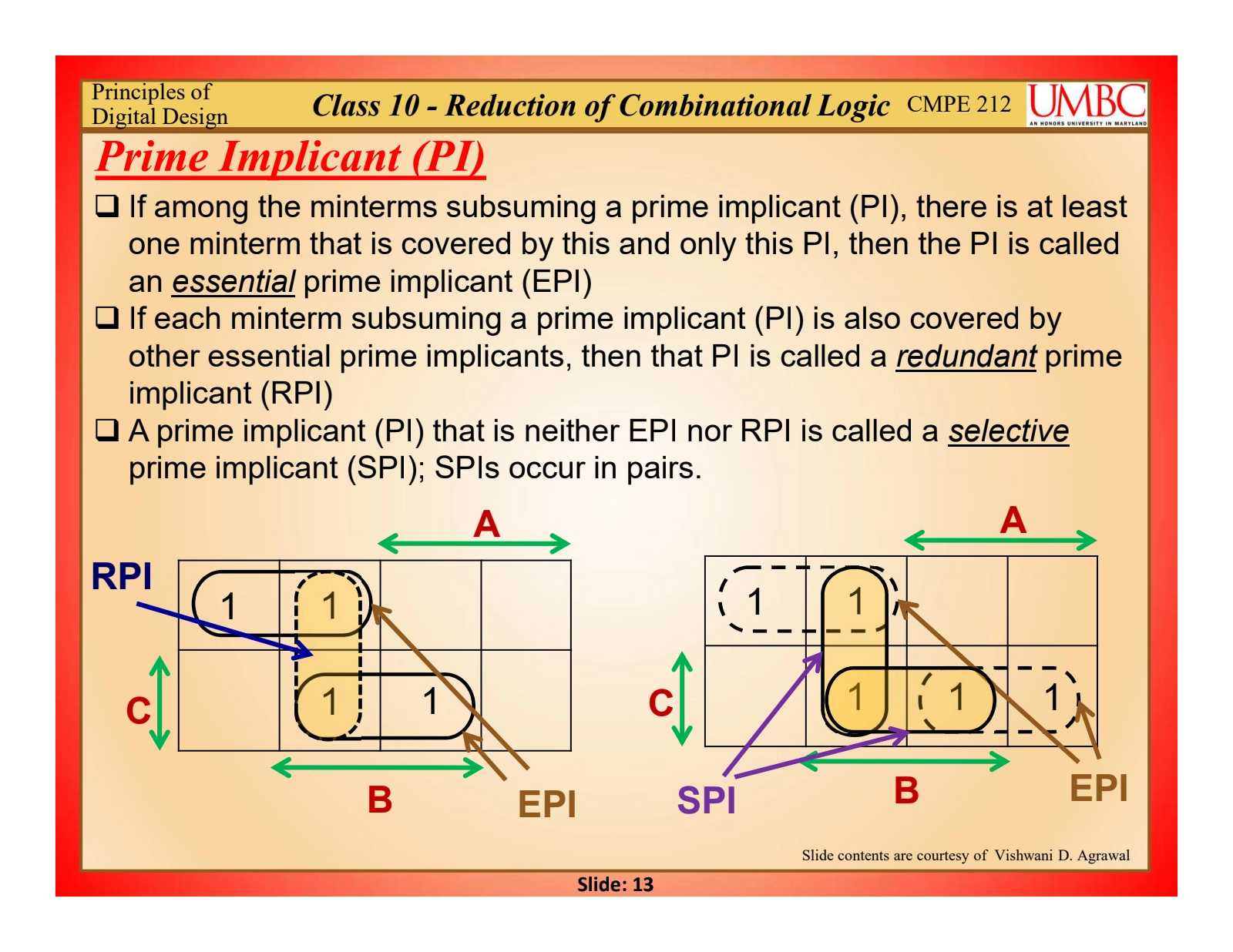

Class: 10, slide: 8-16 → Know How to do a Karnaugh-Map!!