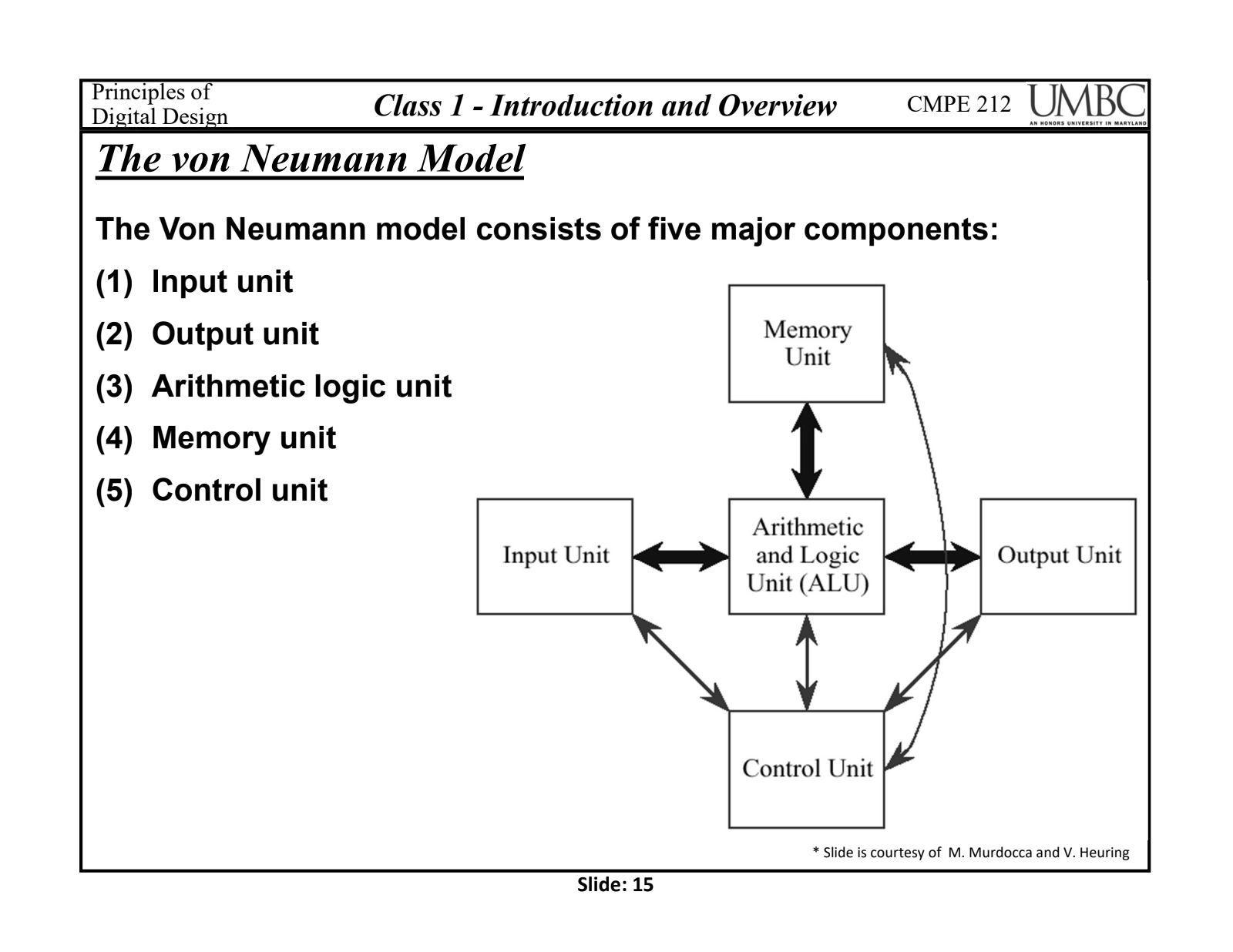

class: 1, slide: 15 → System Bus Model

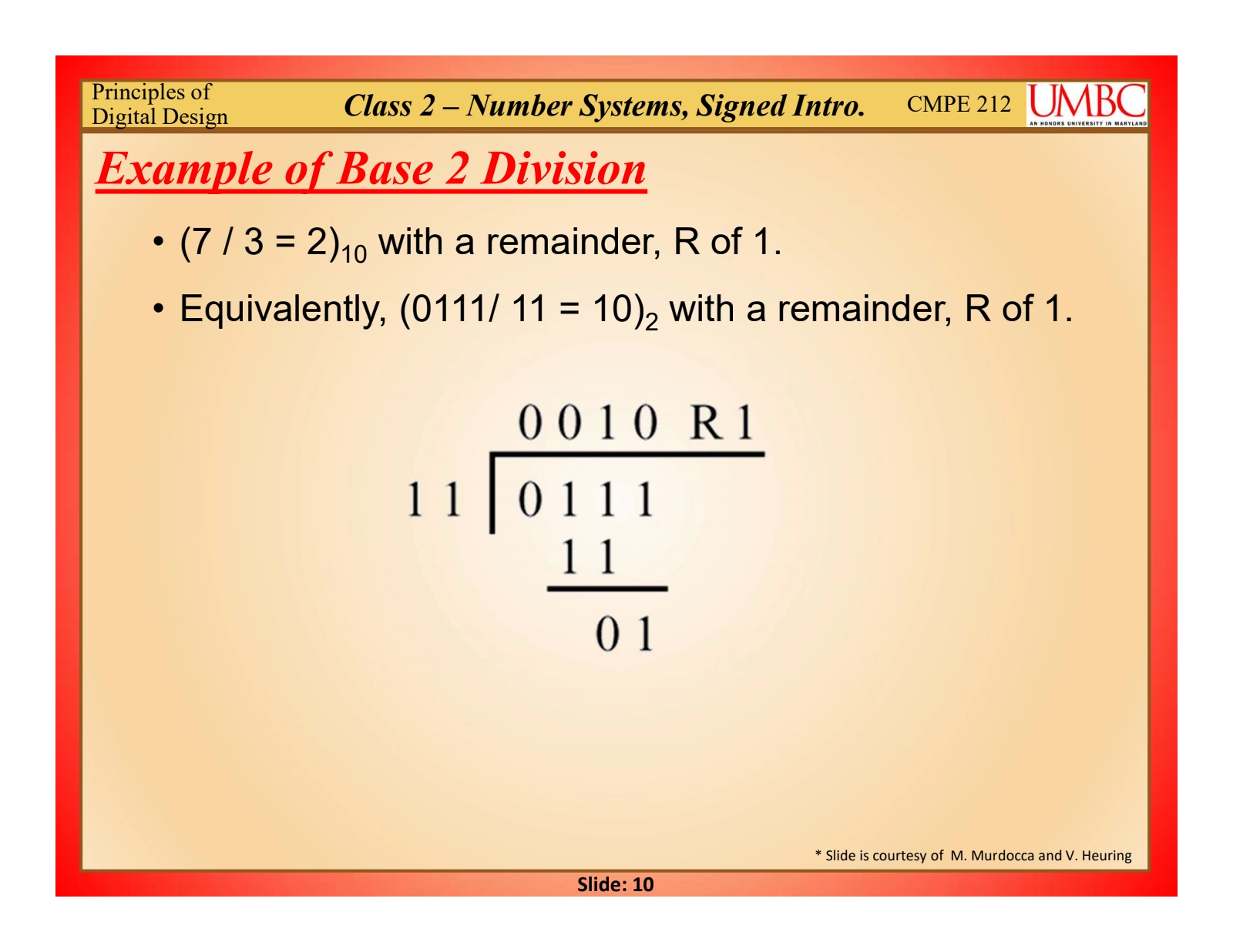

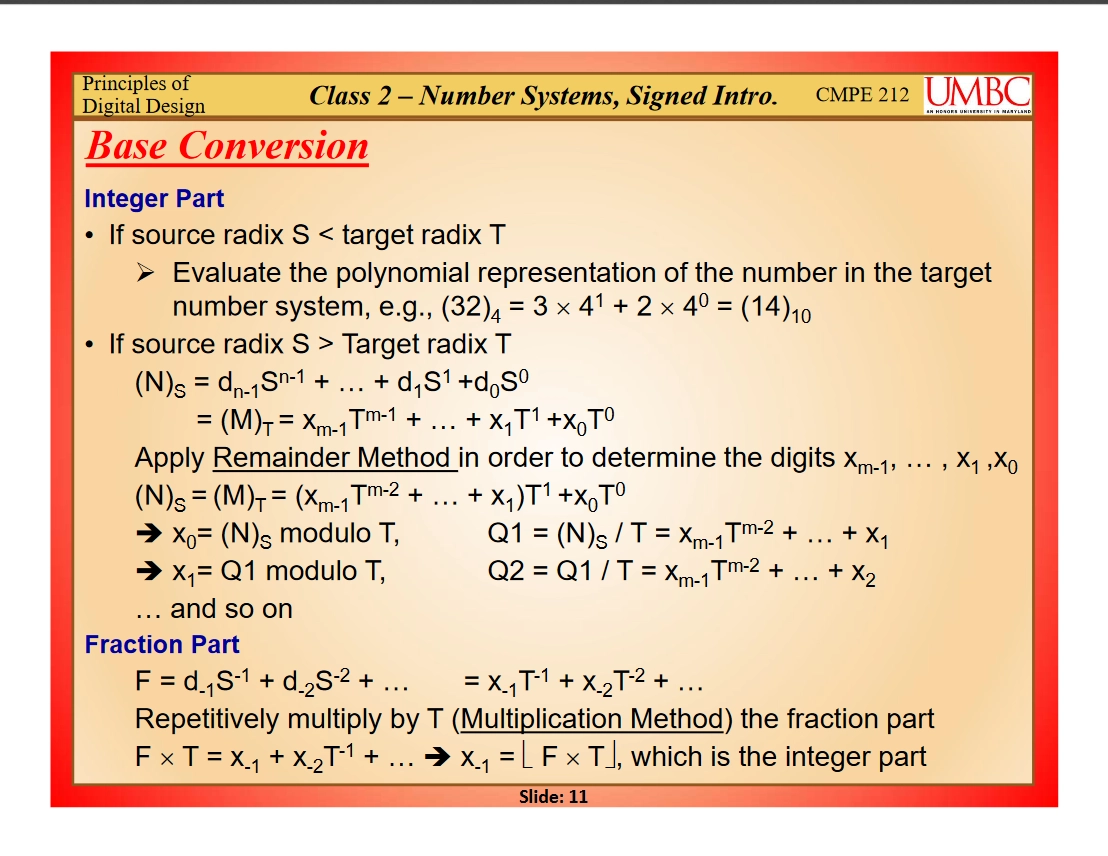

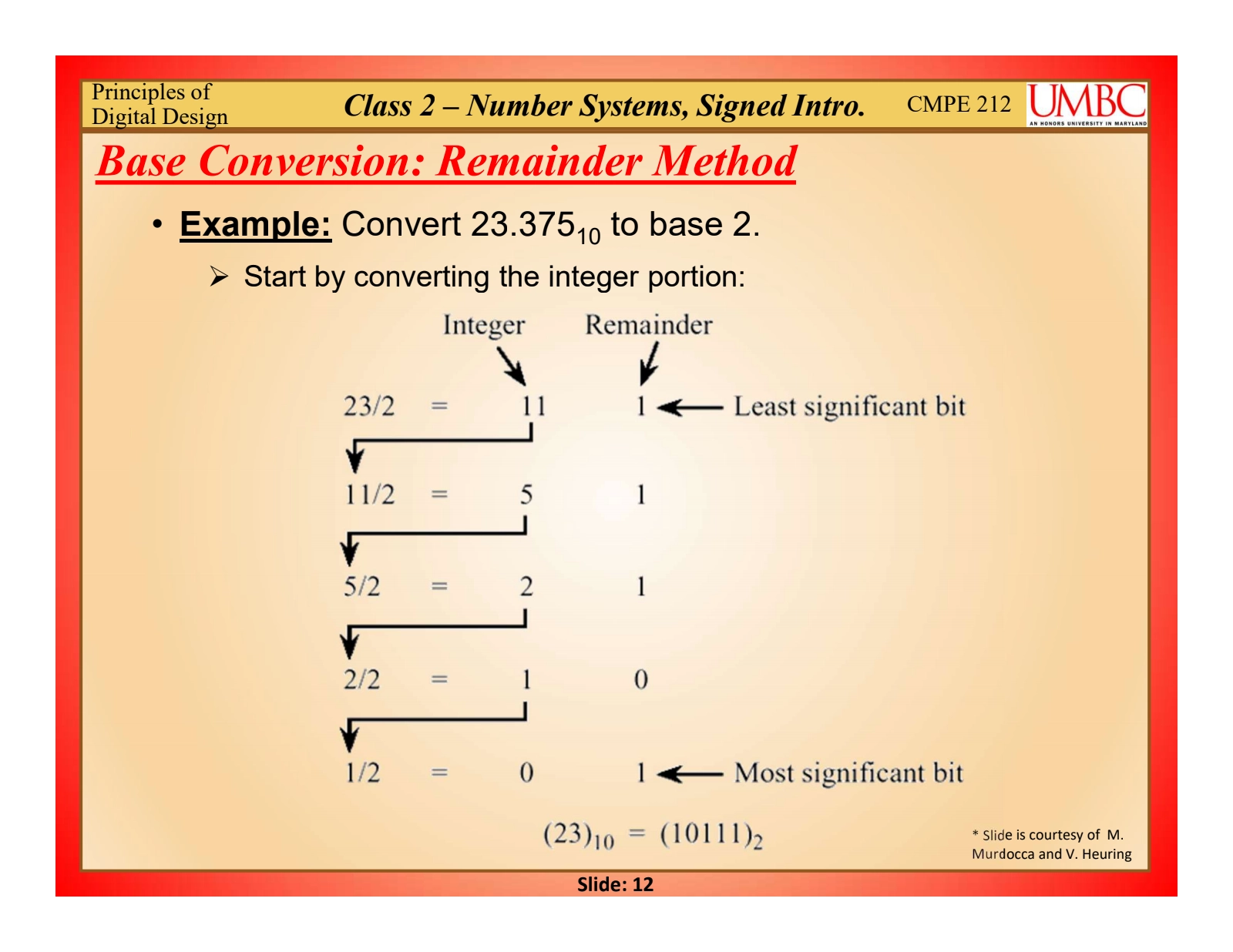

class: 2, slide: 10-12 → Converting Base 10 to Base 2

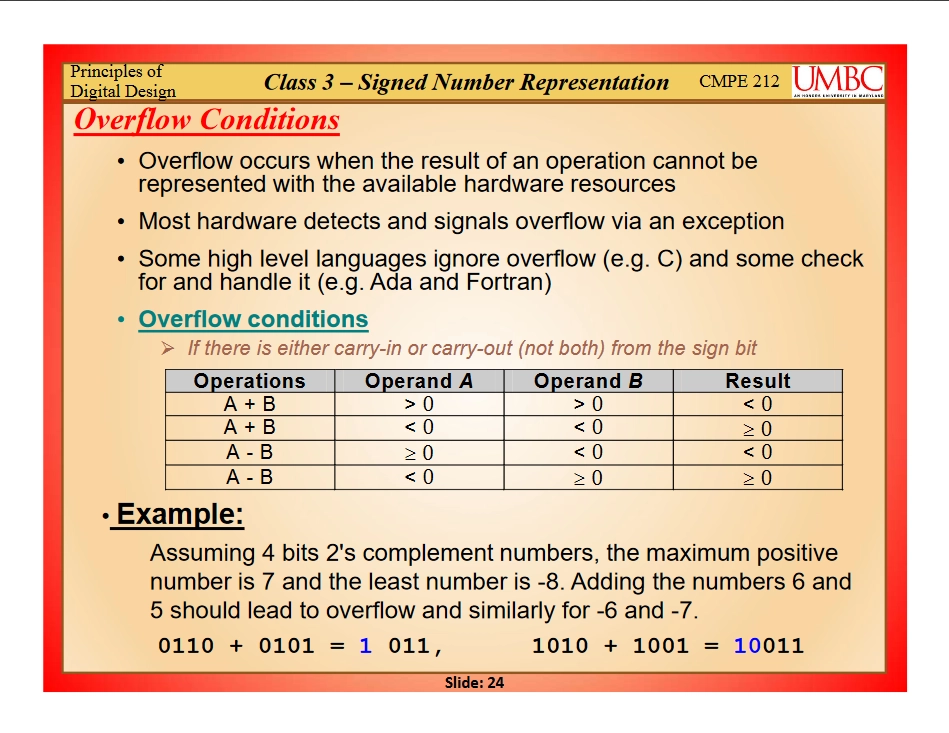

class: 3, slide: 11 → Two's Compliment Overflow

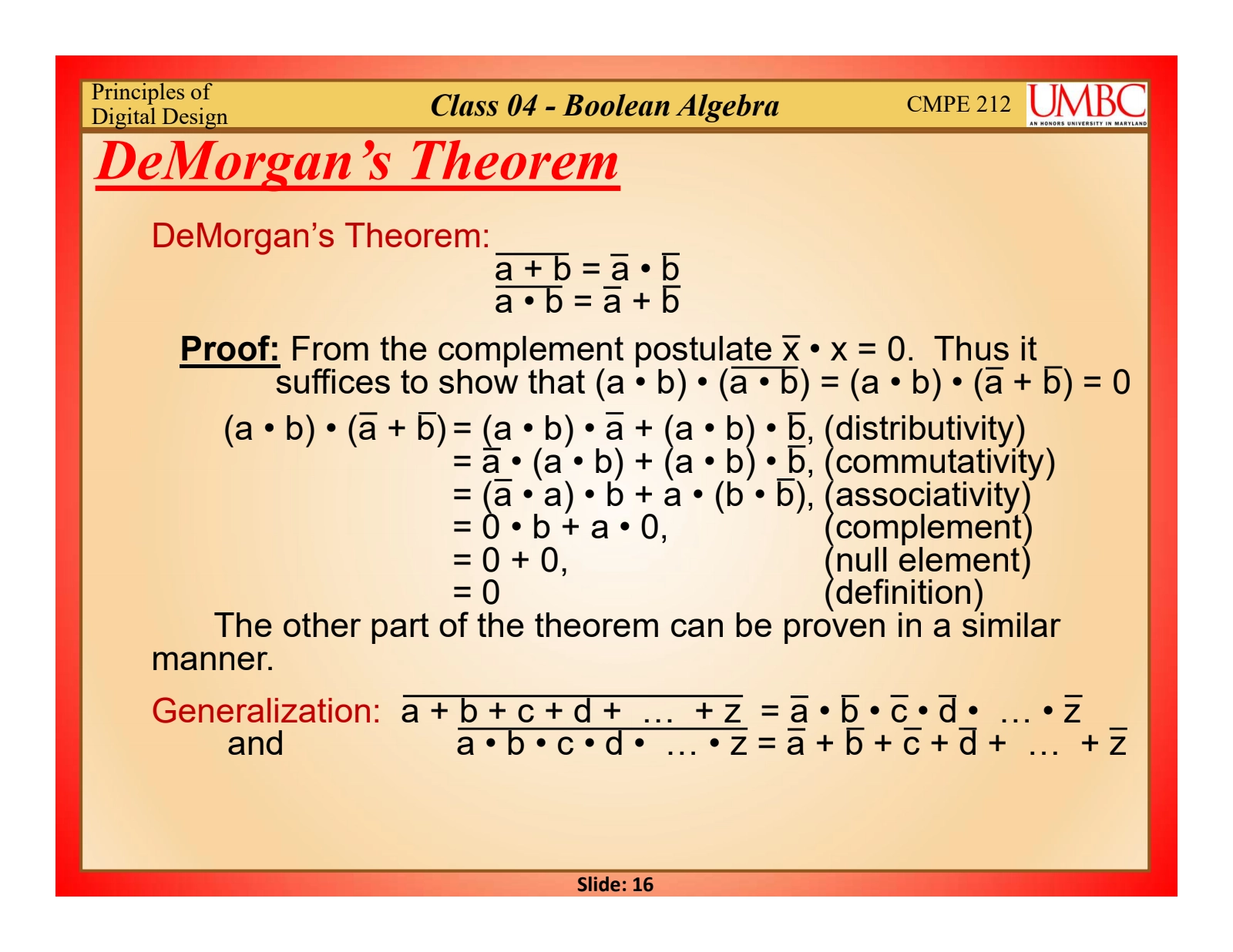

class: 4, slide: 16 → DeMorgan's Theorm

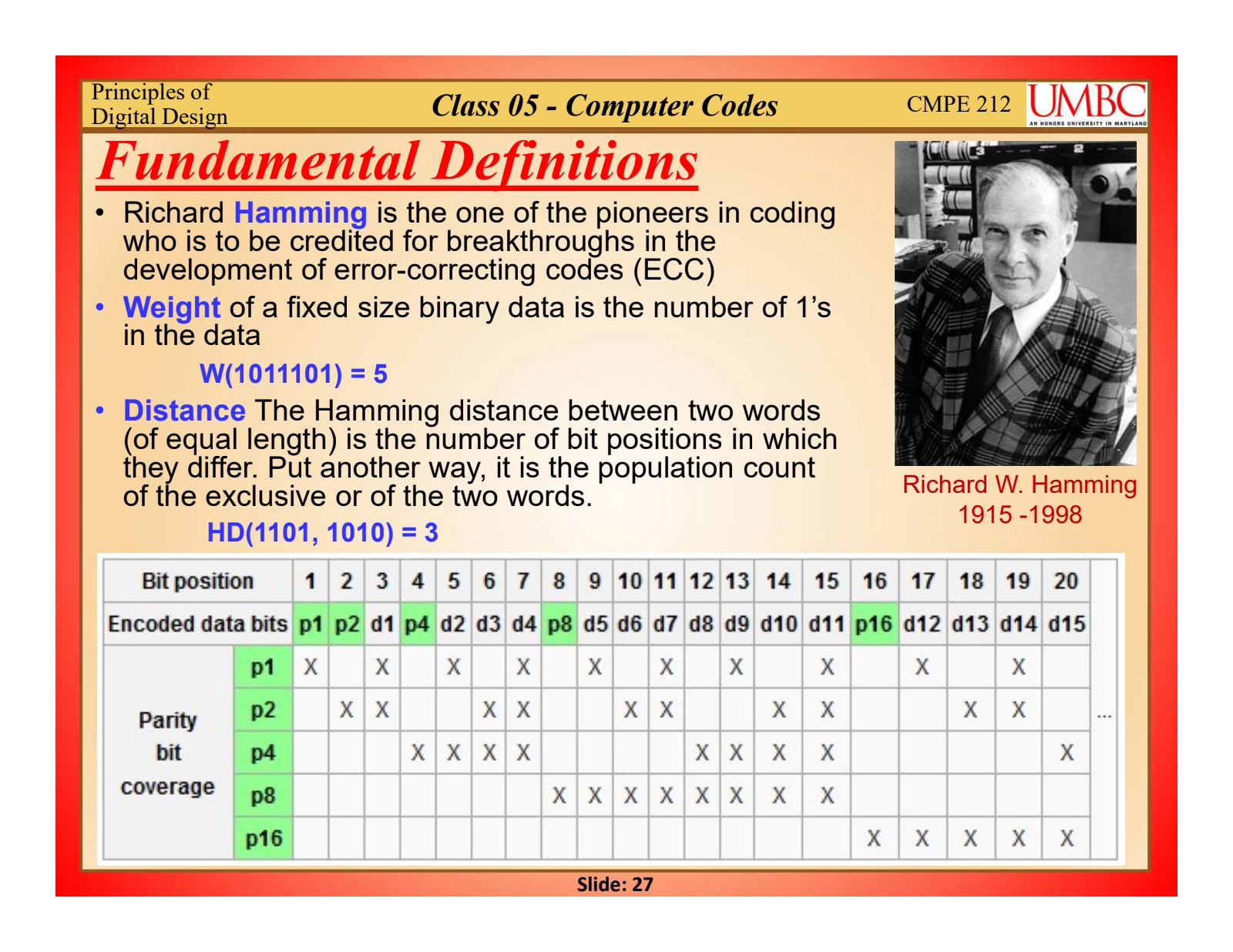

class: 5, slide: 27 → Fundamental SECDED definitions

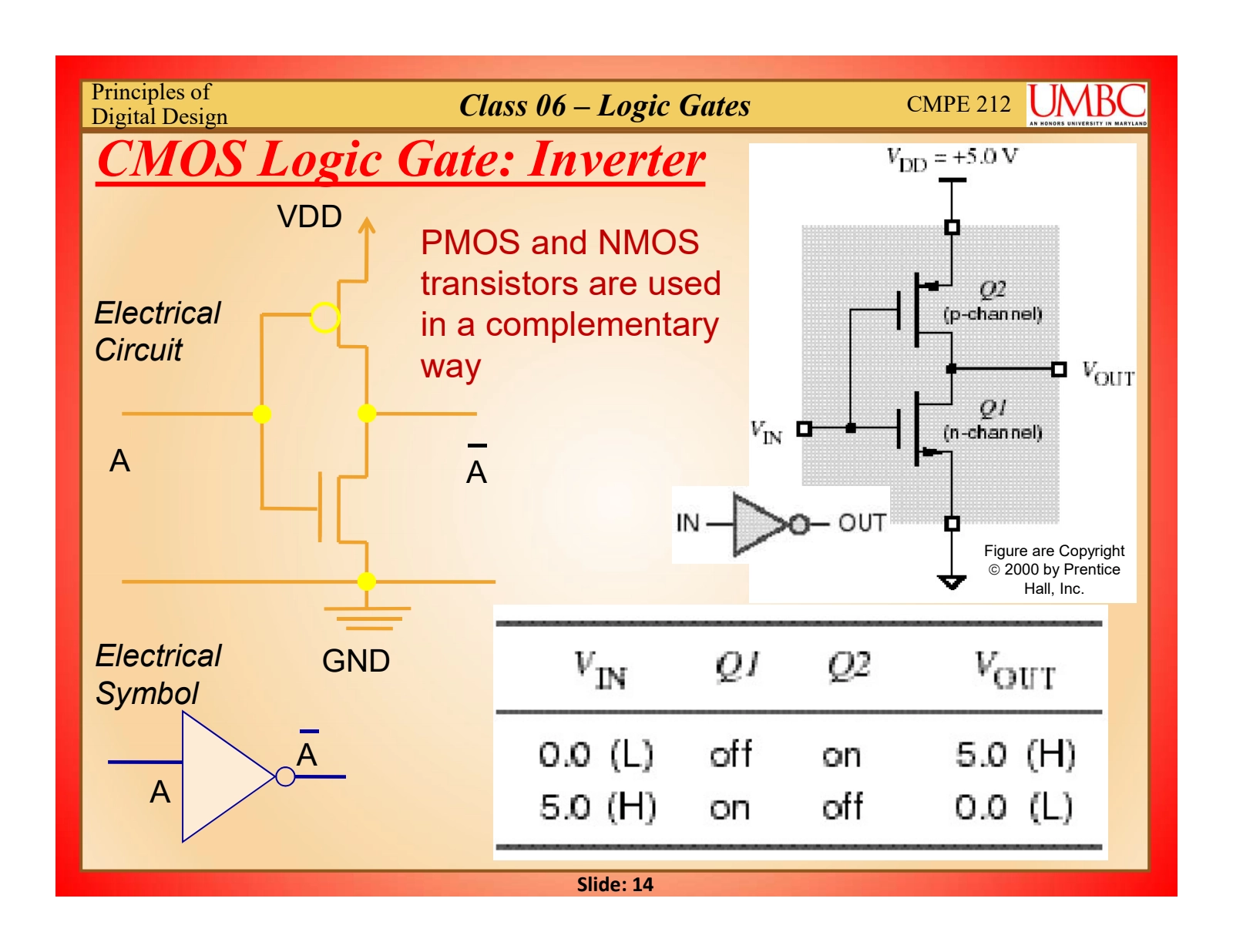

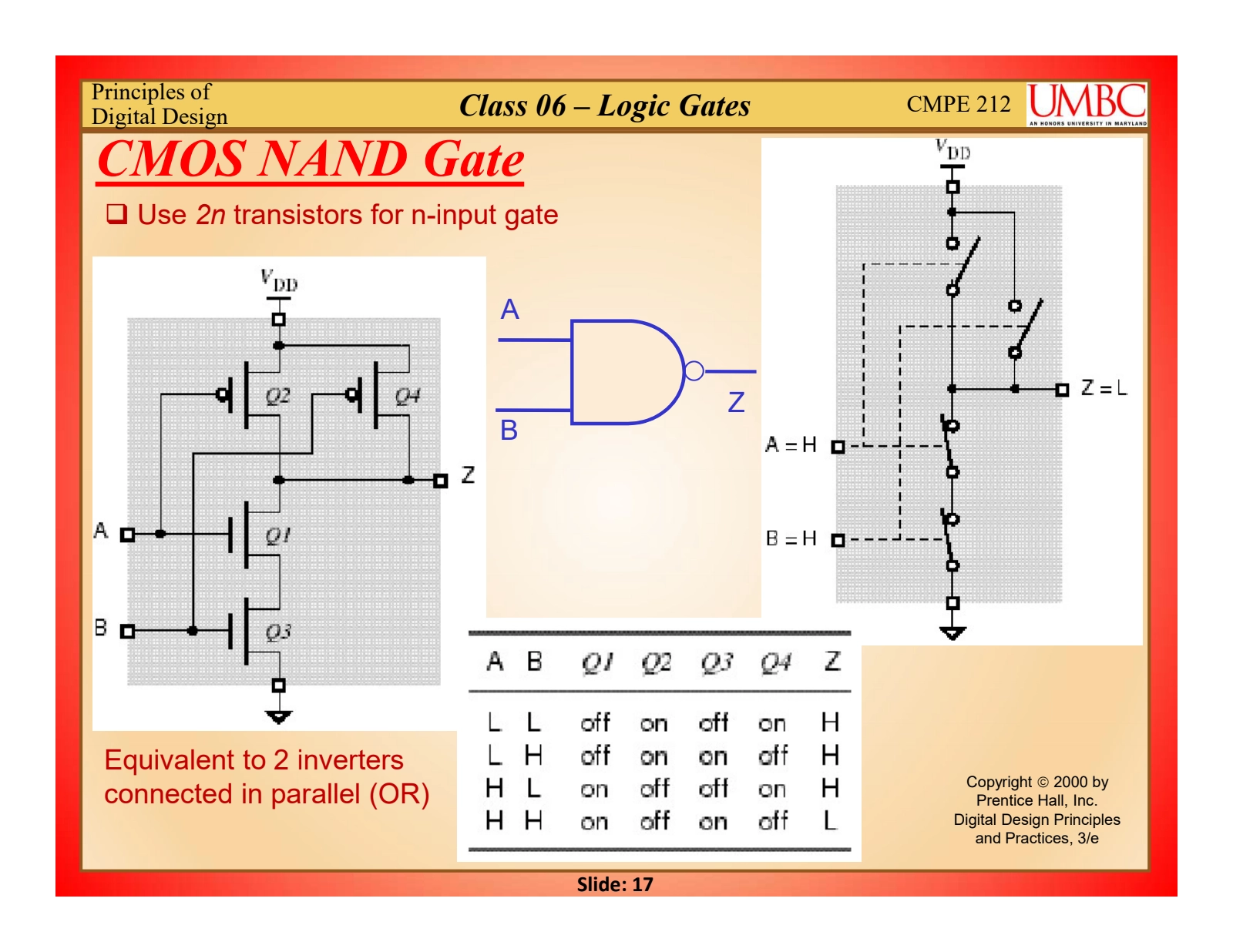

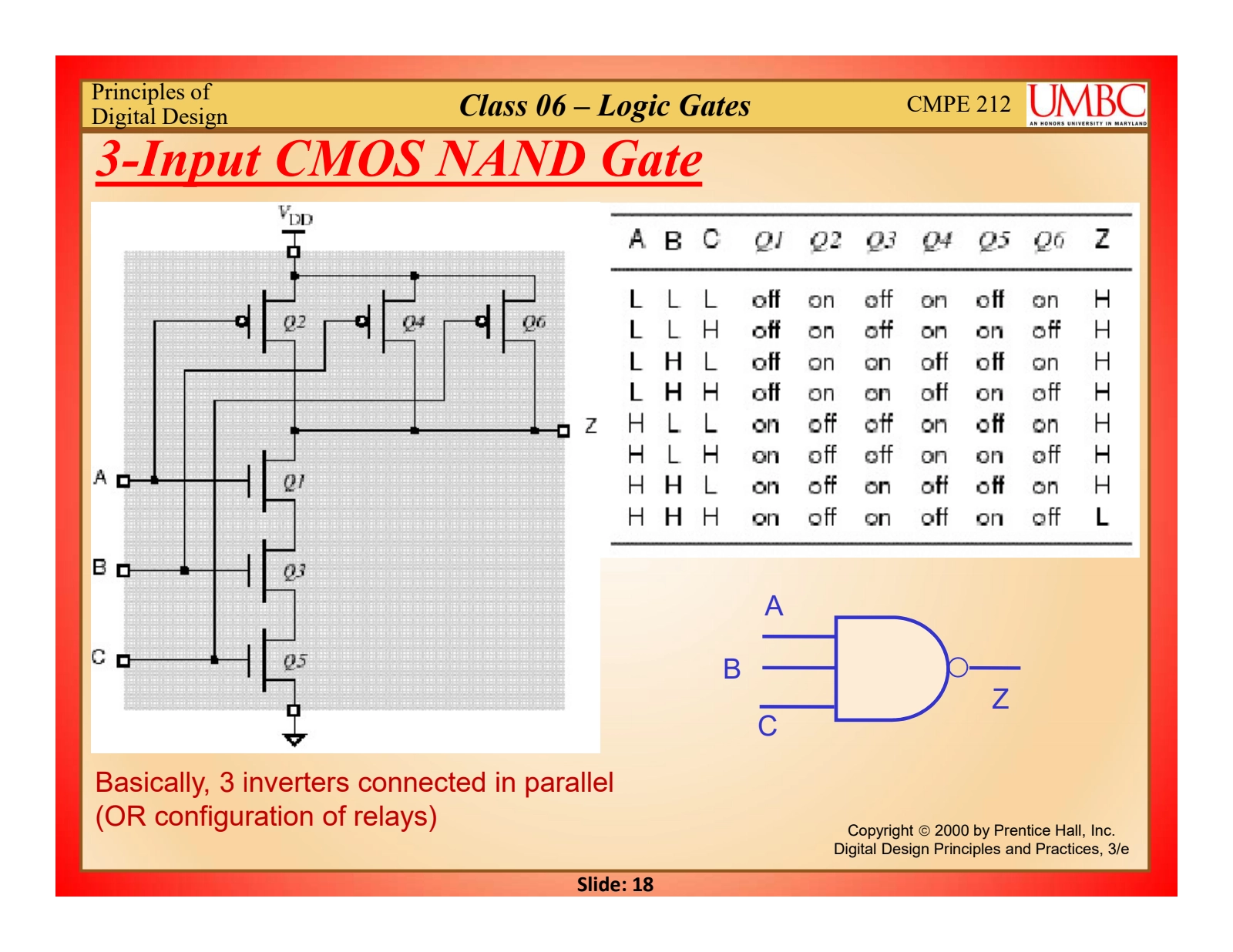

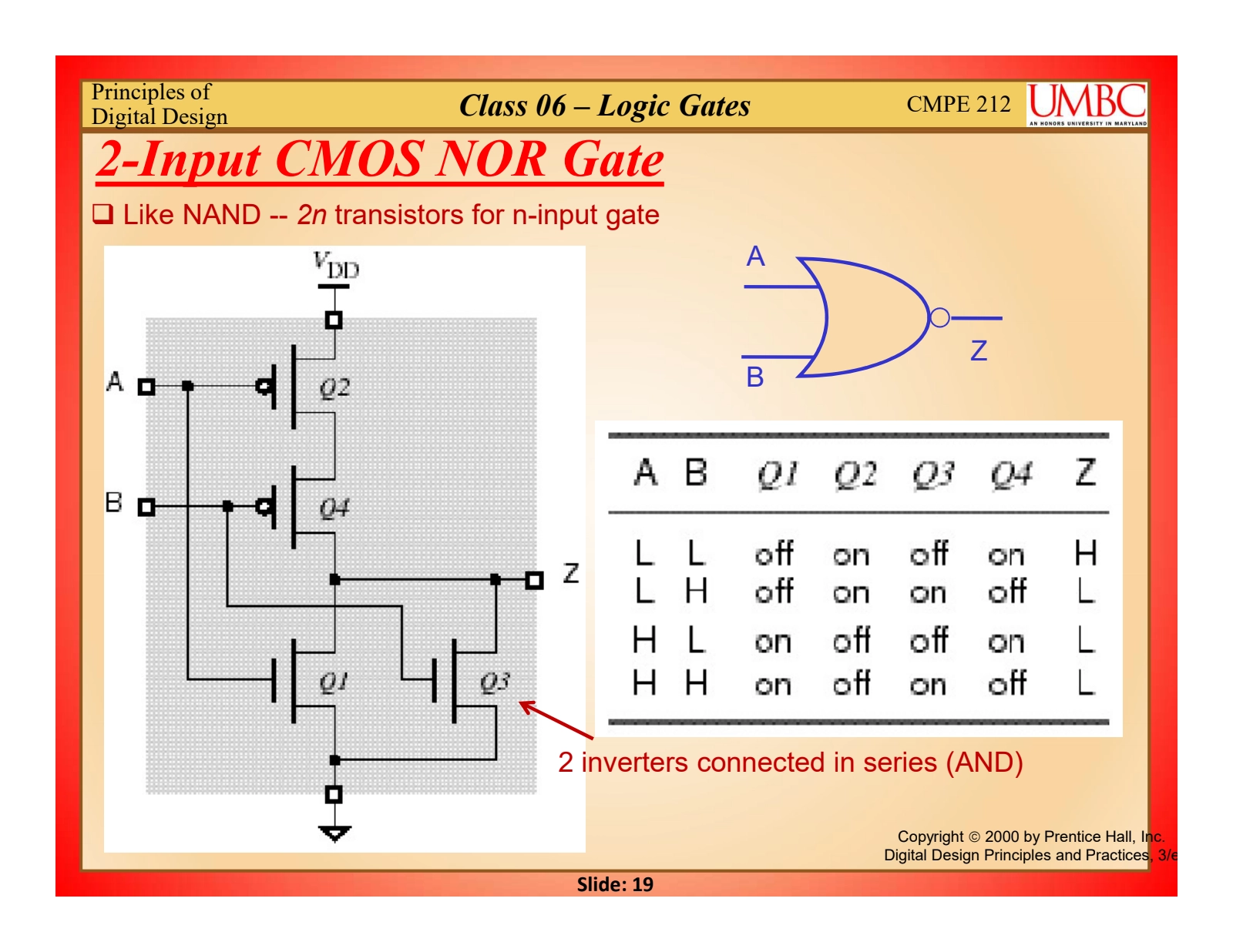

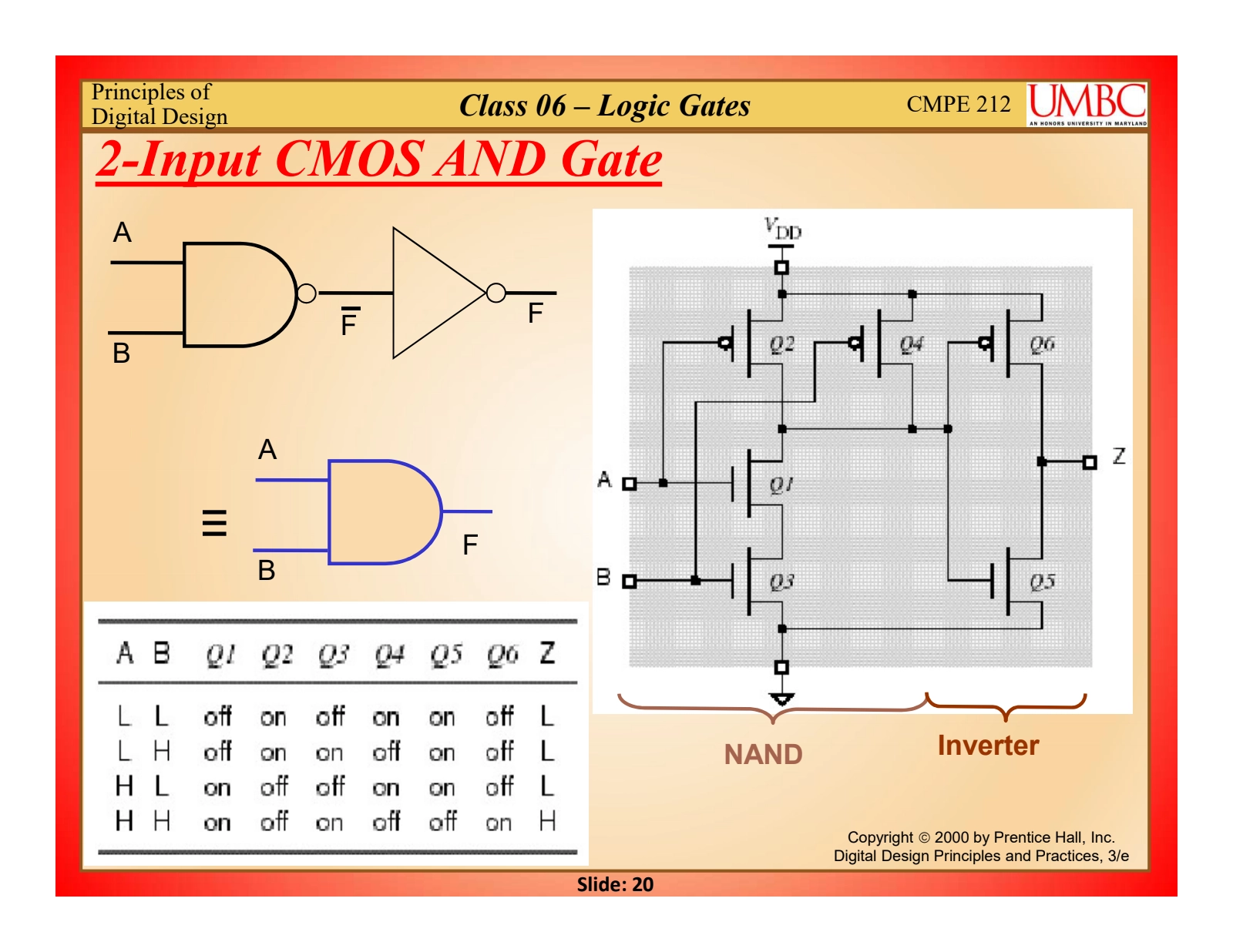

class: 6, slide: 14,17-20 → Draw and explain operation of Gates

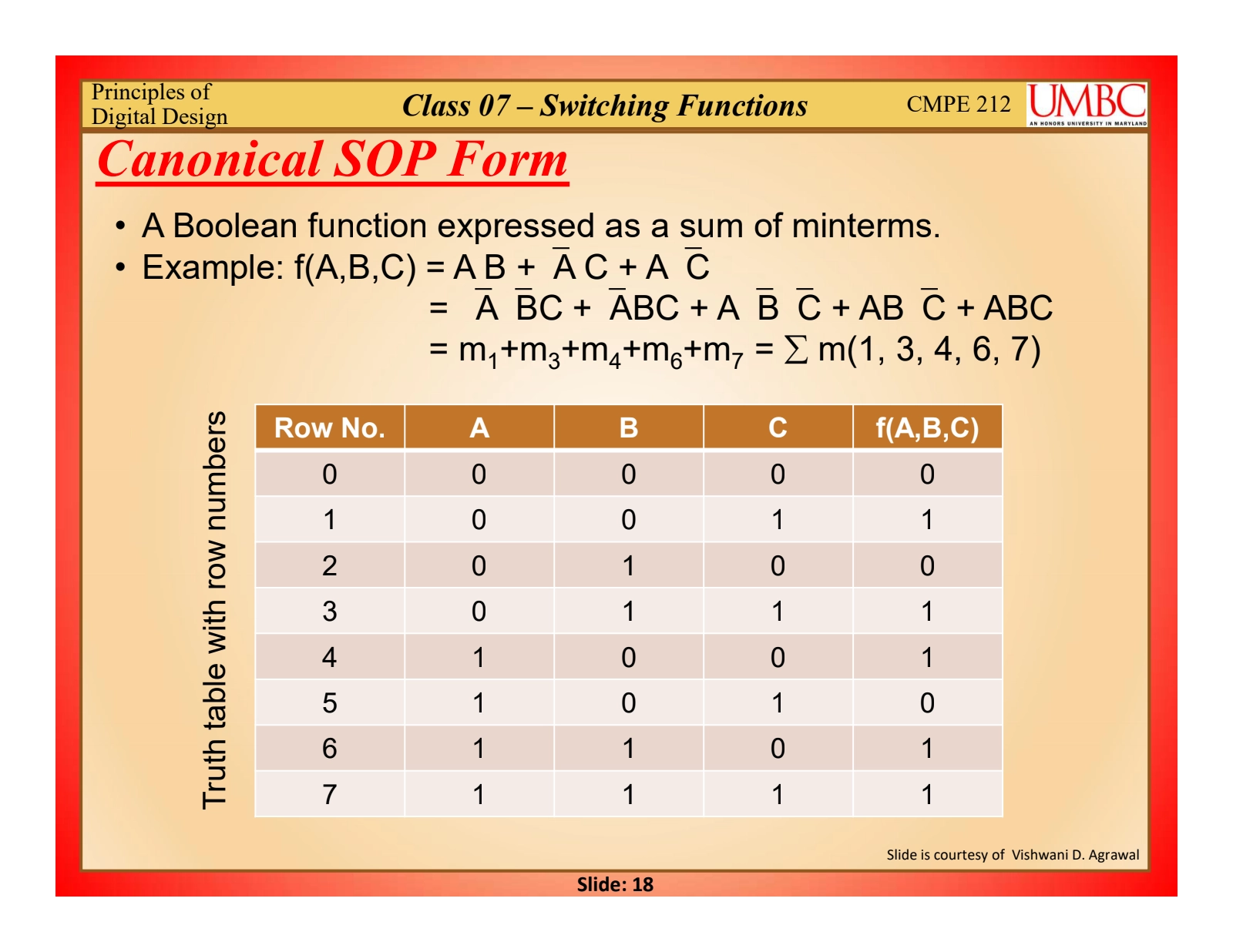

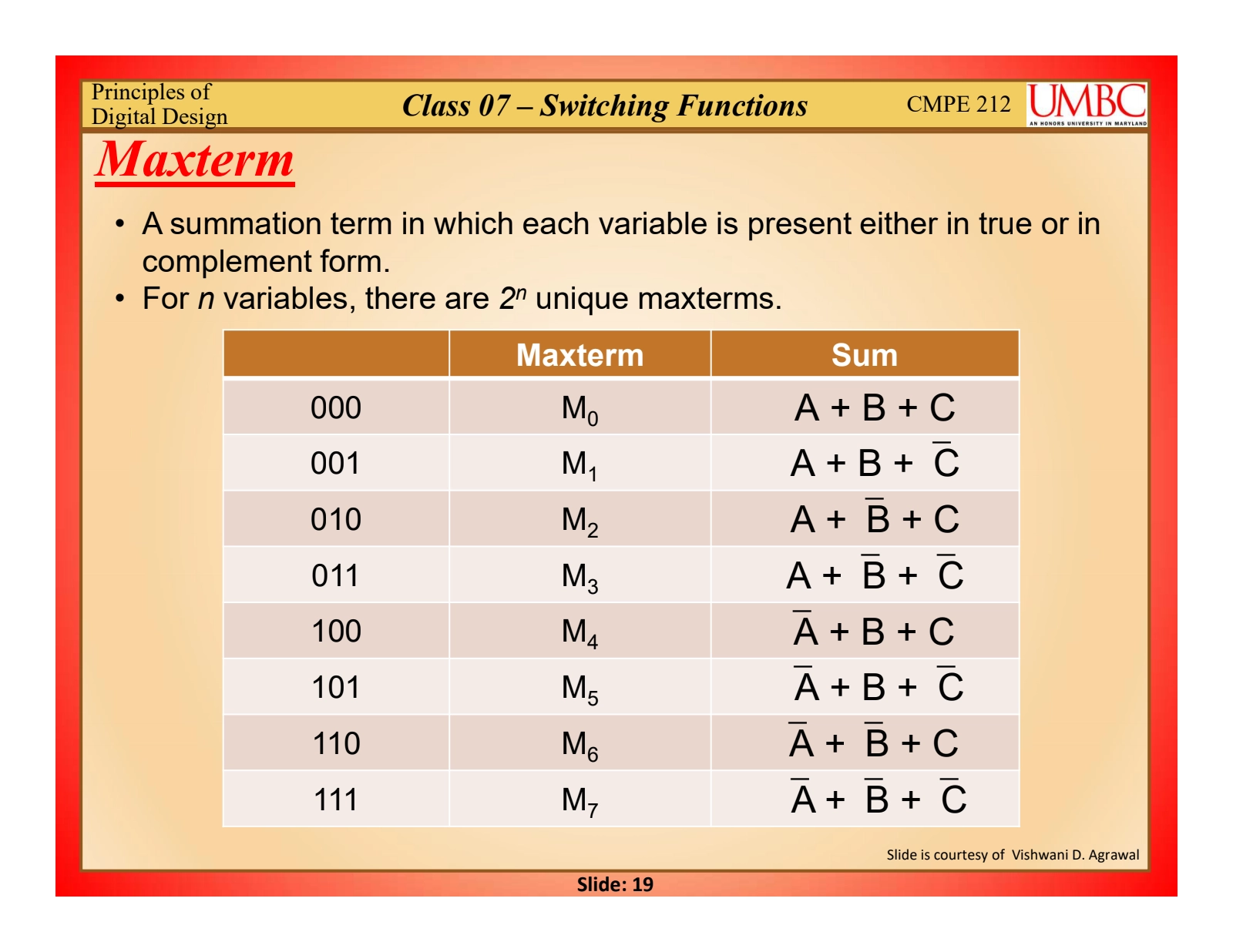

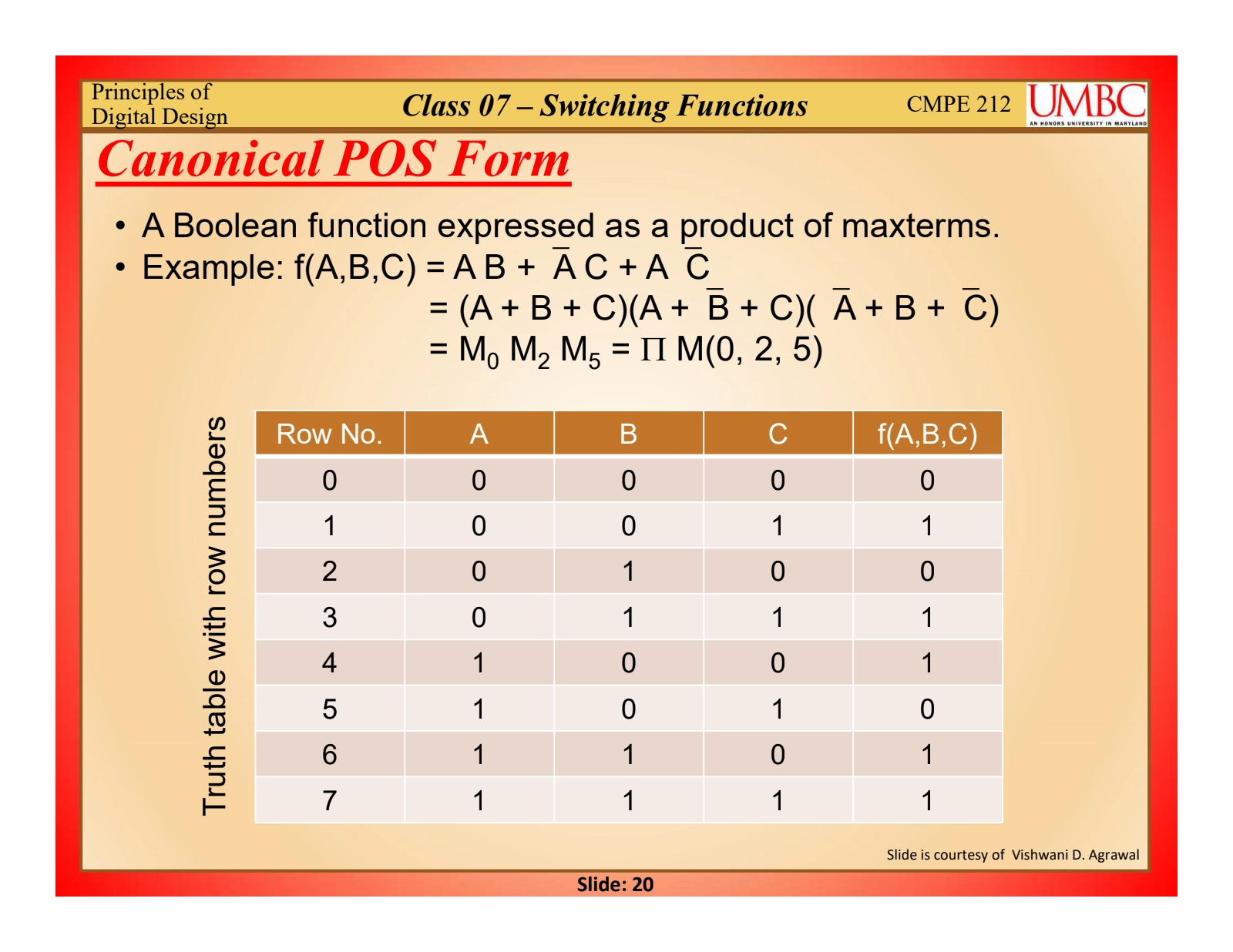

class: 7, slide: 18-20 → Canonical SOP or POS from Truth Tables

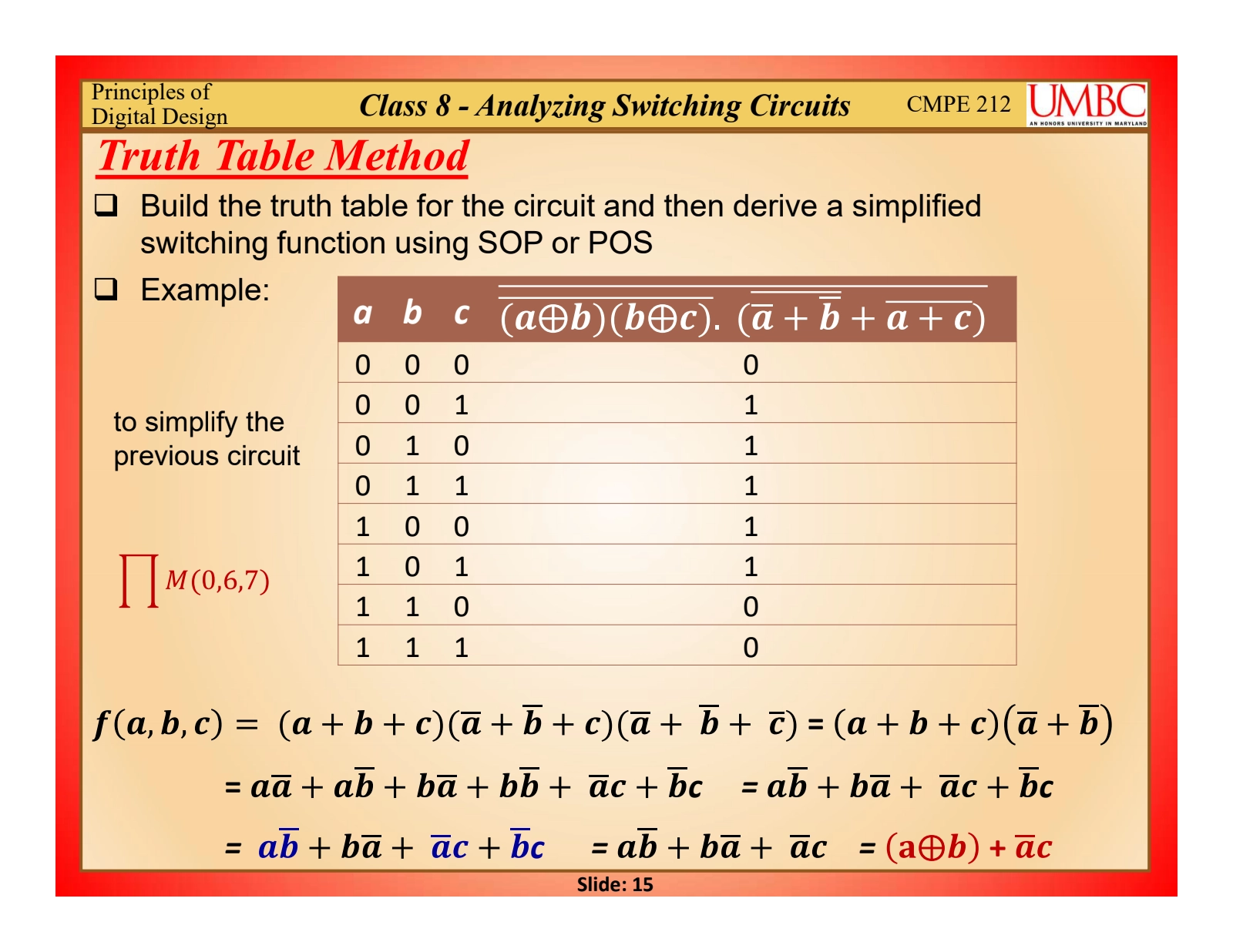

class: 8, slide: 15 → Construct a circuit from a Truth Table

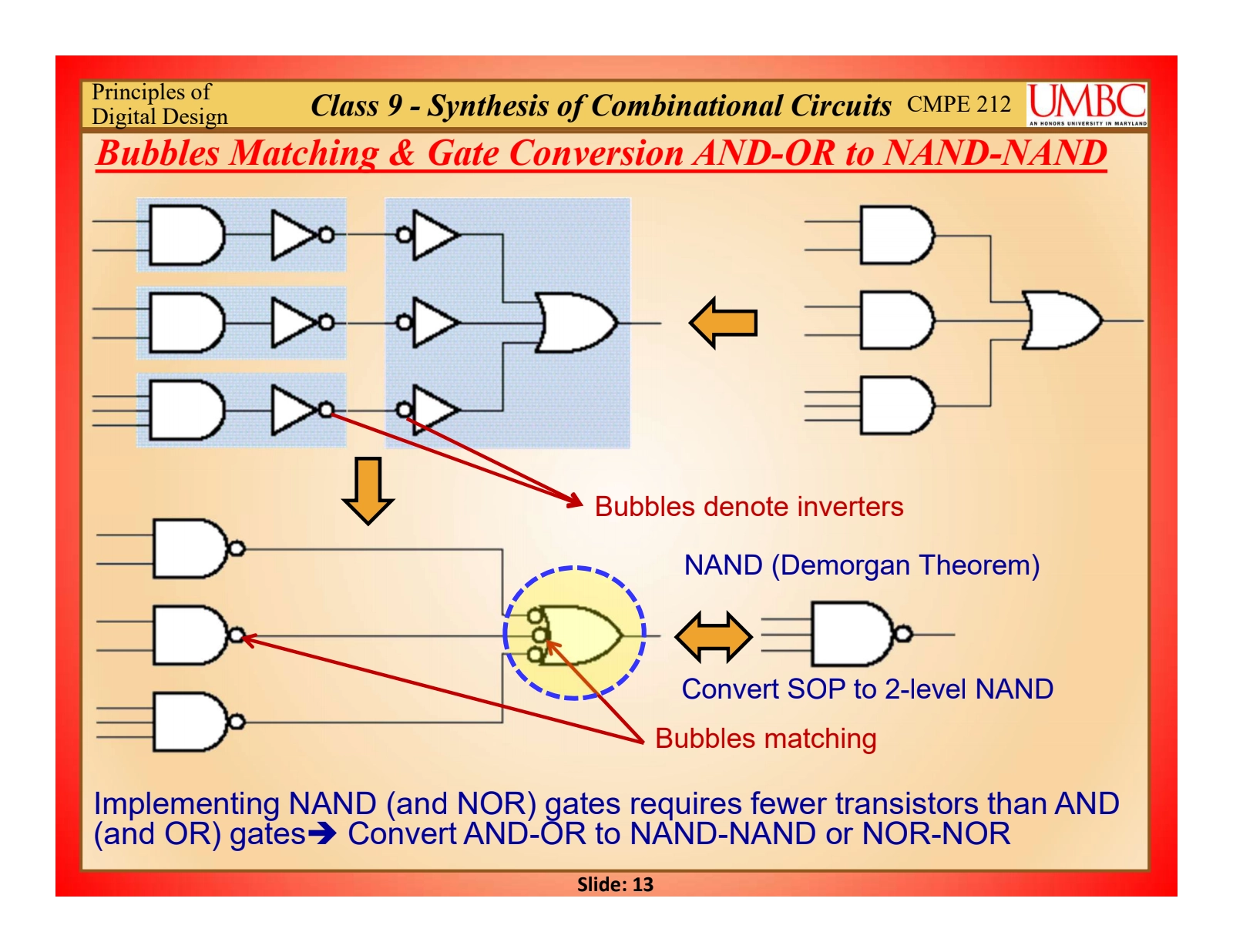

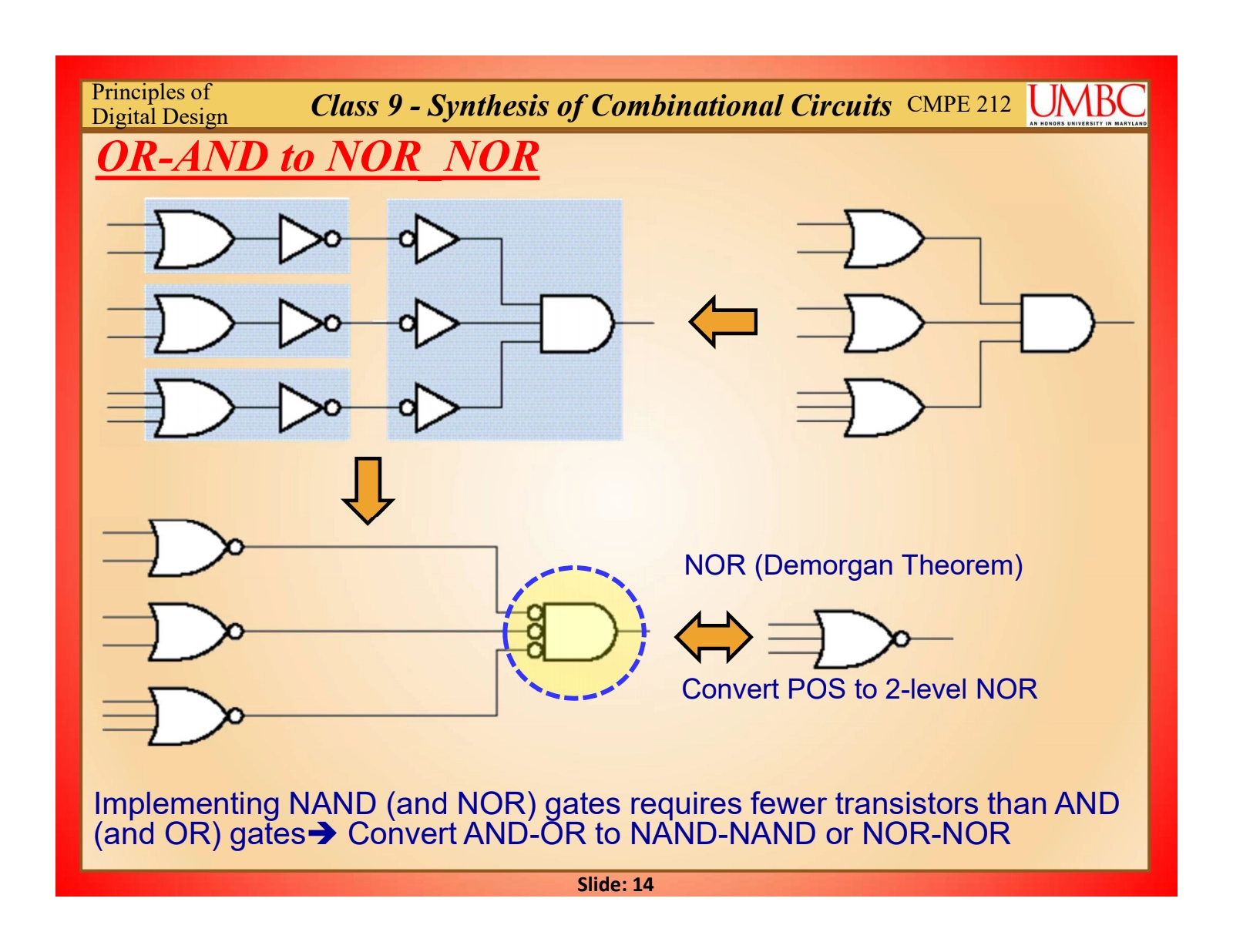

class: 9, slide: 13-14 → Bubles Matching & Gate Conversion

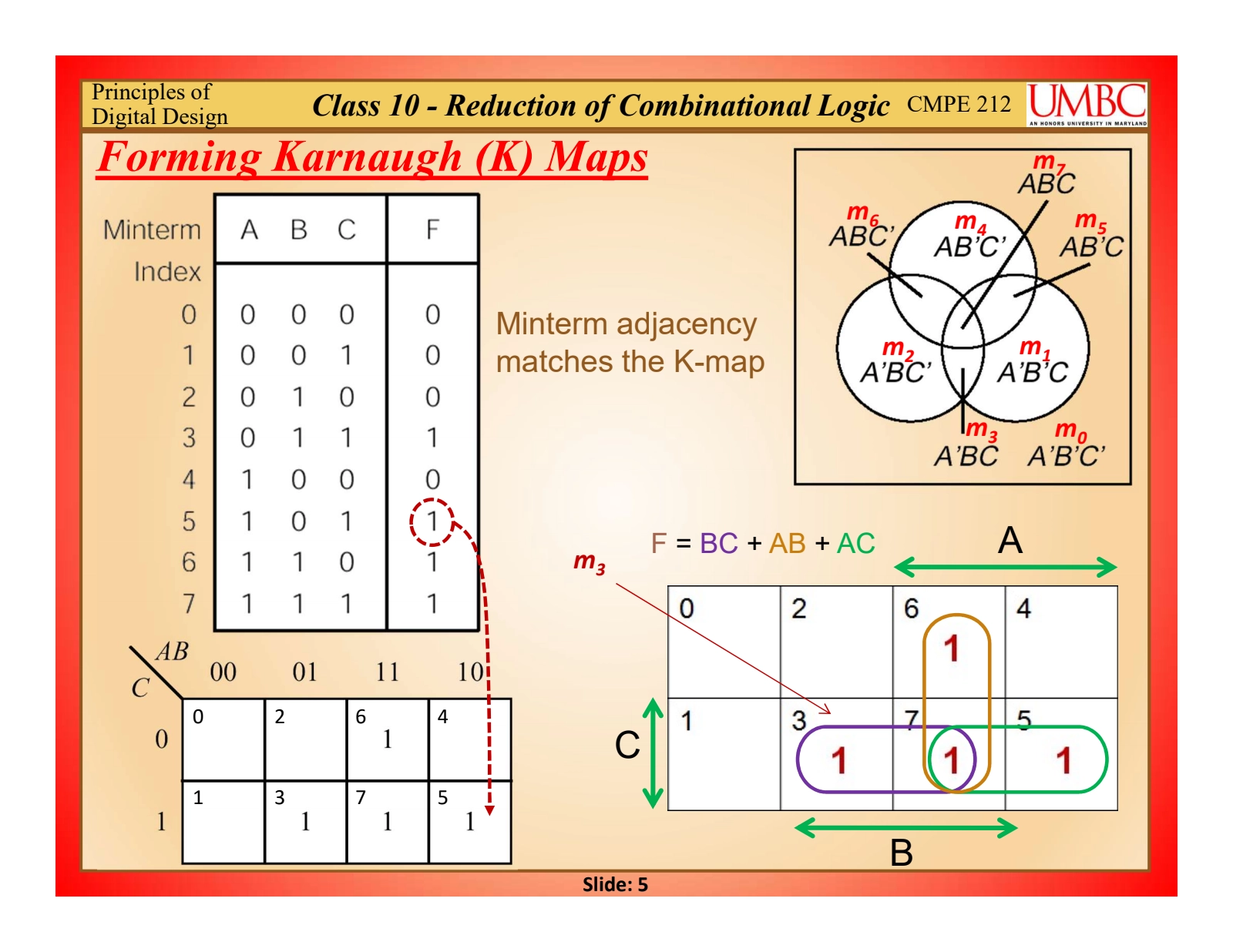

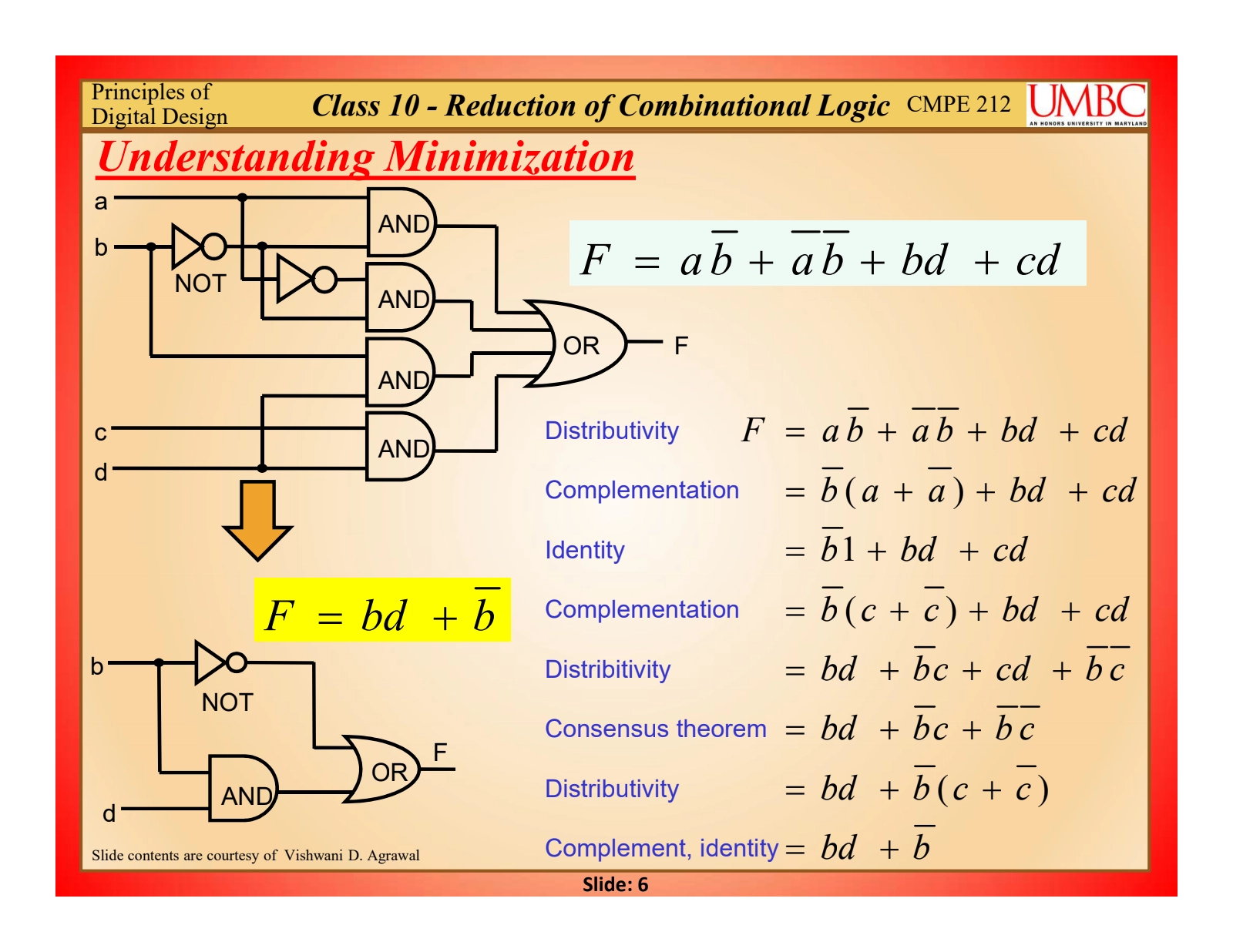

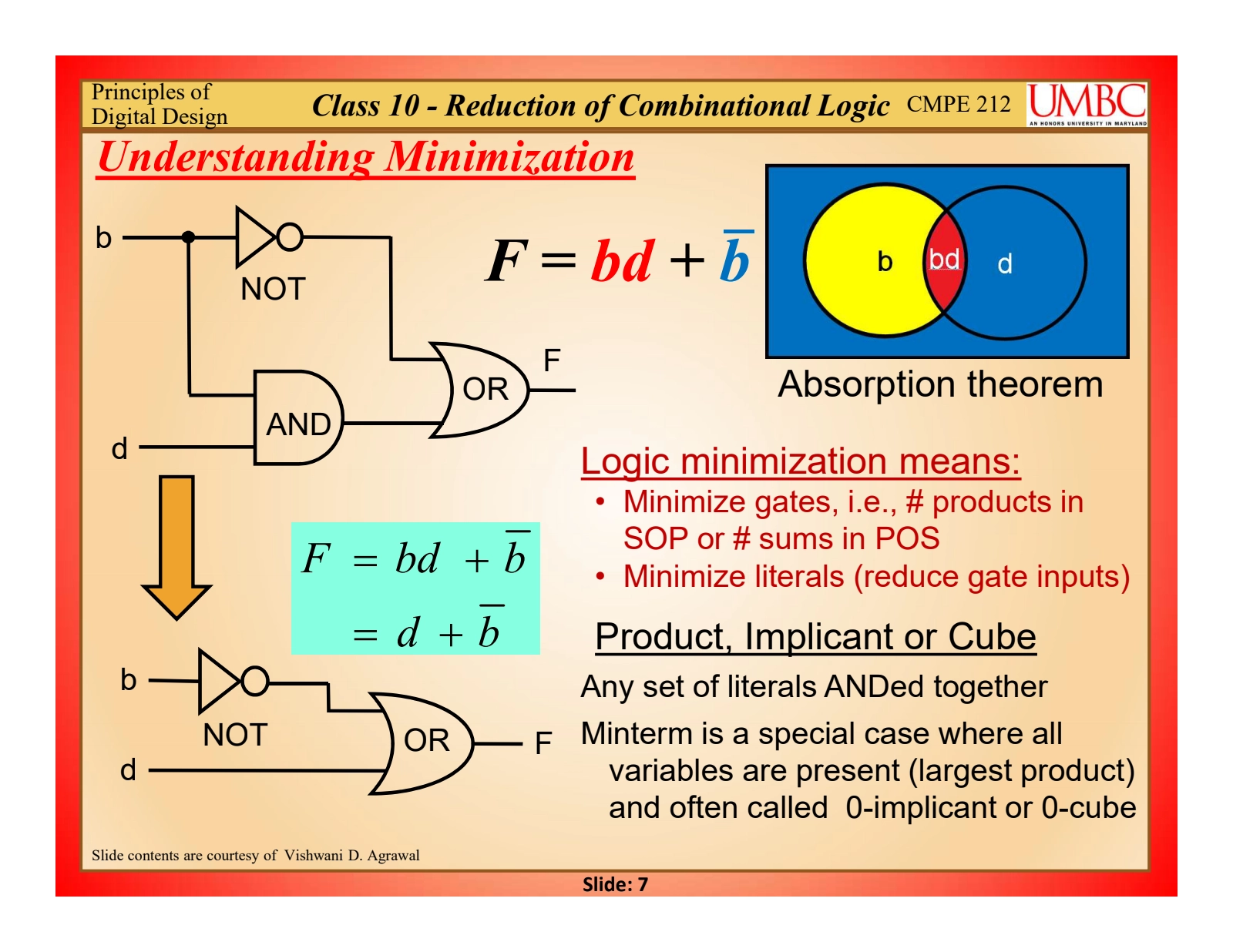

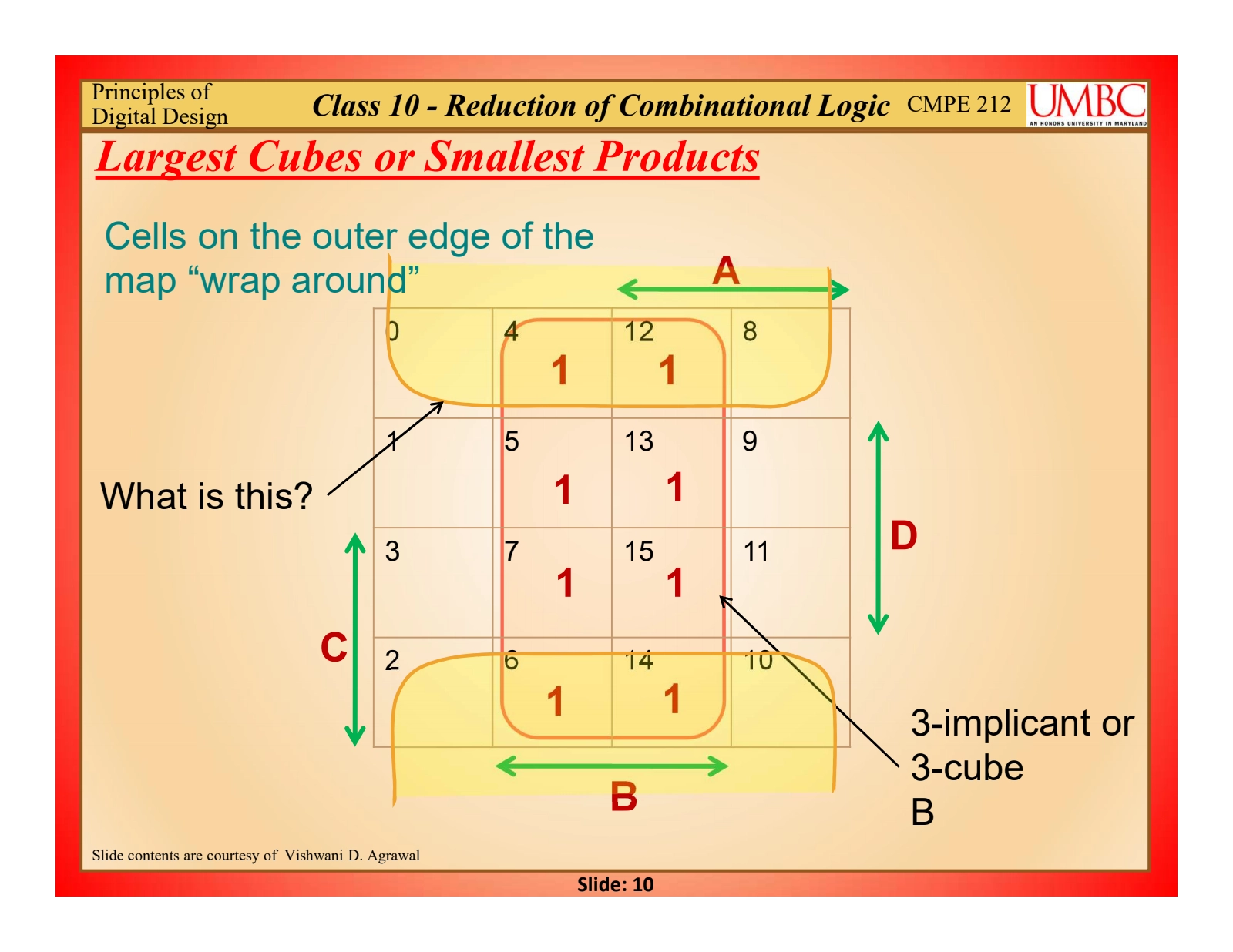

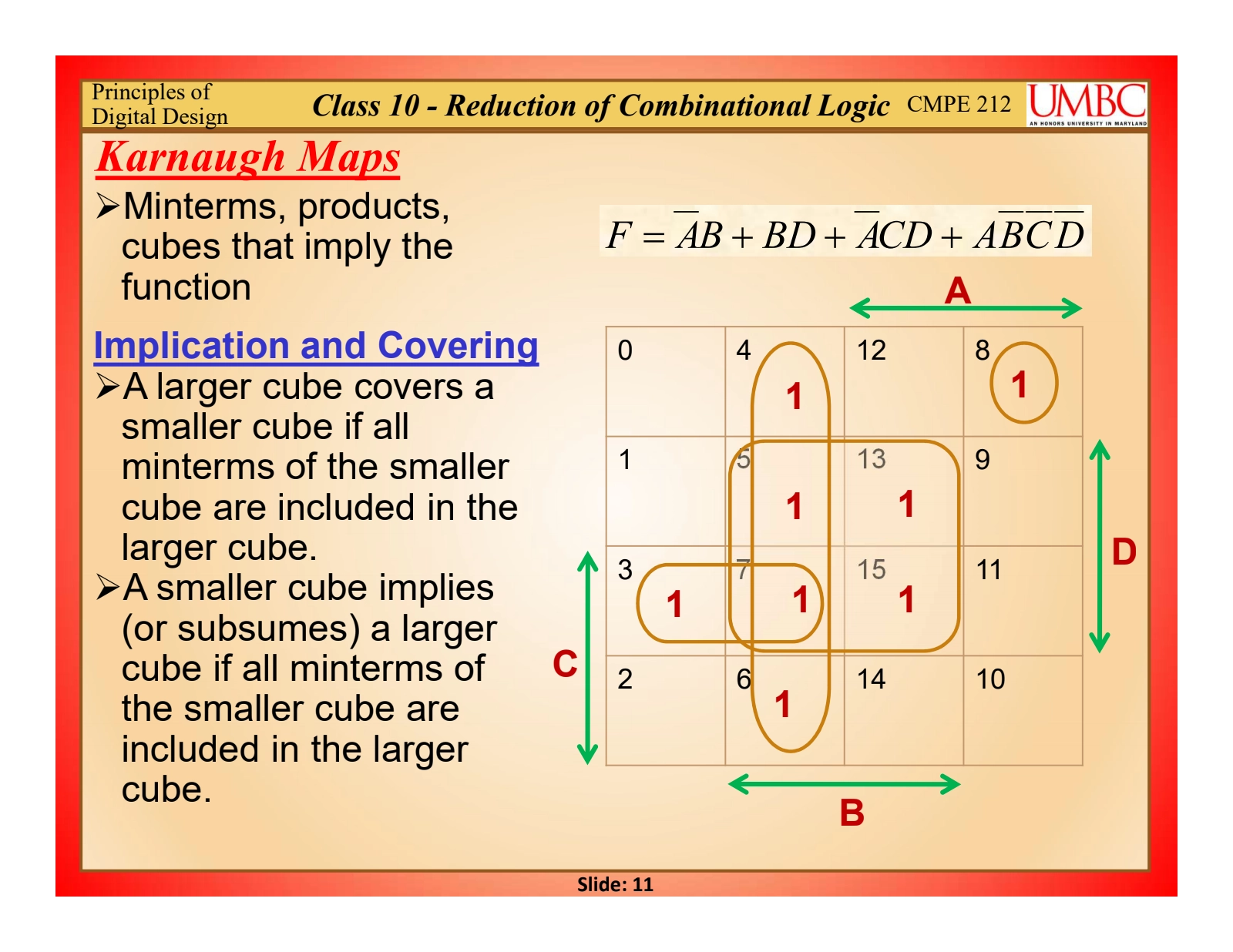

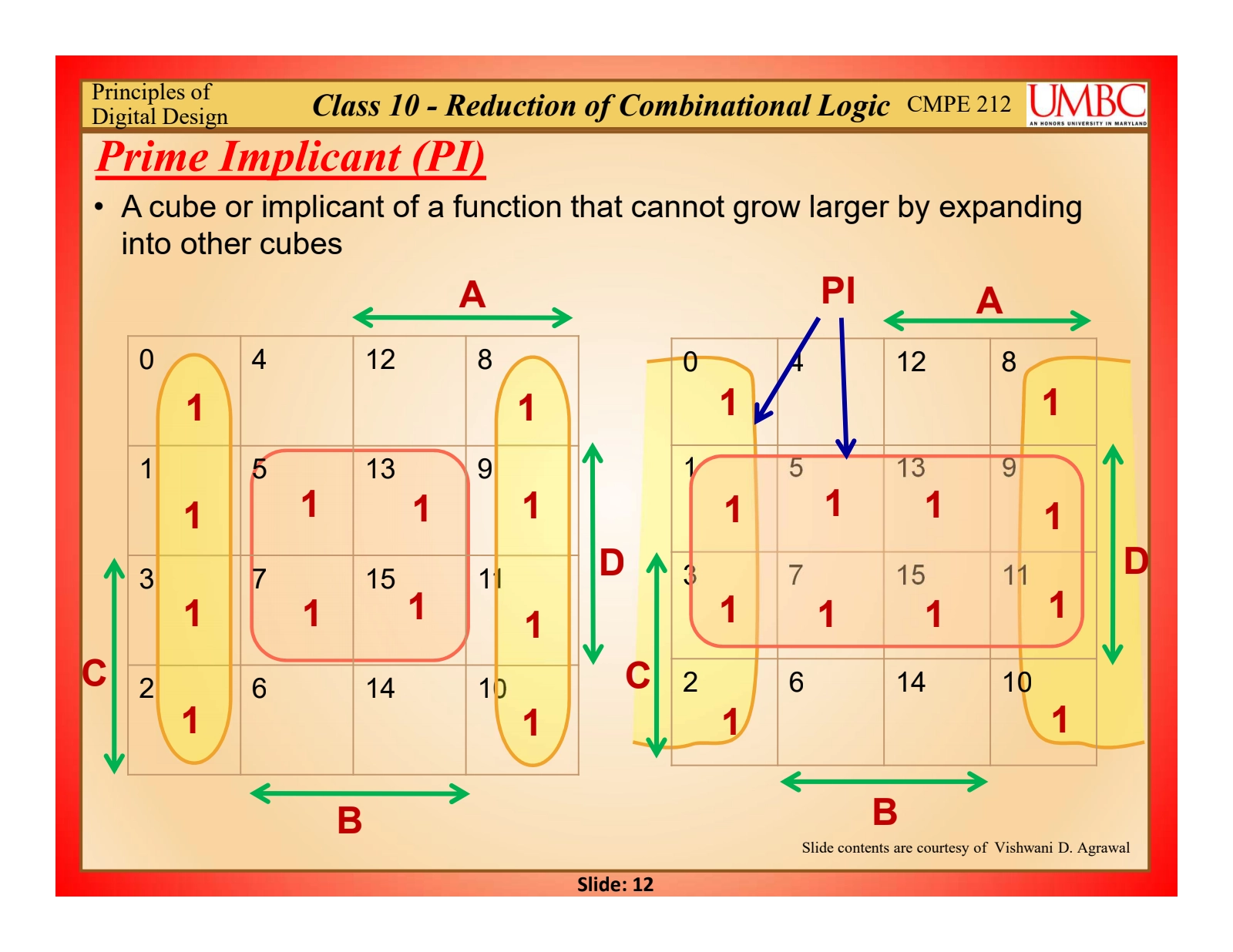

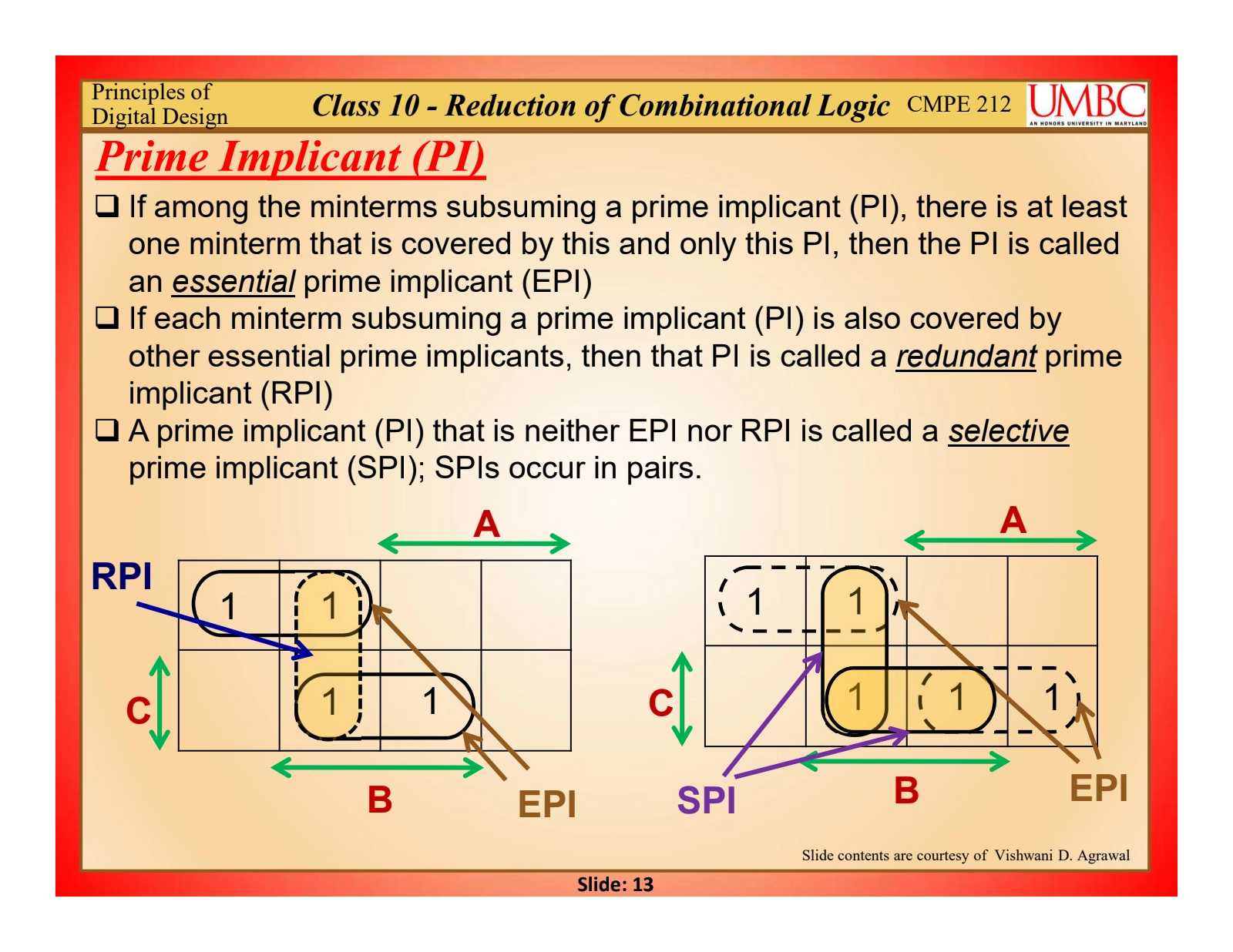

Class: 10, slide: 5 → Forming Karnaugh Maps

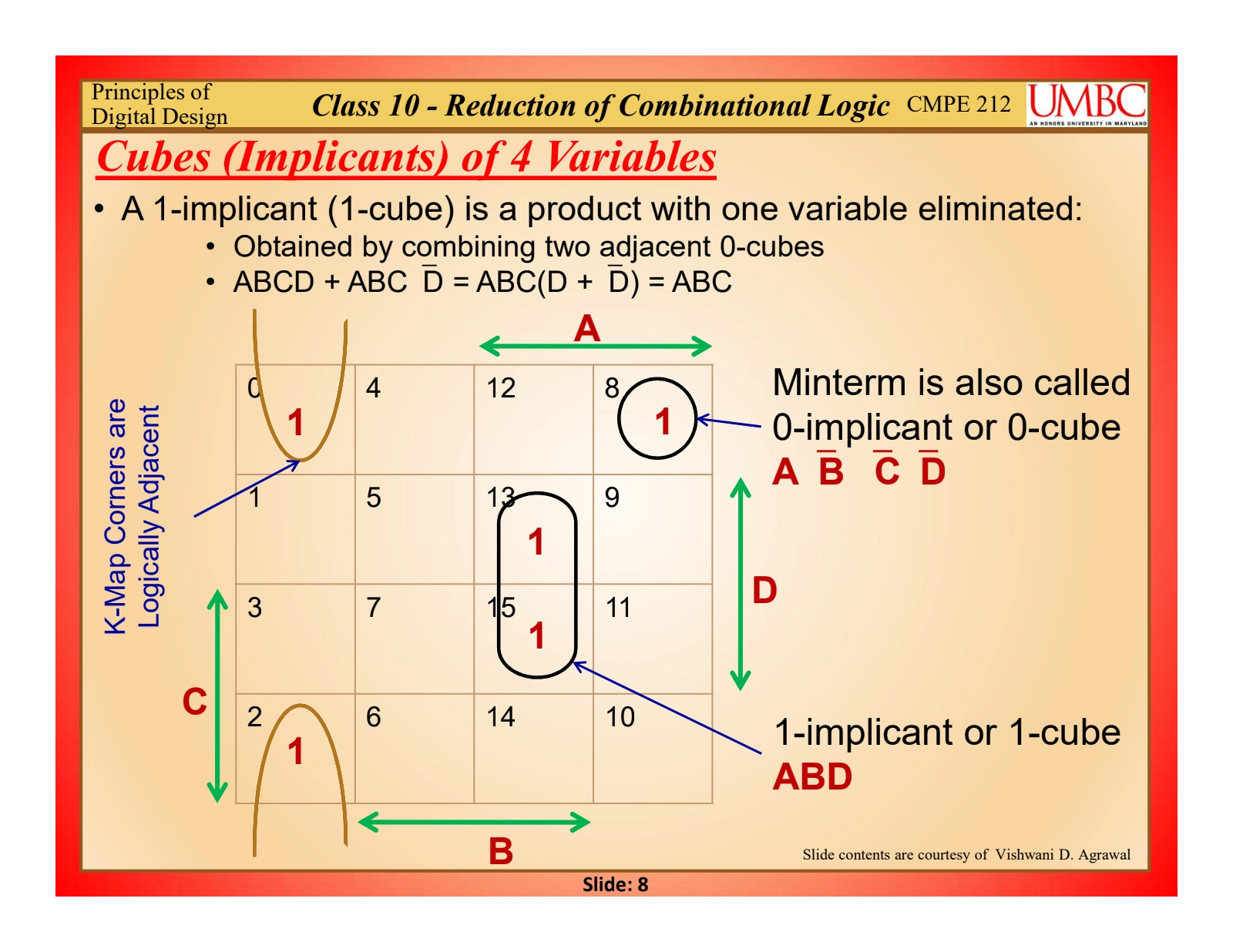

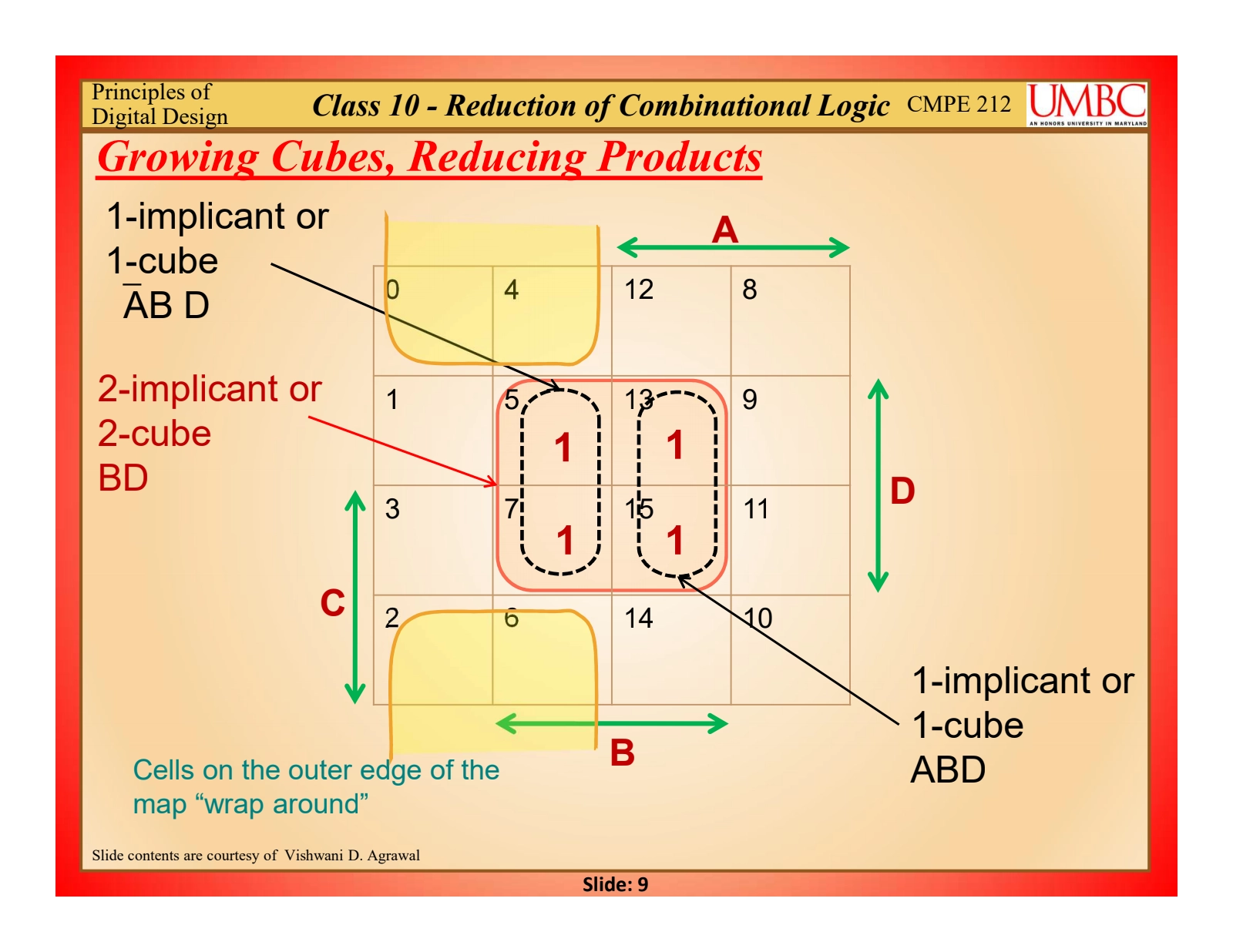

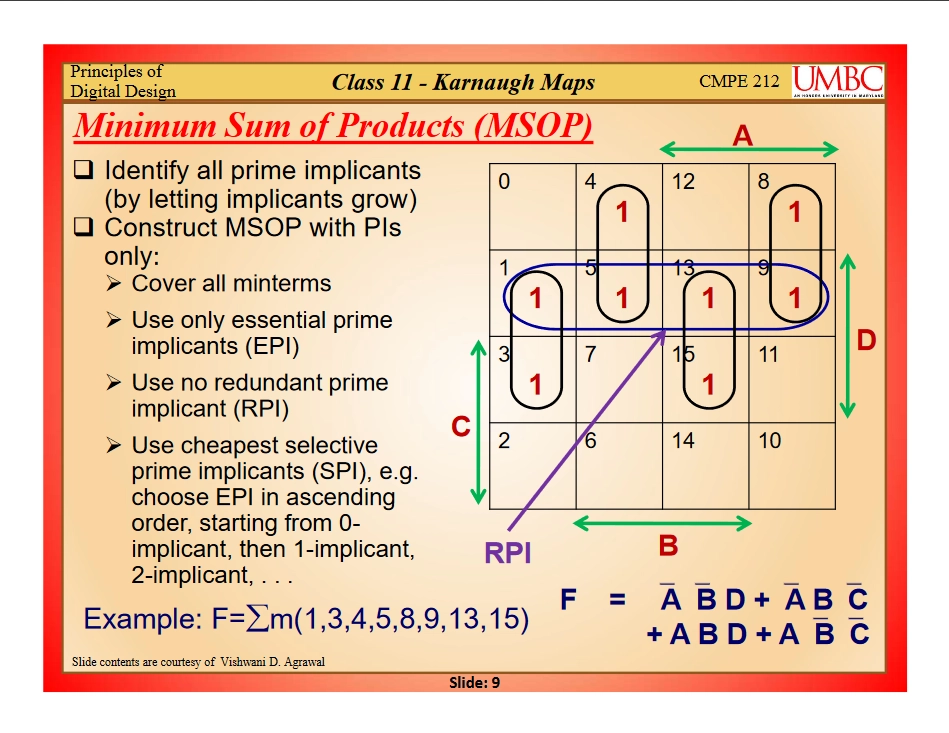

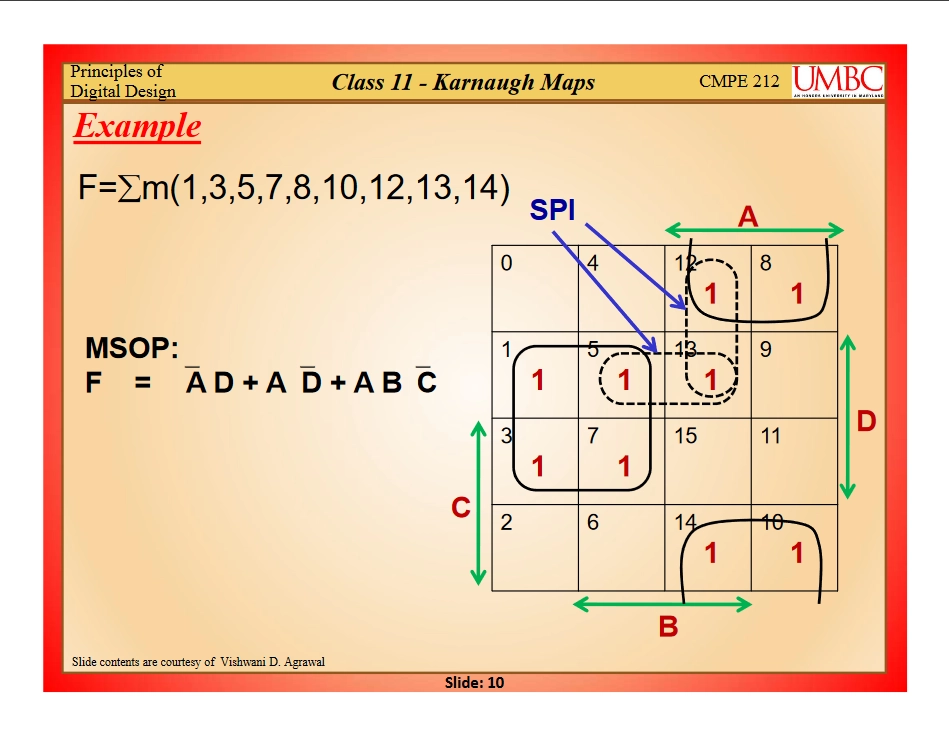

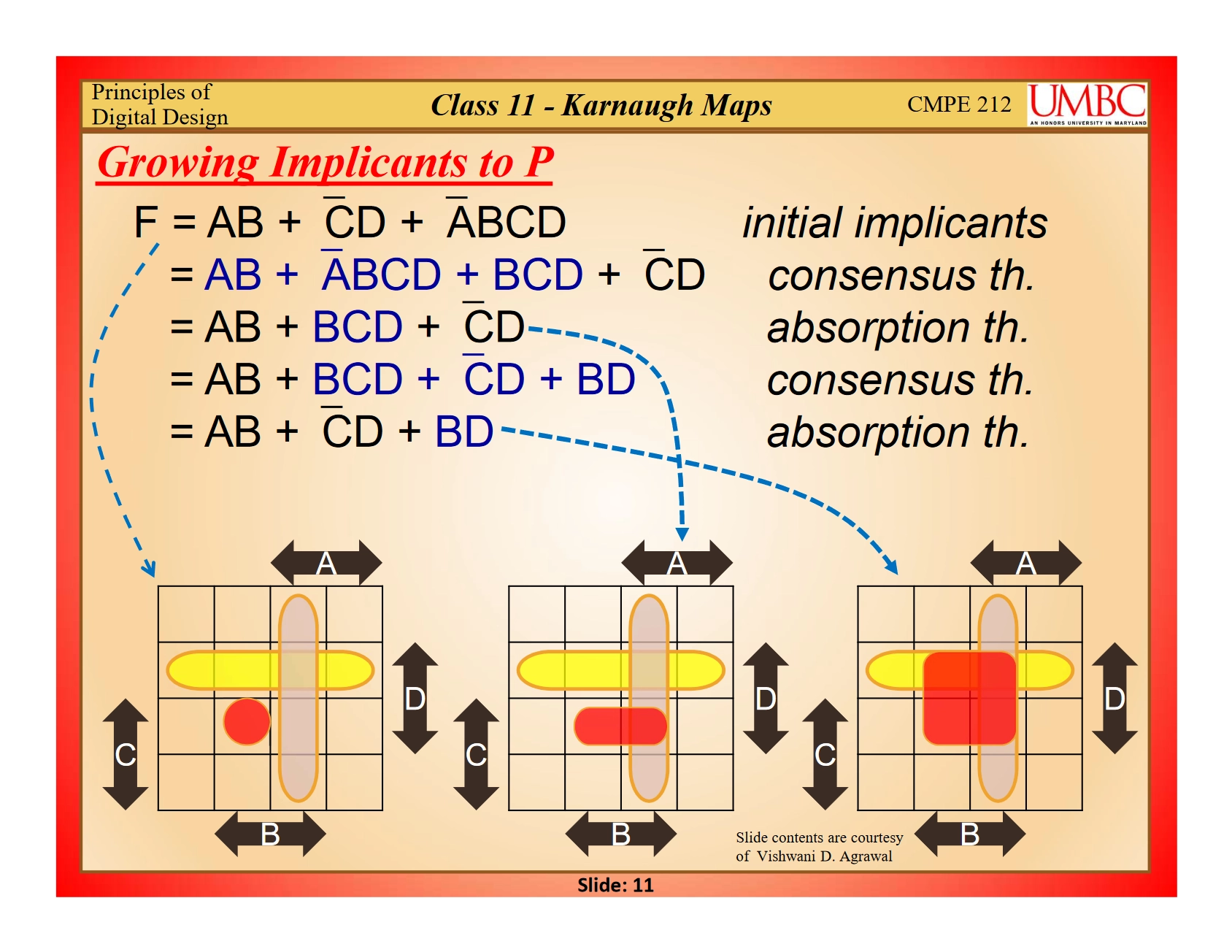

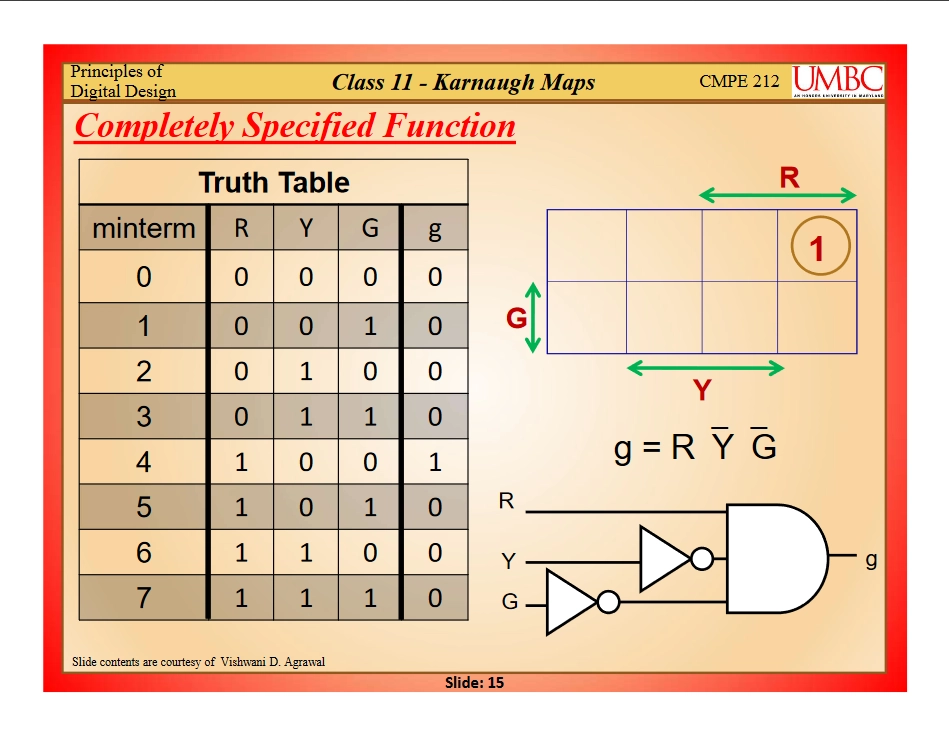

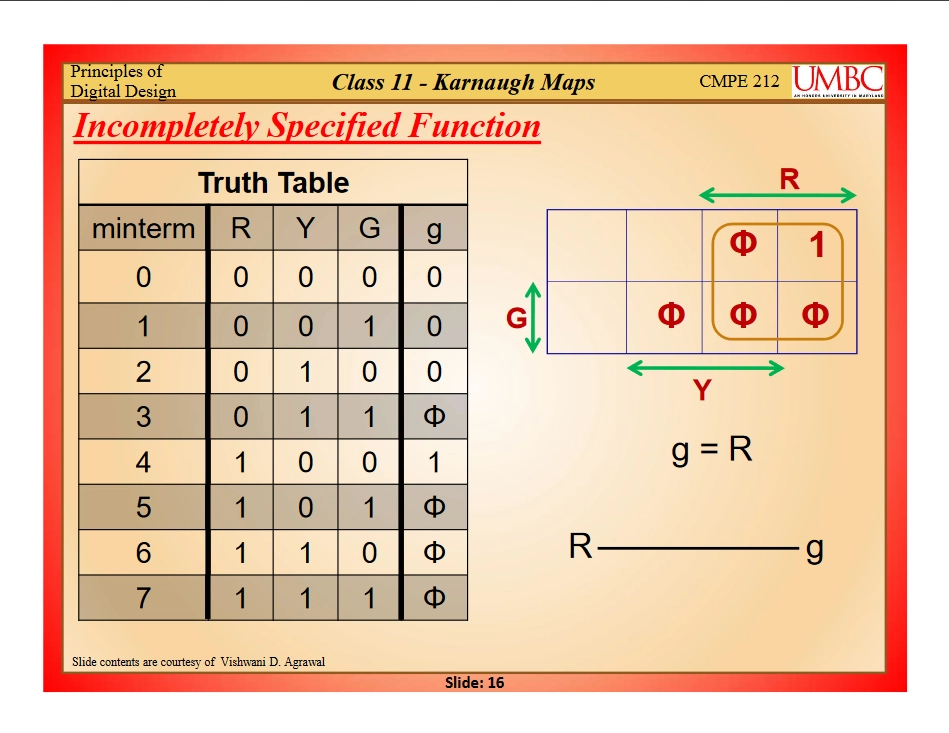

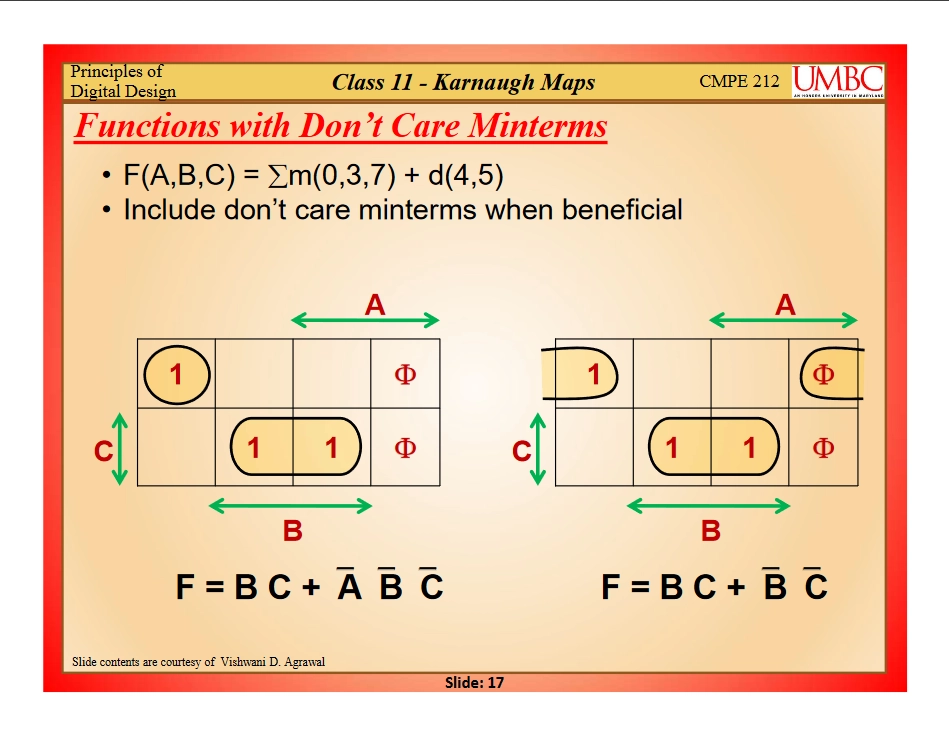

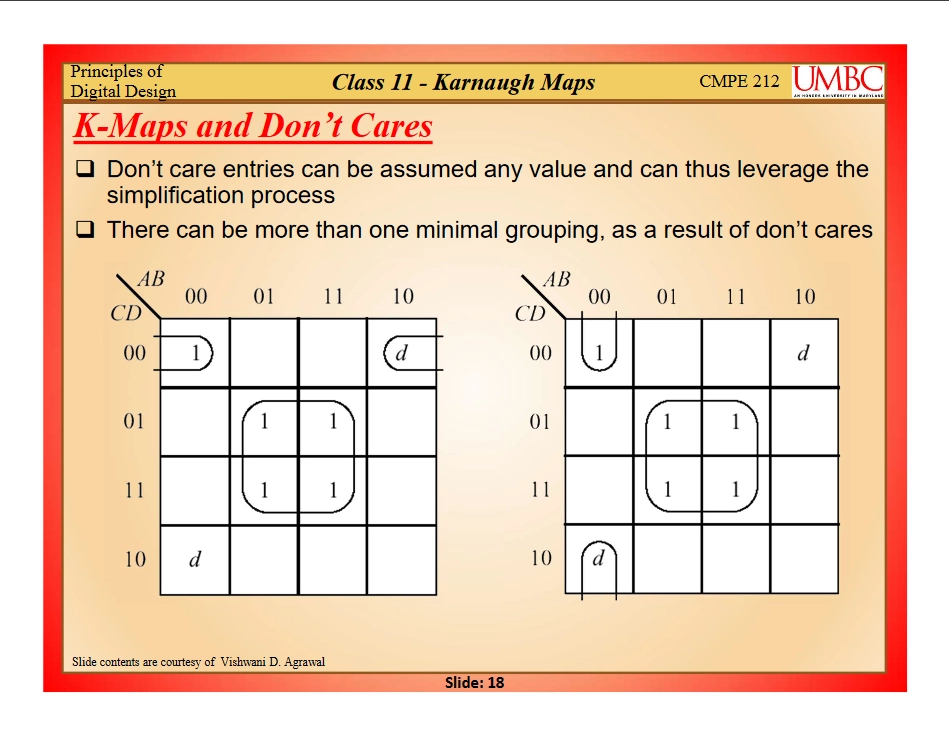

Class: 10, slide: 8-16 → Know How to do a Karnaugh-Map!!

class: 11, slide: 9-11 → Minterms Covered by a Product

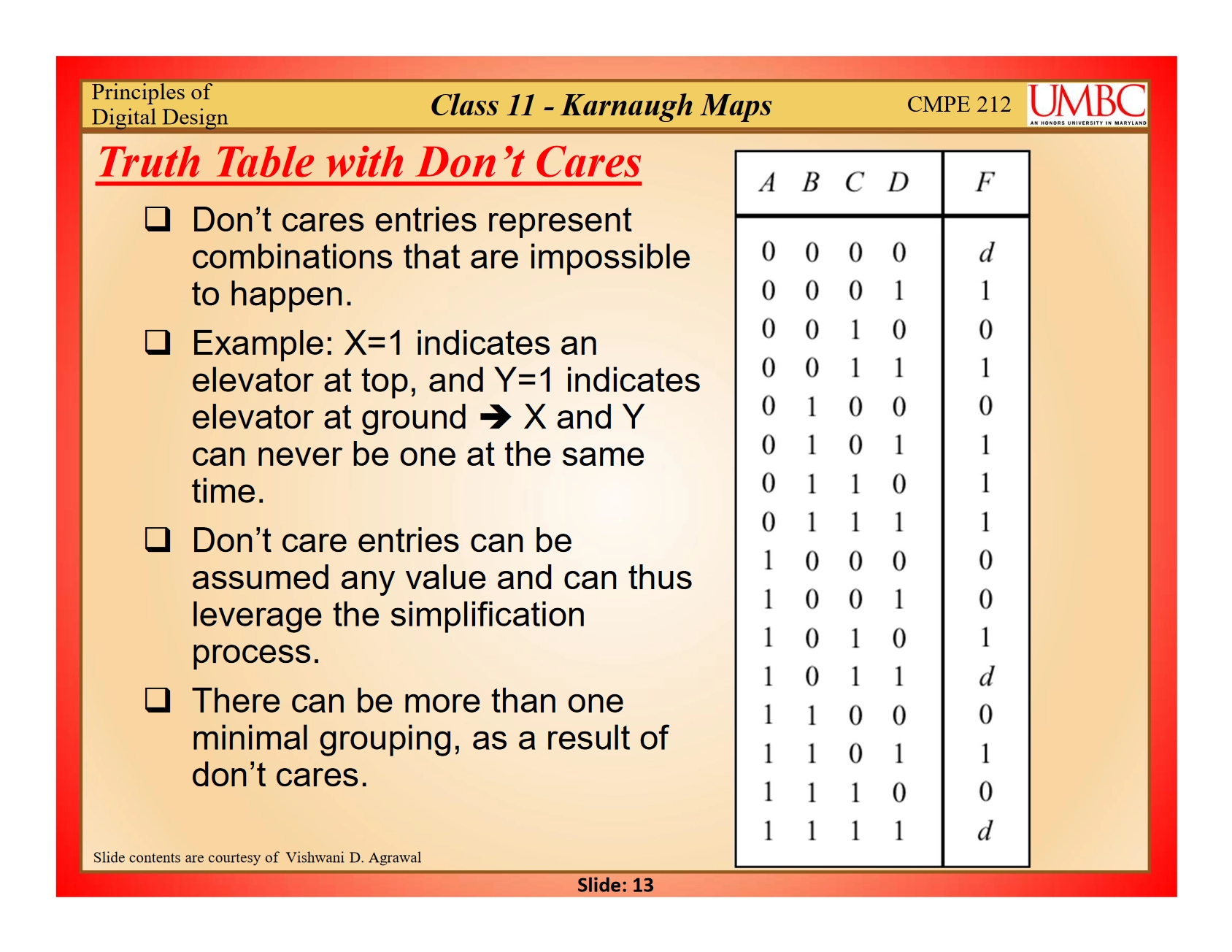

class: 11, slide: 13-18 → K Mapping with Don't Cares

class: 12, slide: 13 → Speed and Performance

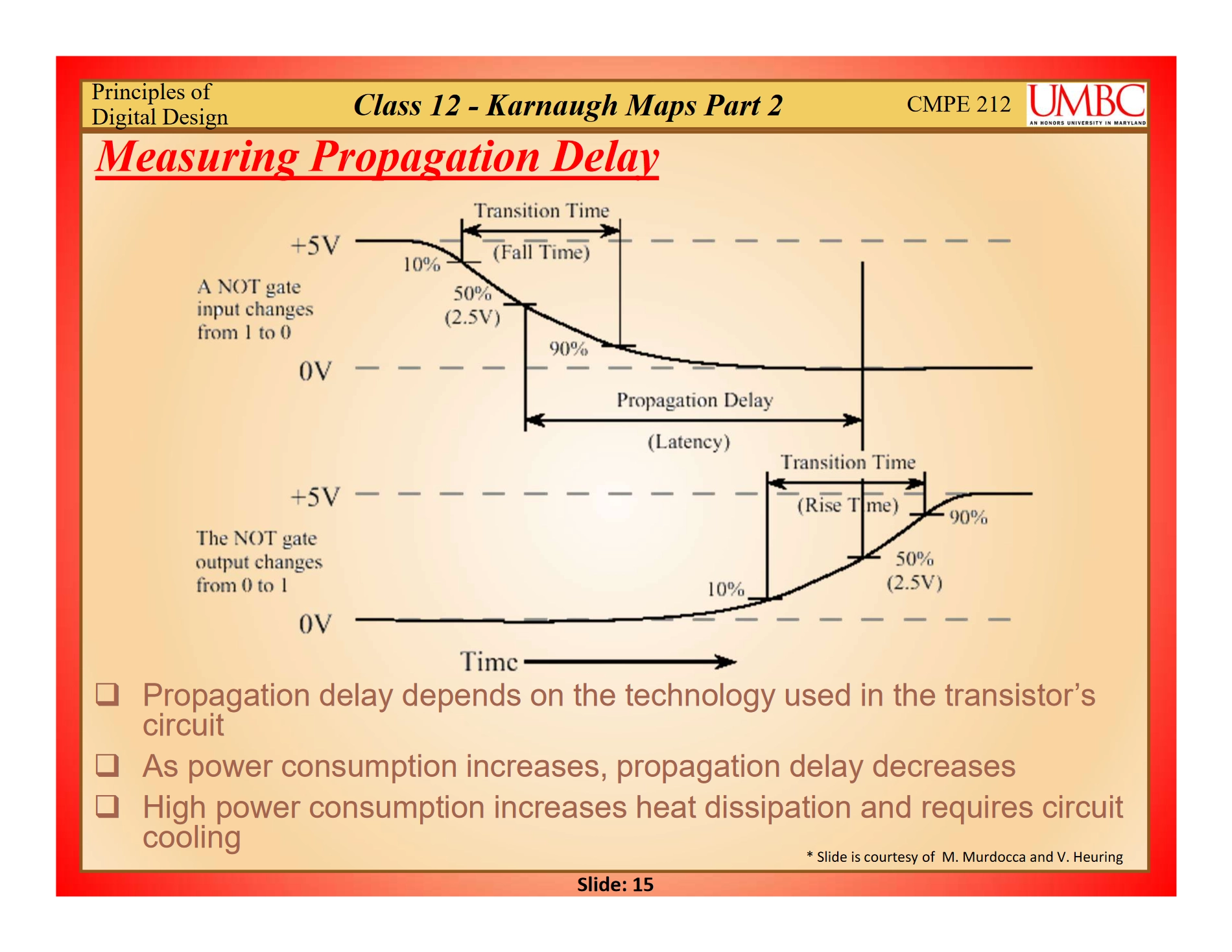

class: 12, slide: 15 → Measuring Propagation Delay

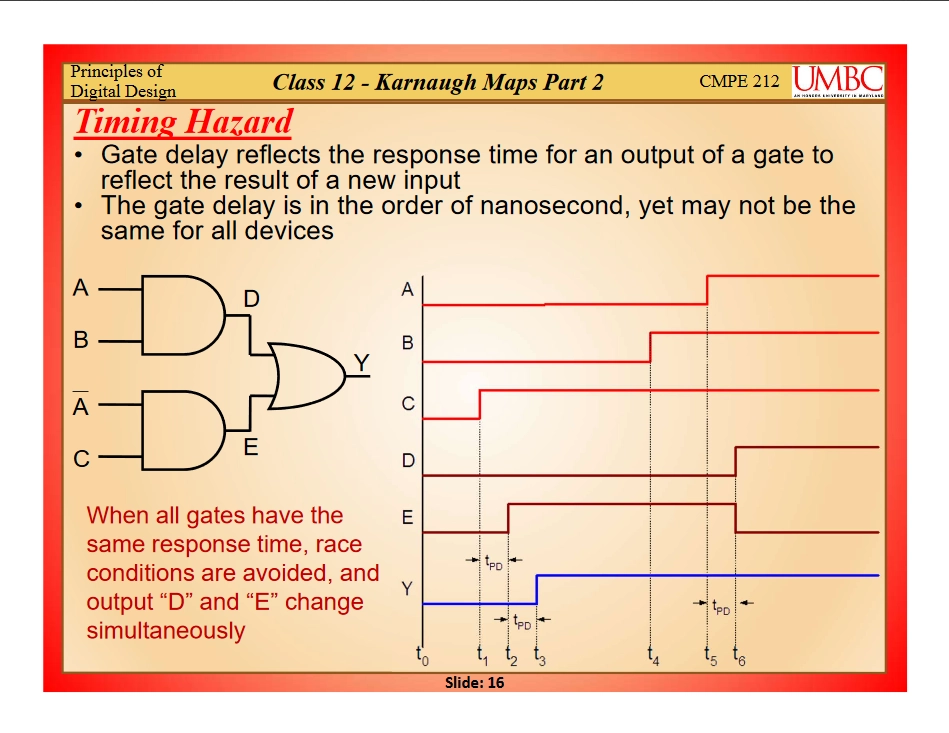

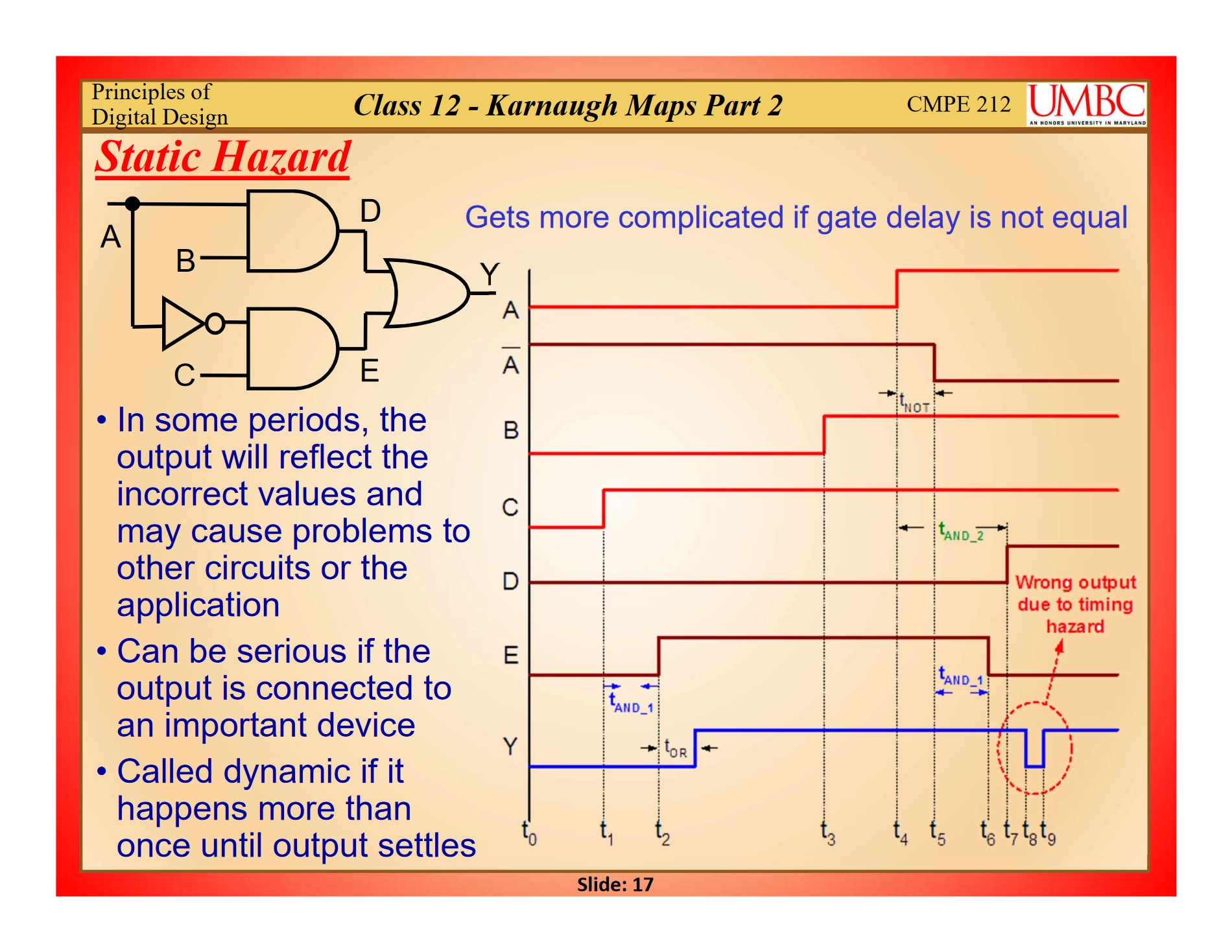

class: 12, slide: 16-17 → Static Hazards and fixing them

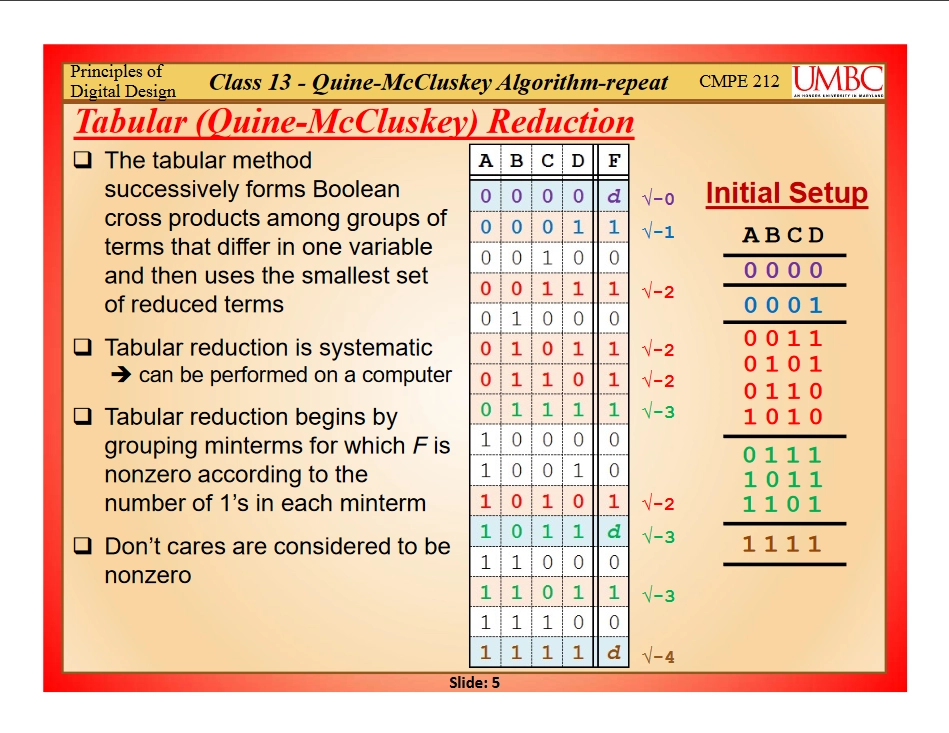

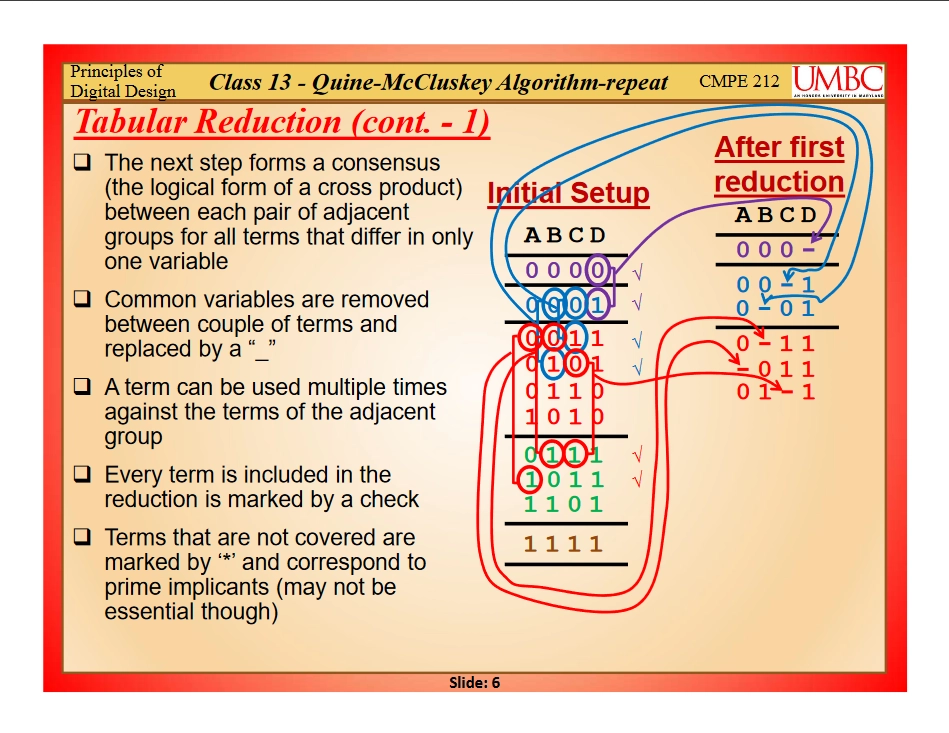

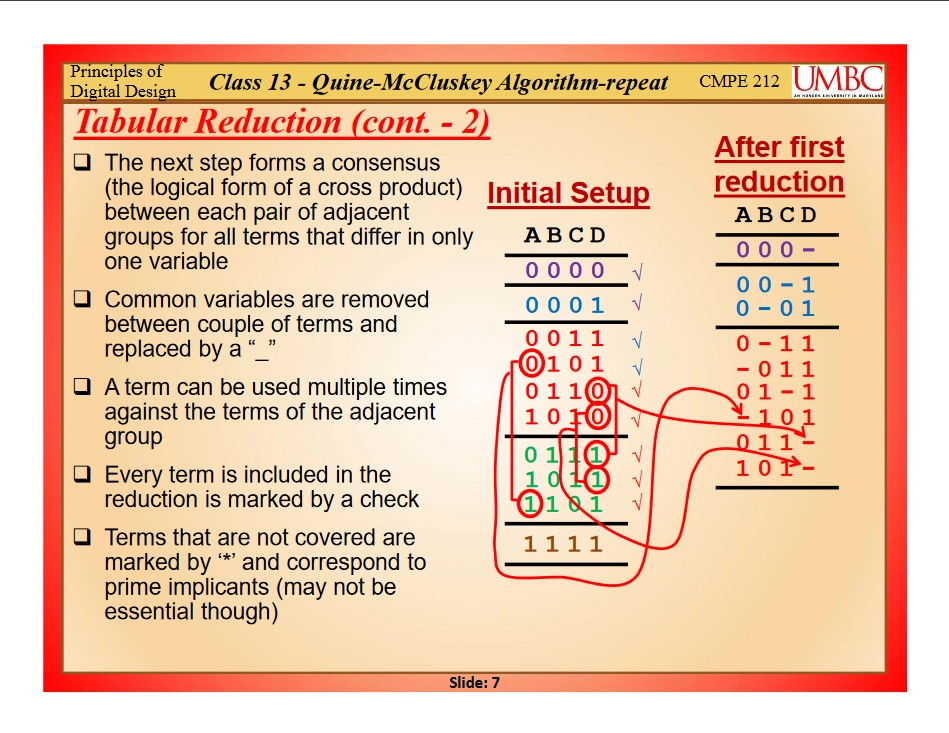

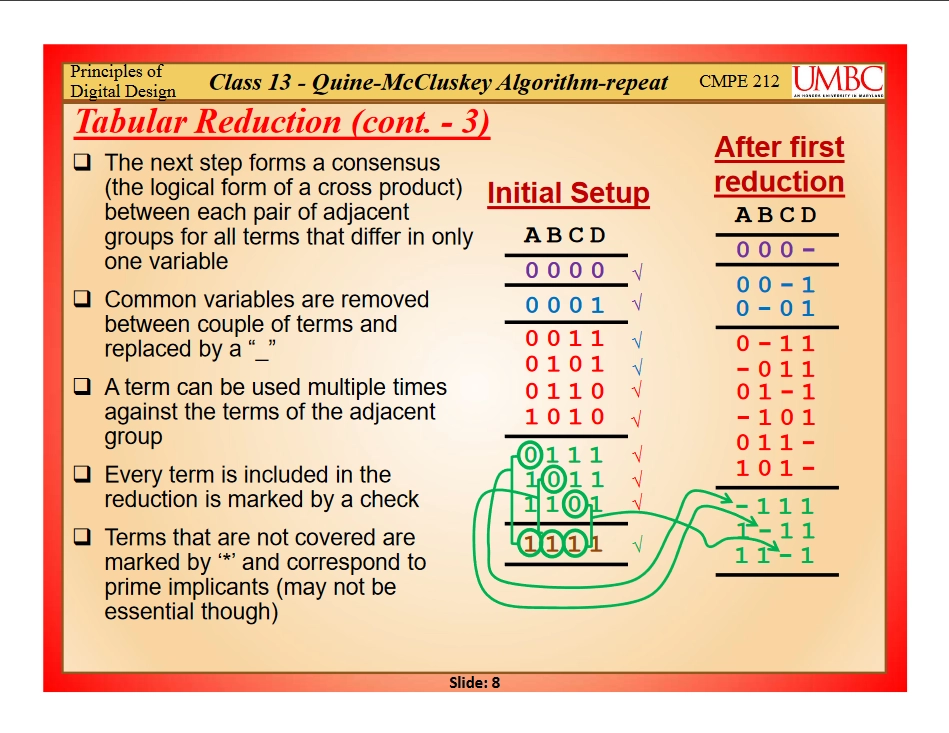

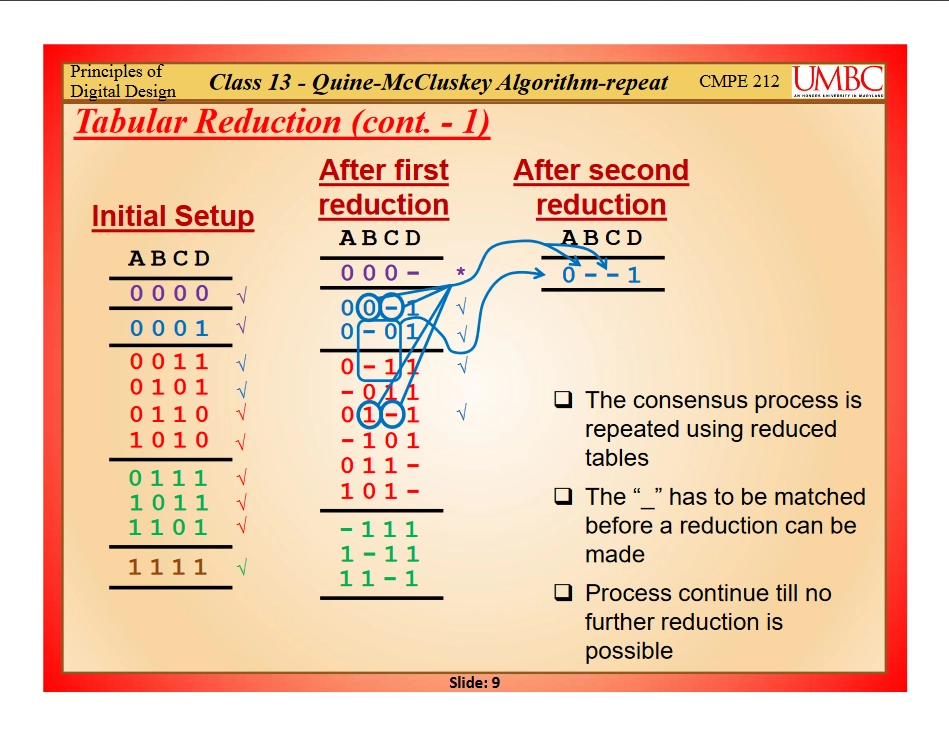

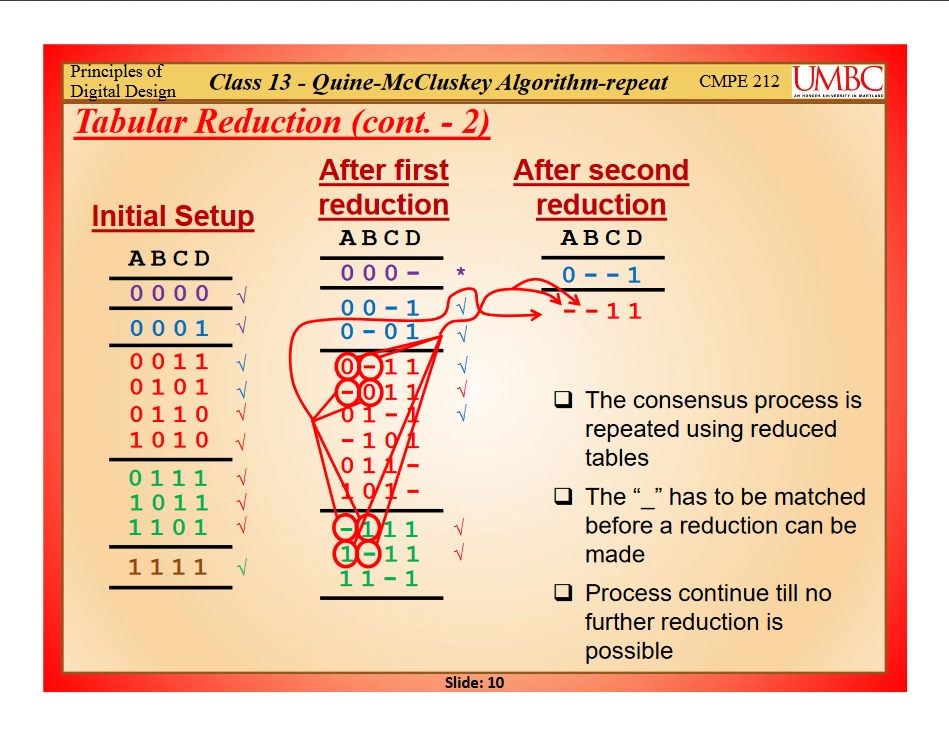

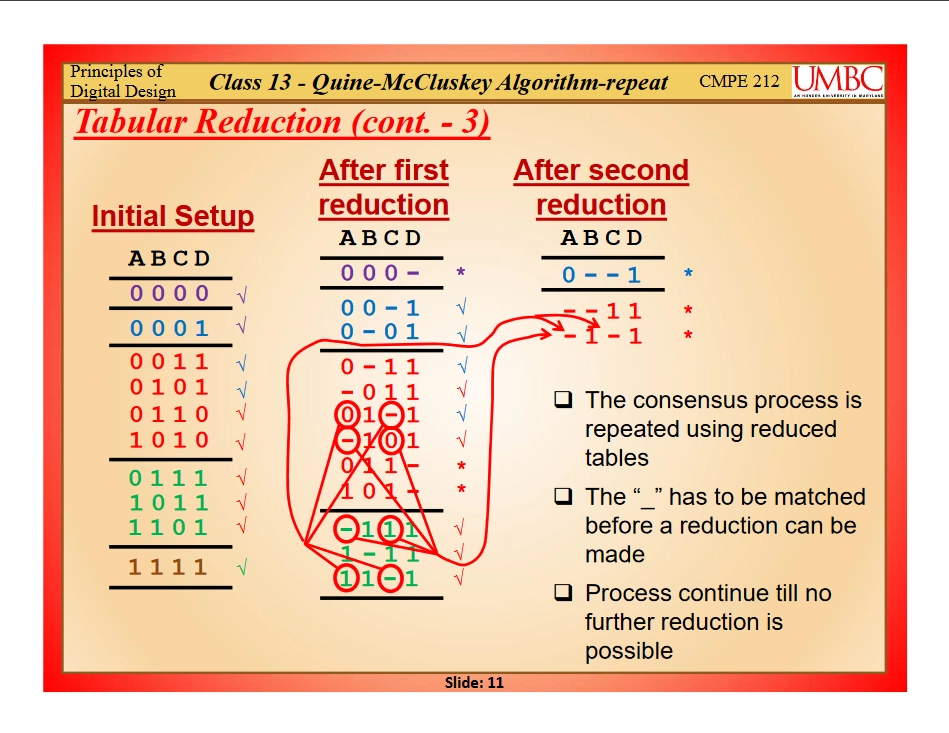

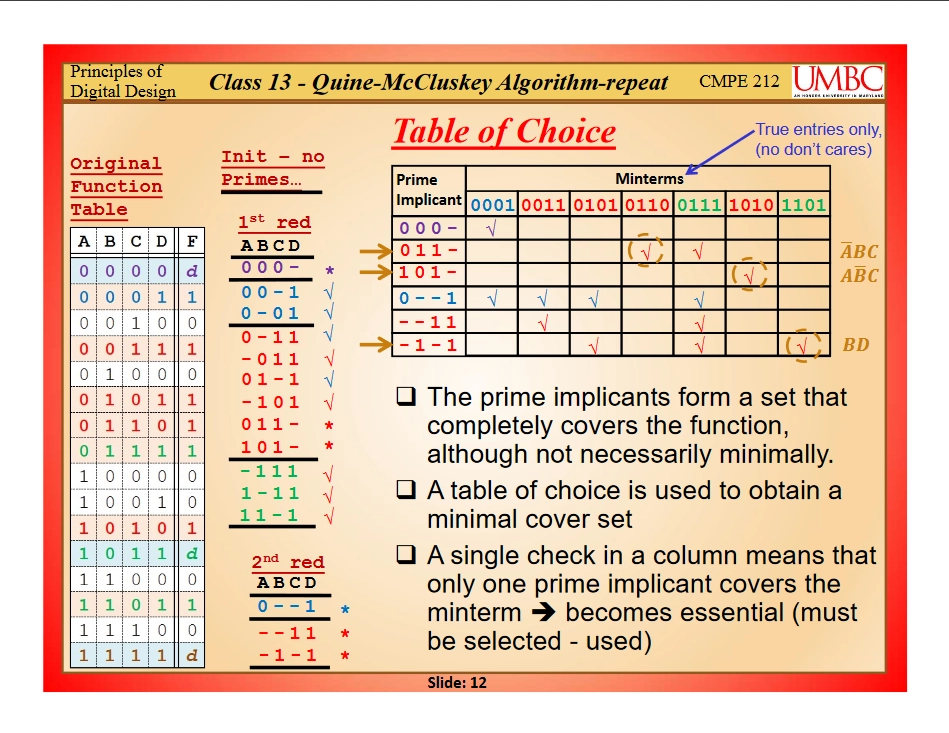

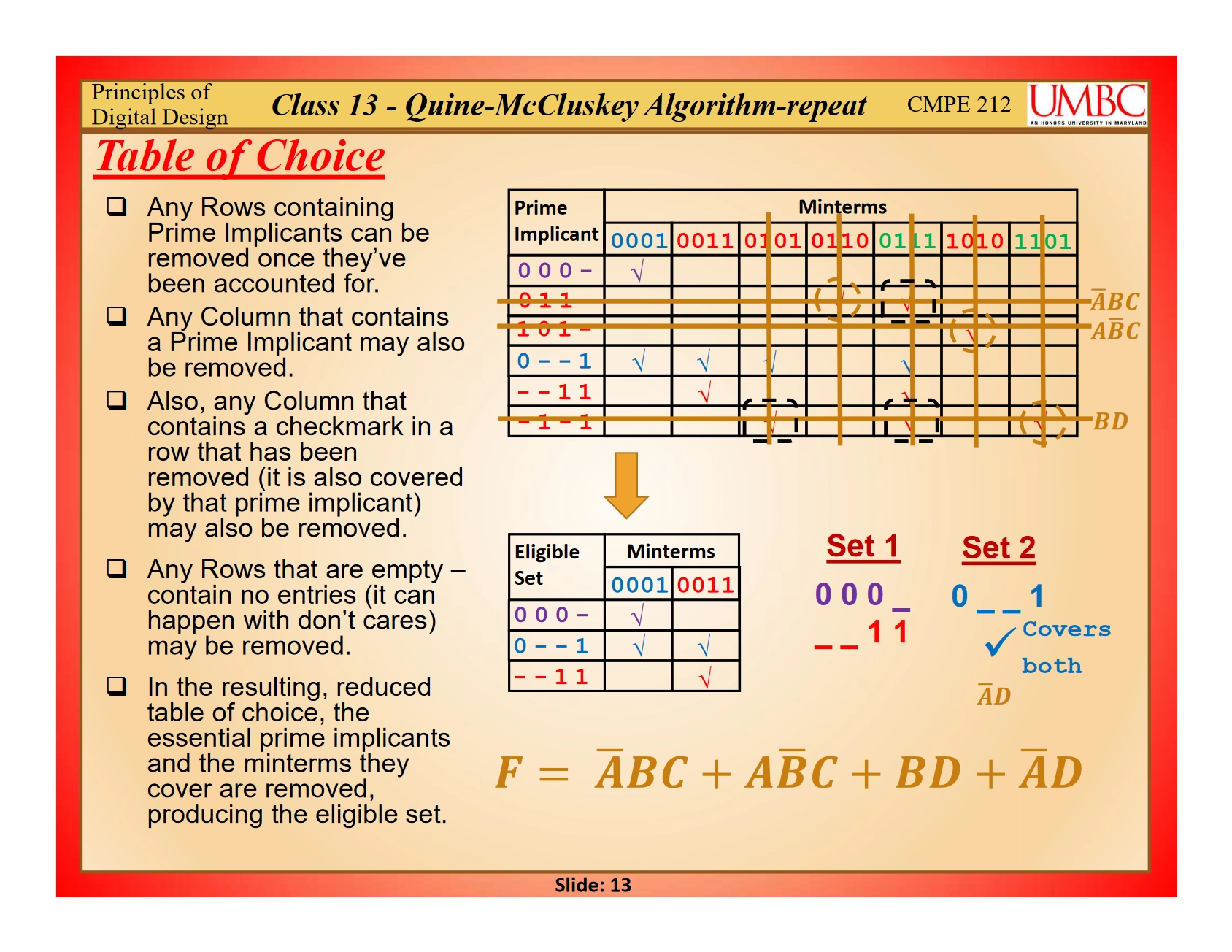

class: 13, slide: 5-13 → Quine McClusky - reduced

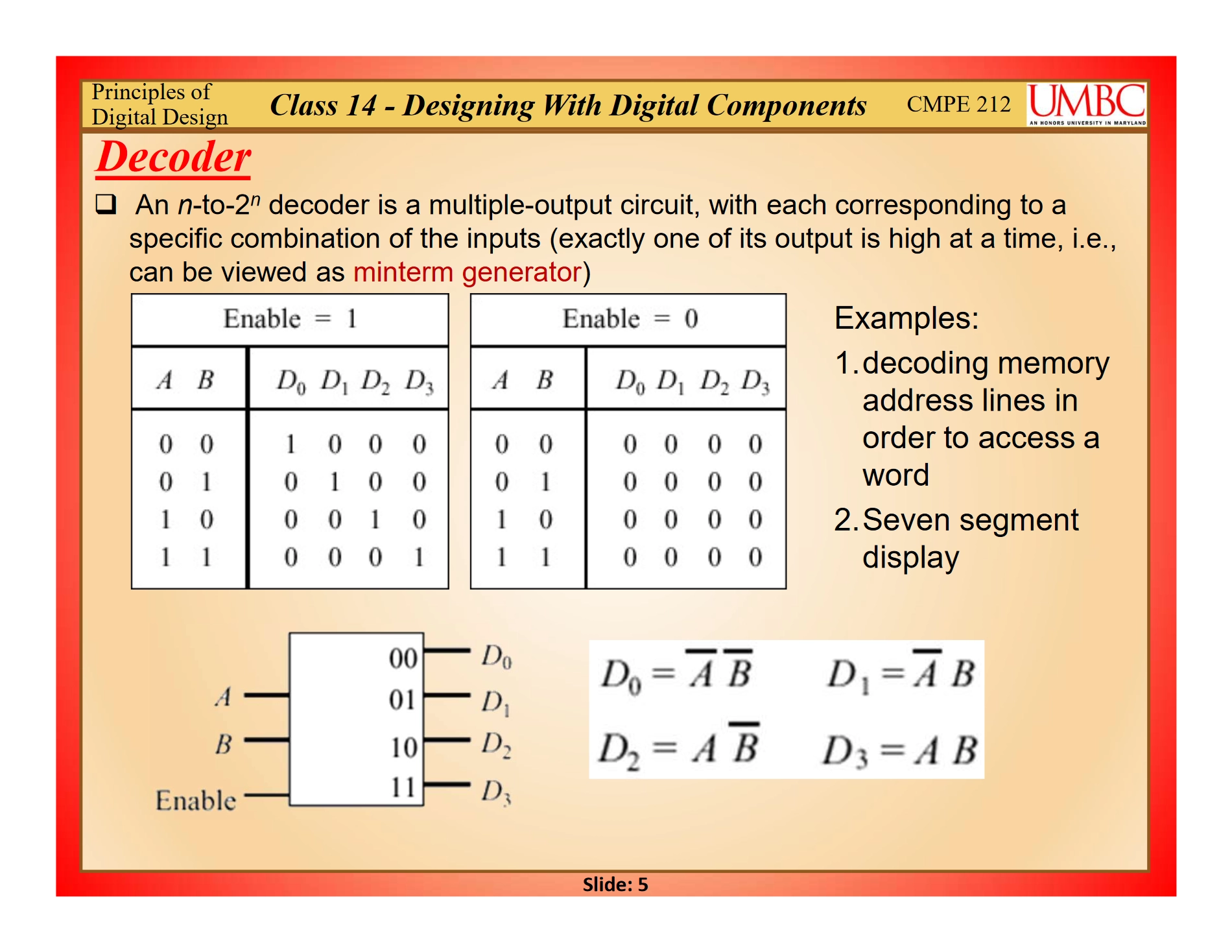

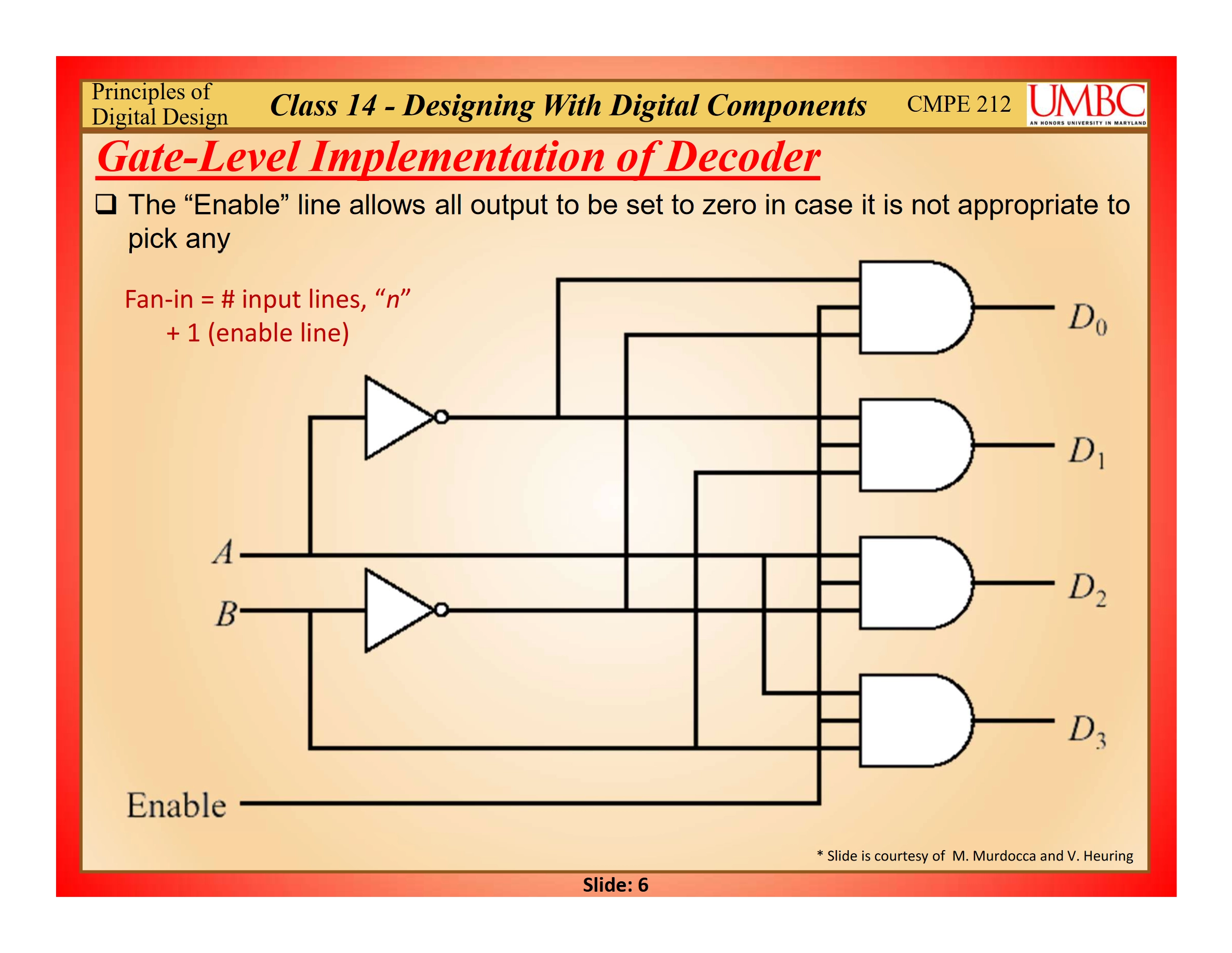

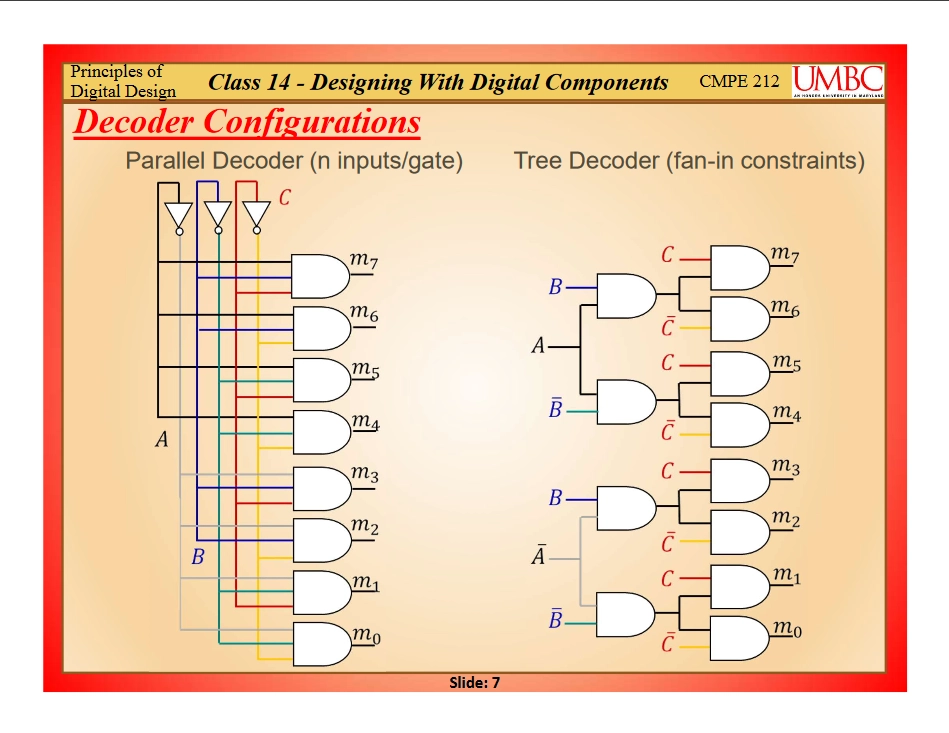

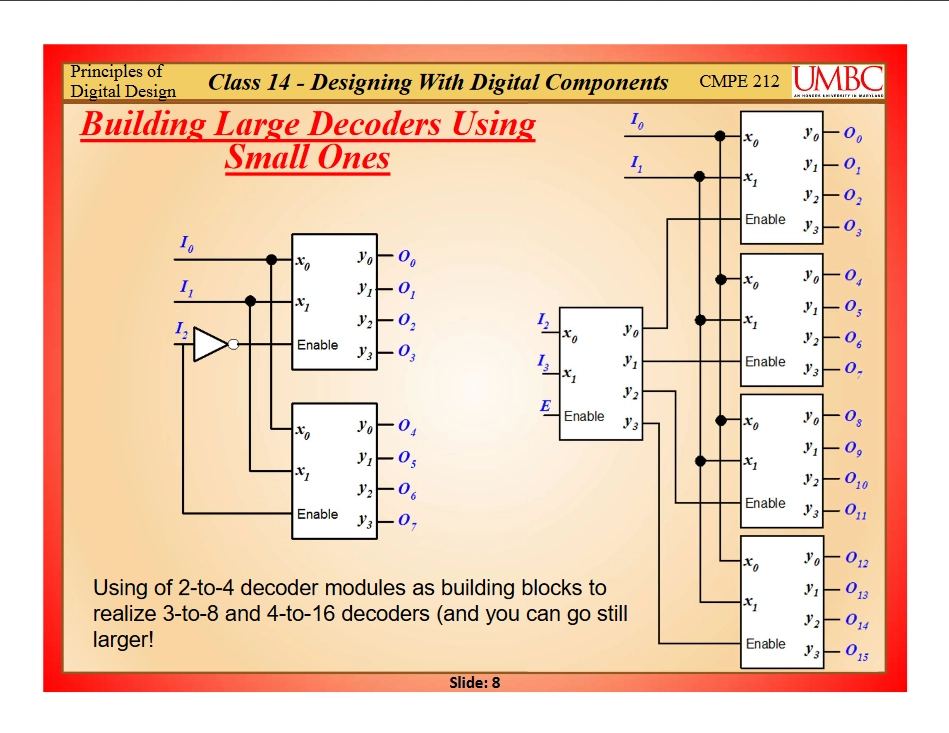

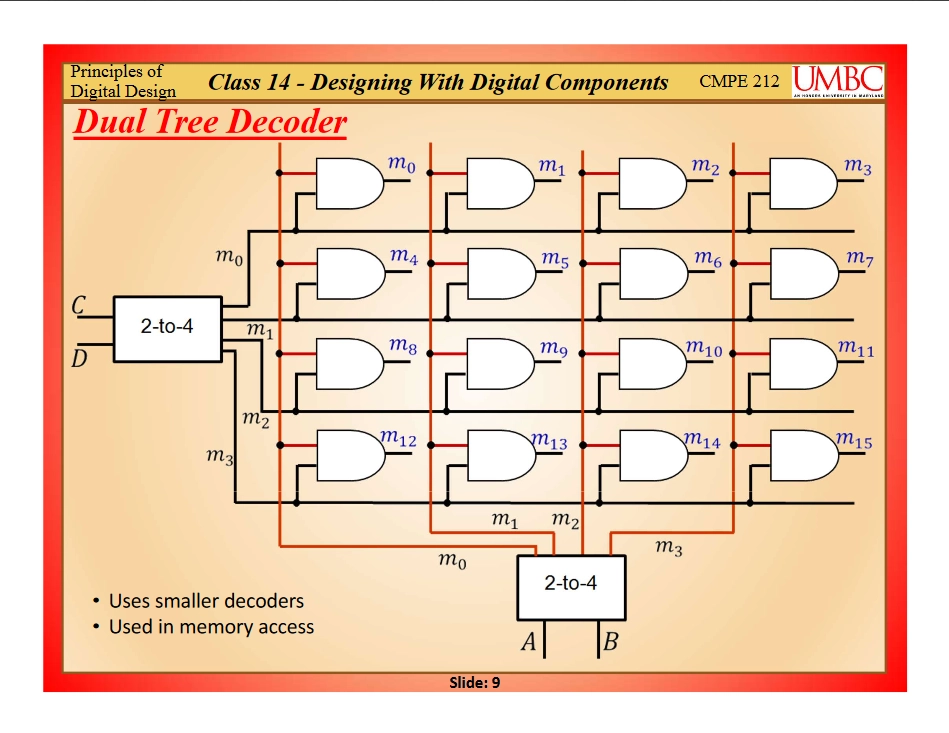

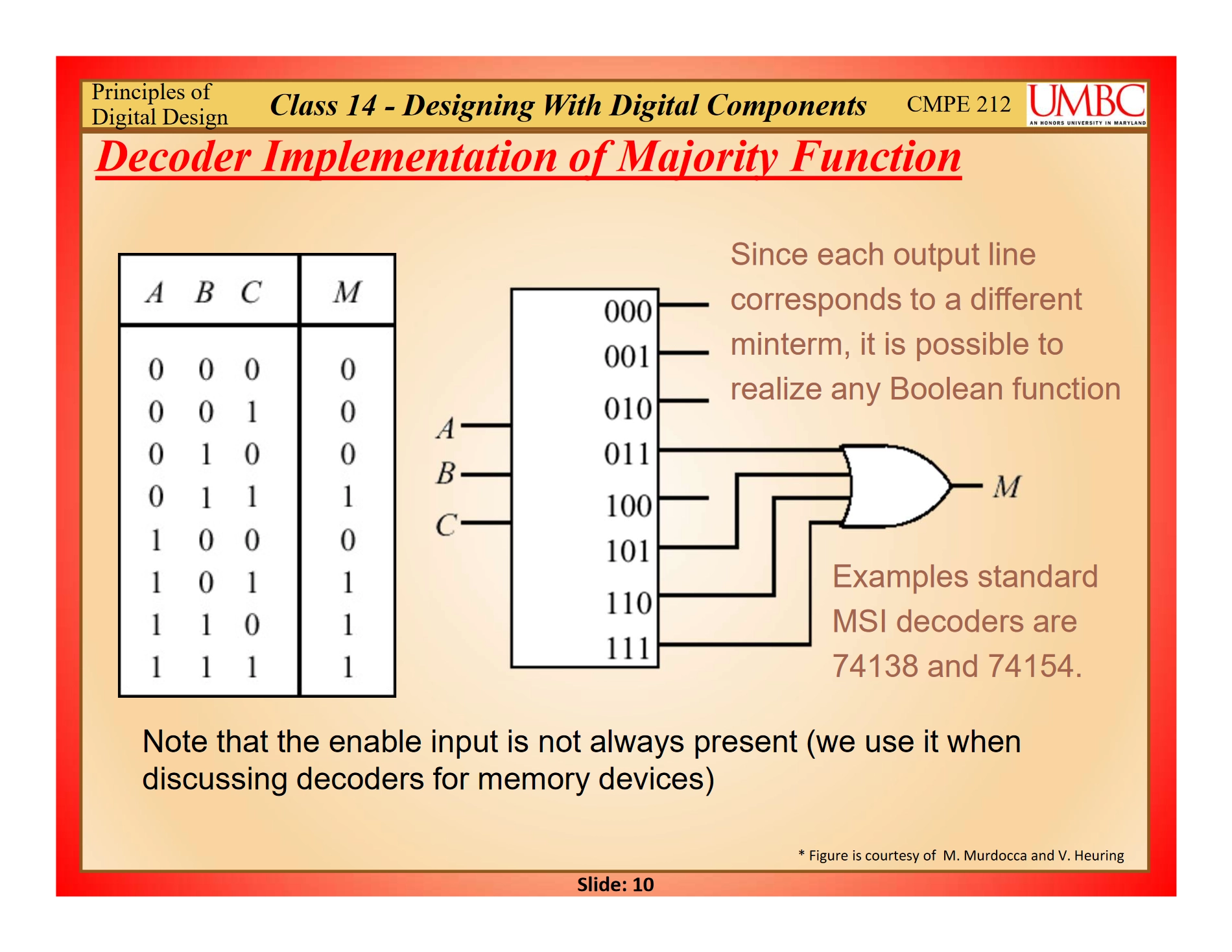

class: 14, slide: 5-10 → Decoder, Building Large Decoders, Doing a function with one

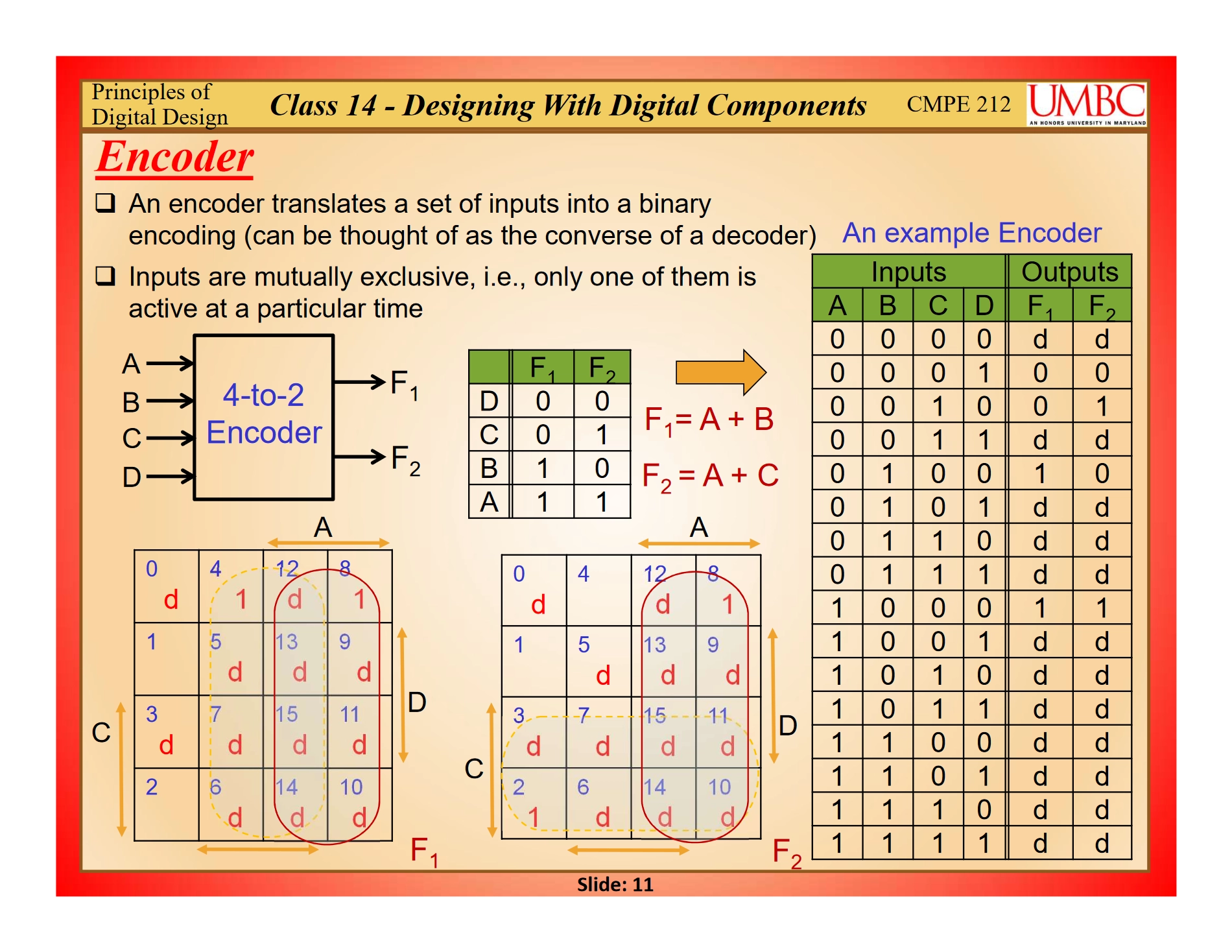

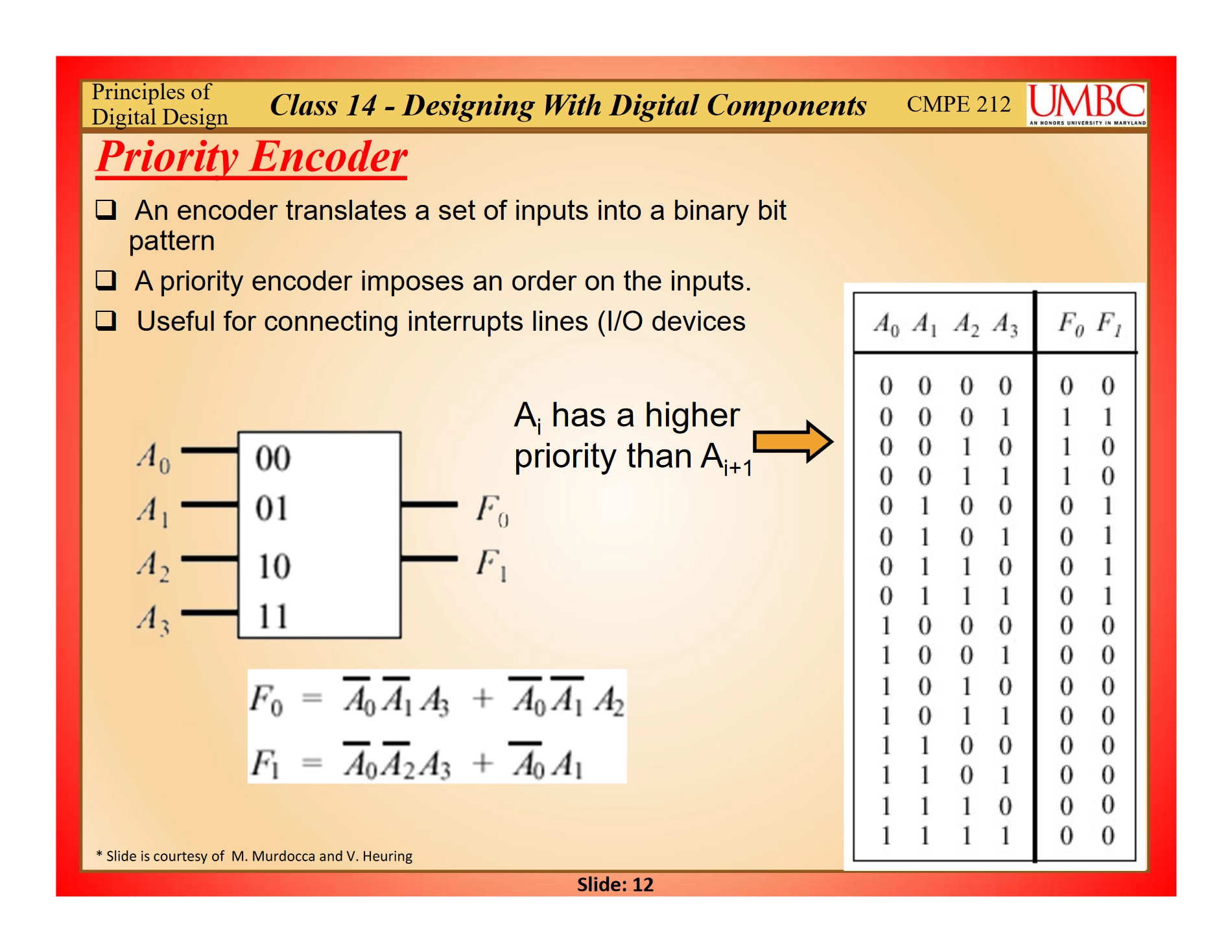

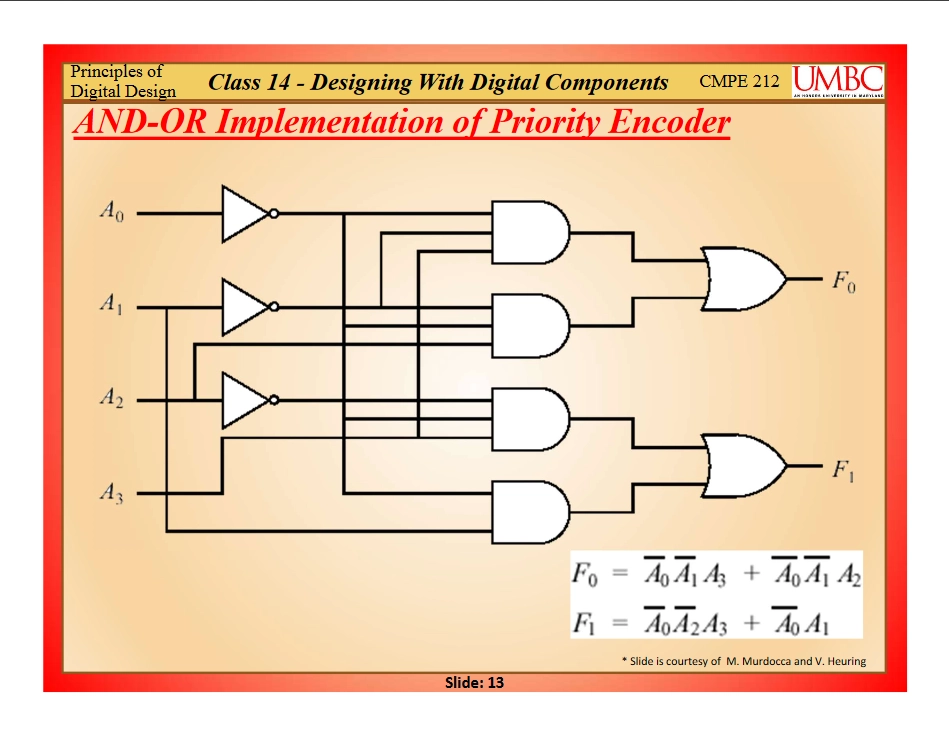

class: 14, slide: 11-13 → Encoder, Priority Encoder

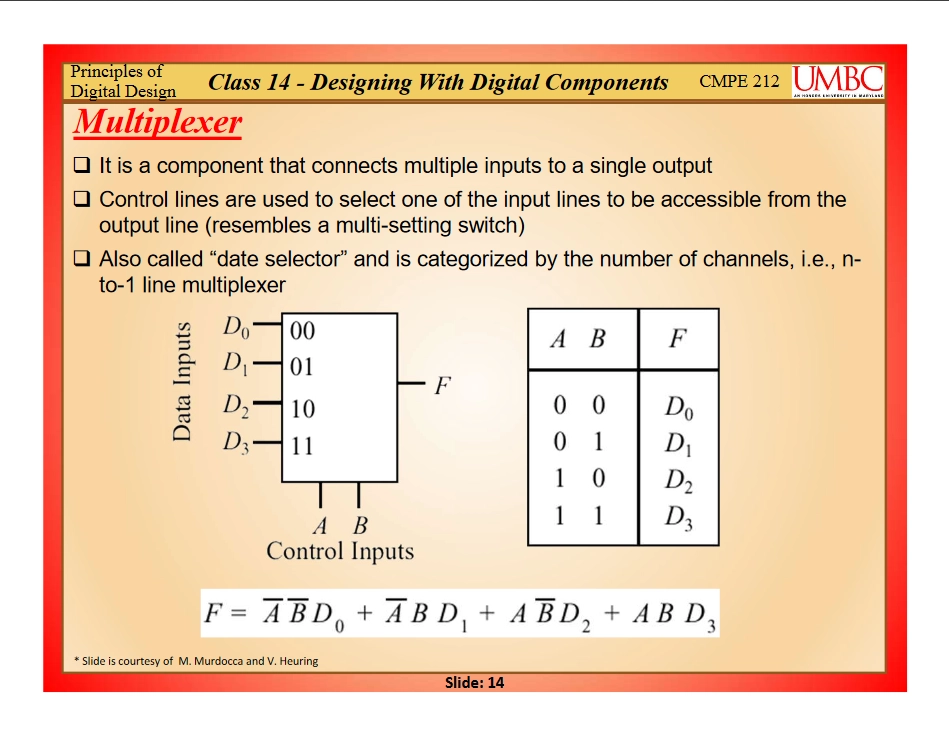

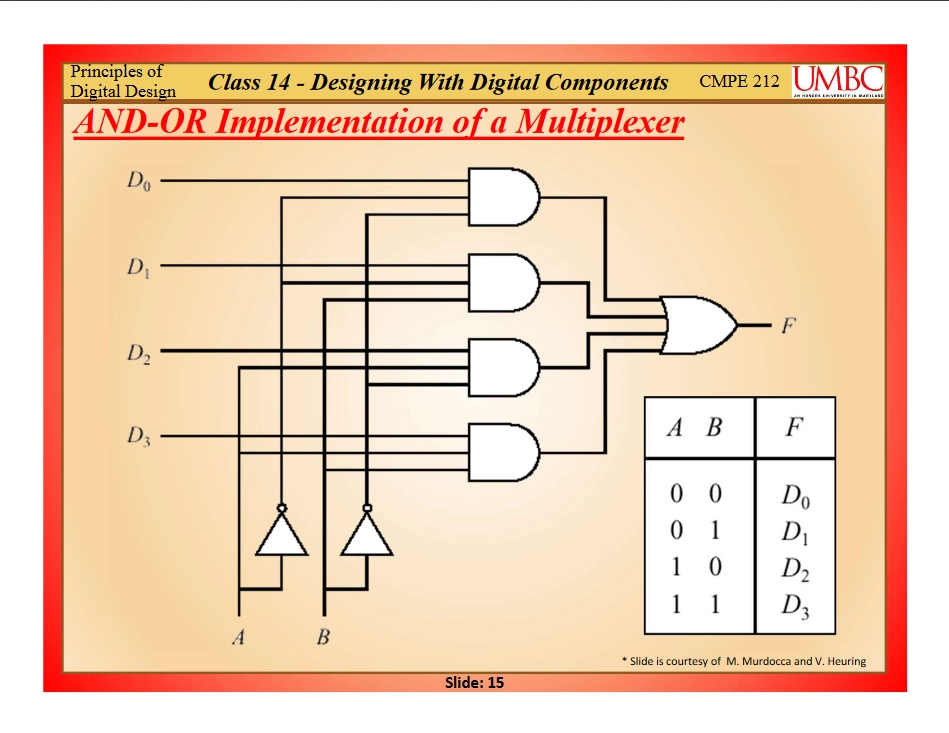

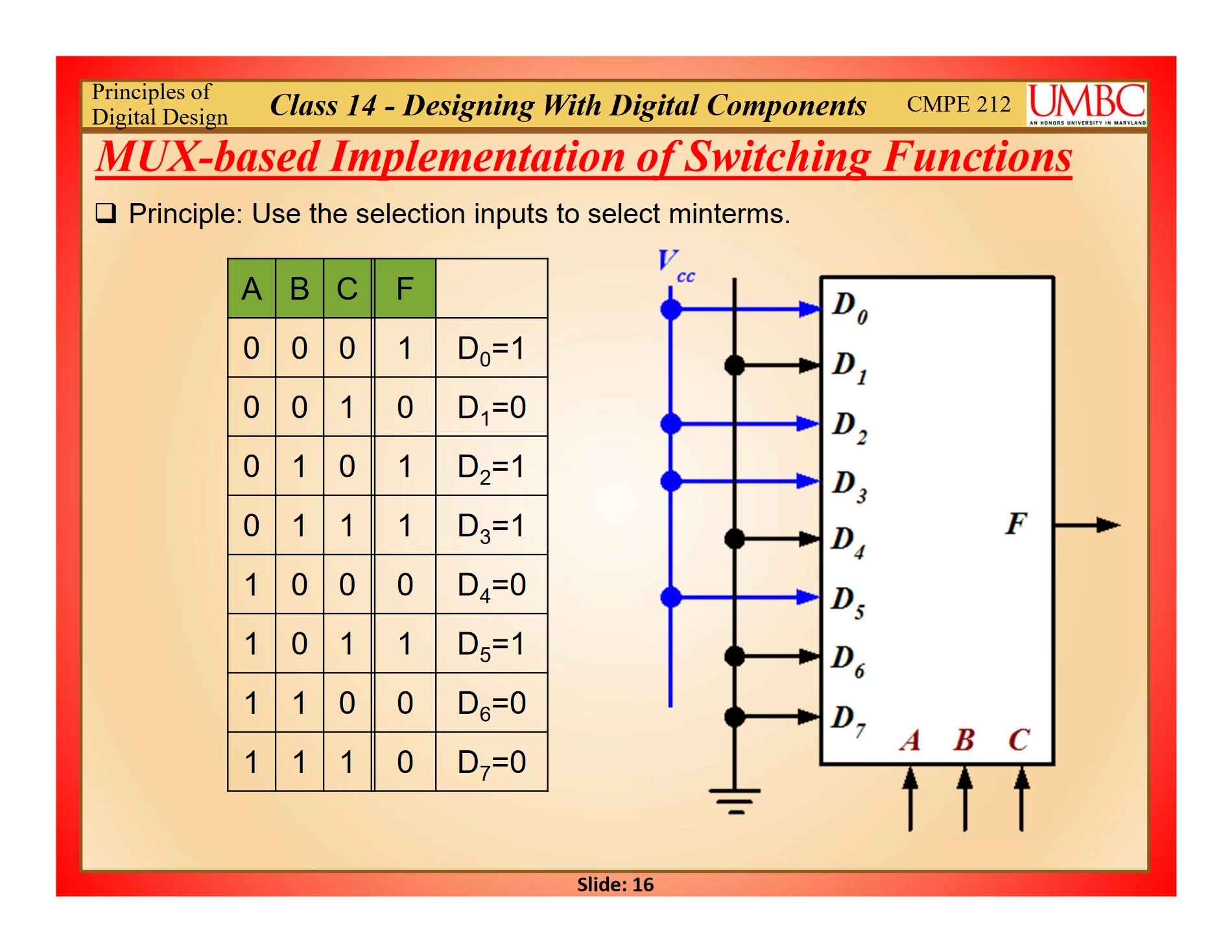

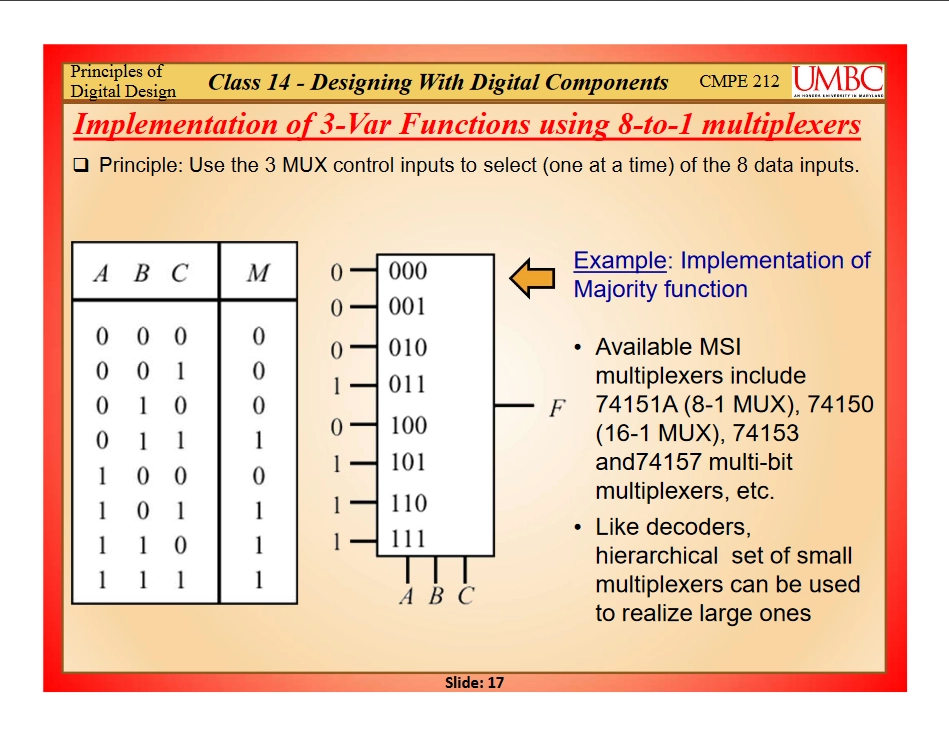

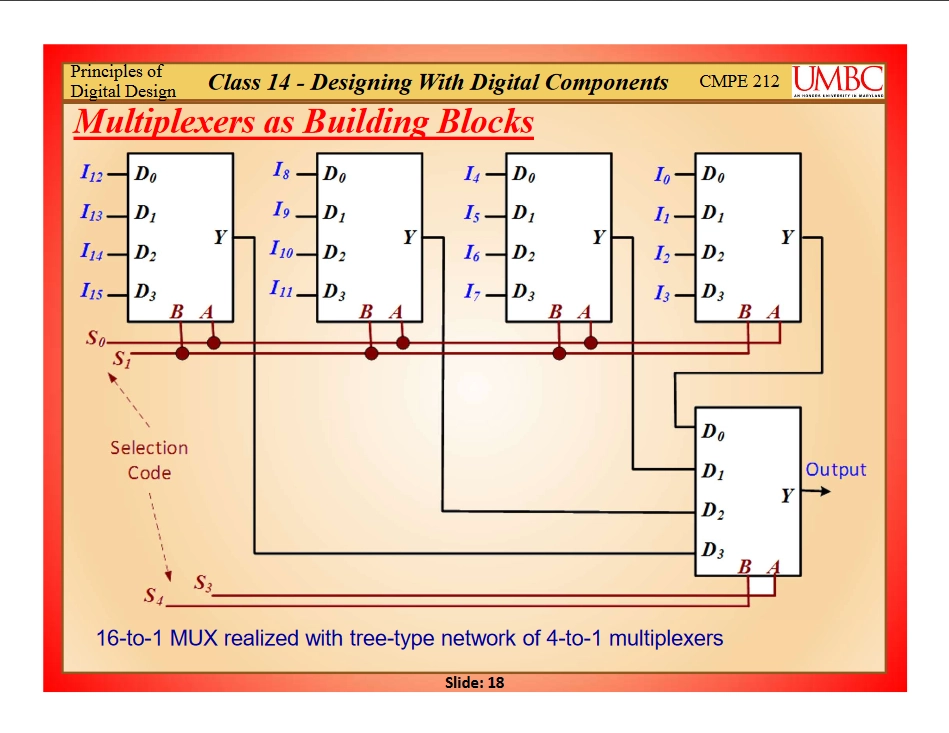

class: 14, slide: 14-18 → Mulitplexer, Building Large Mulitiplexer, Doing a function with one

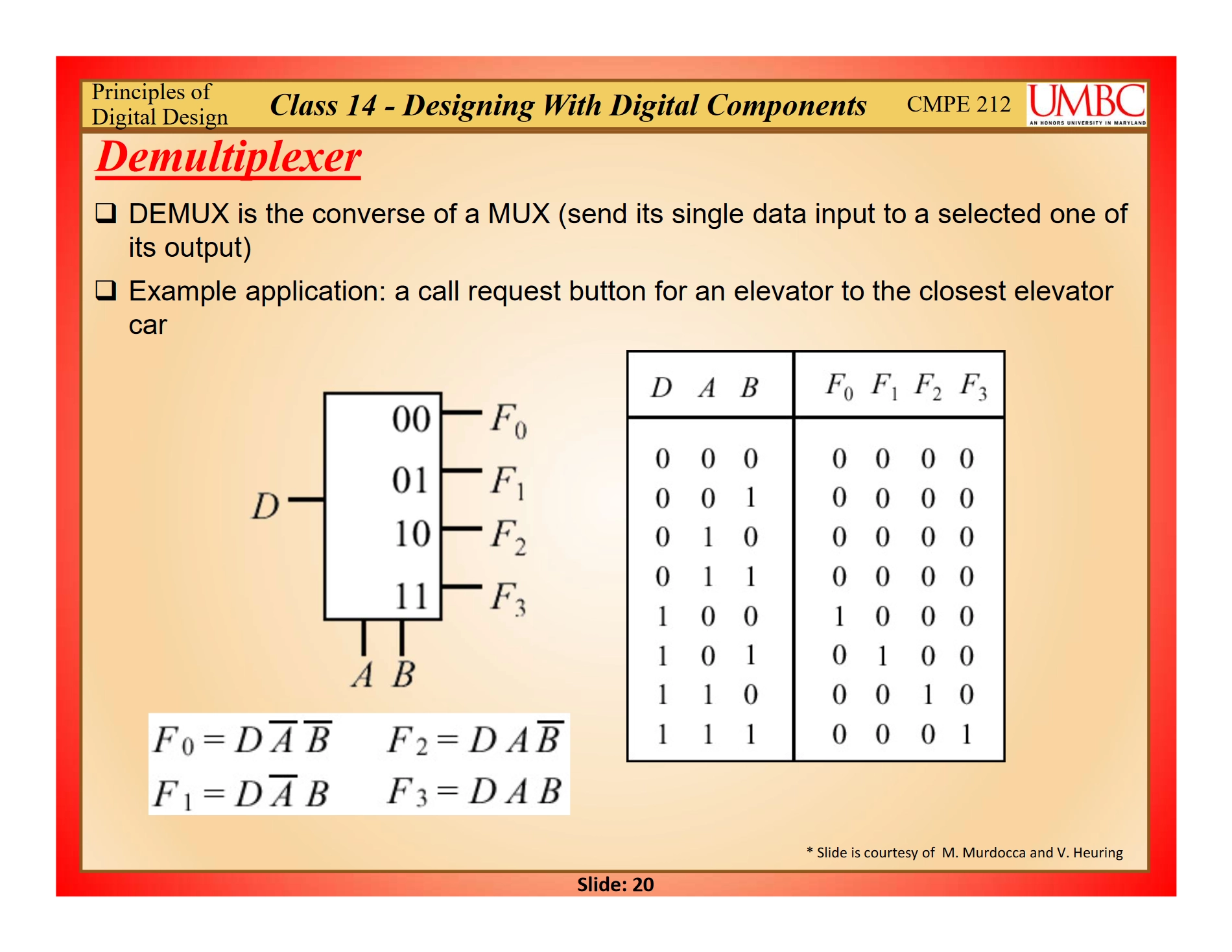

class: 14, slide: 20 → Demultiplexer

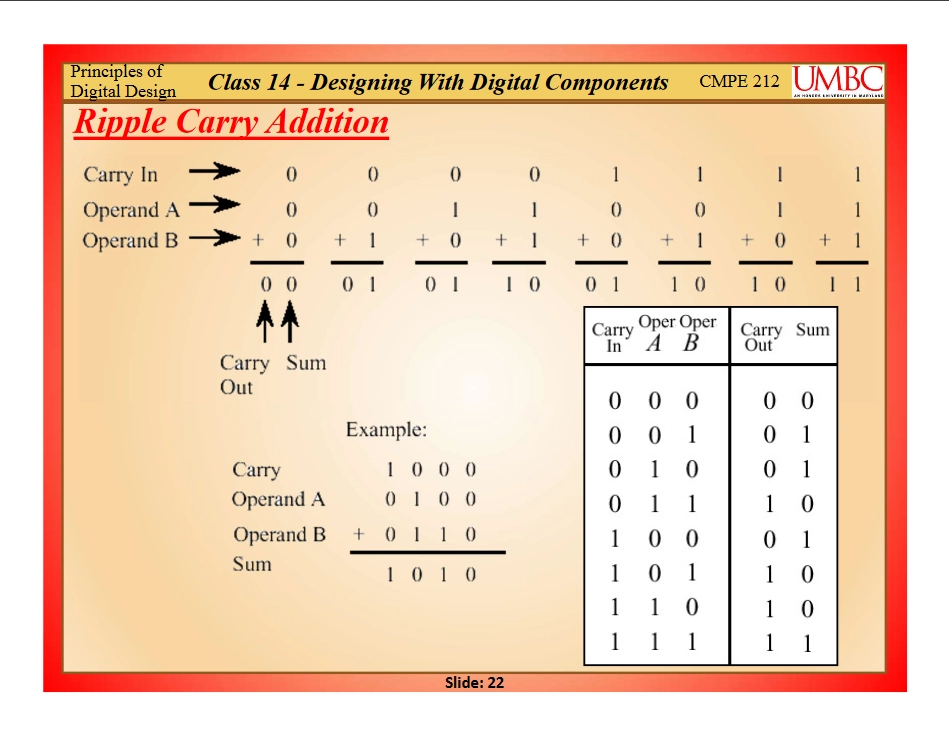

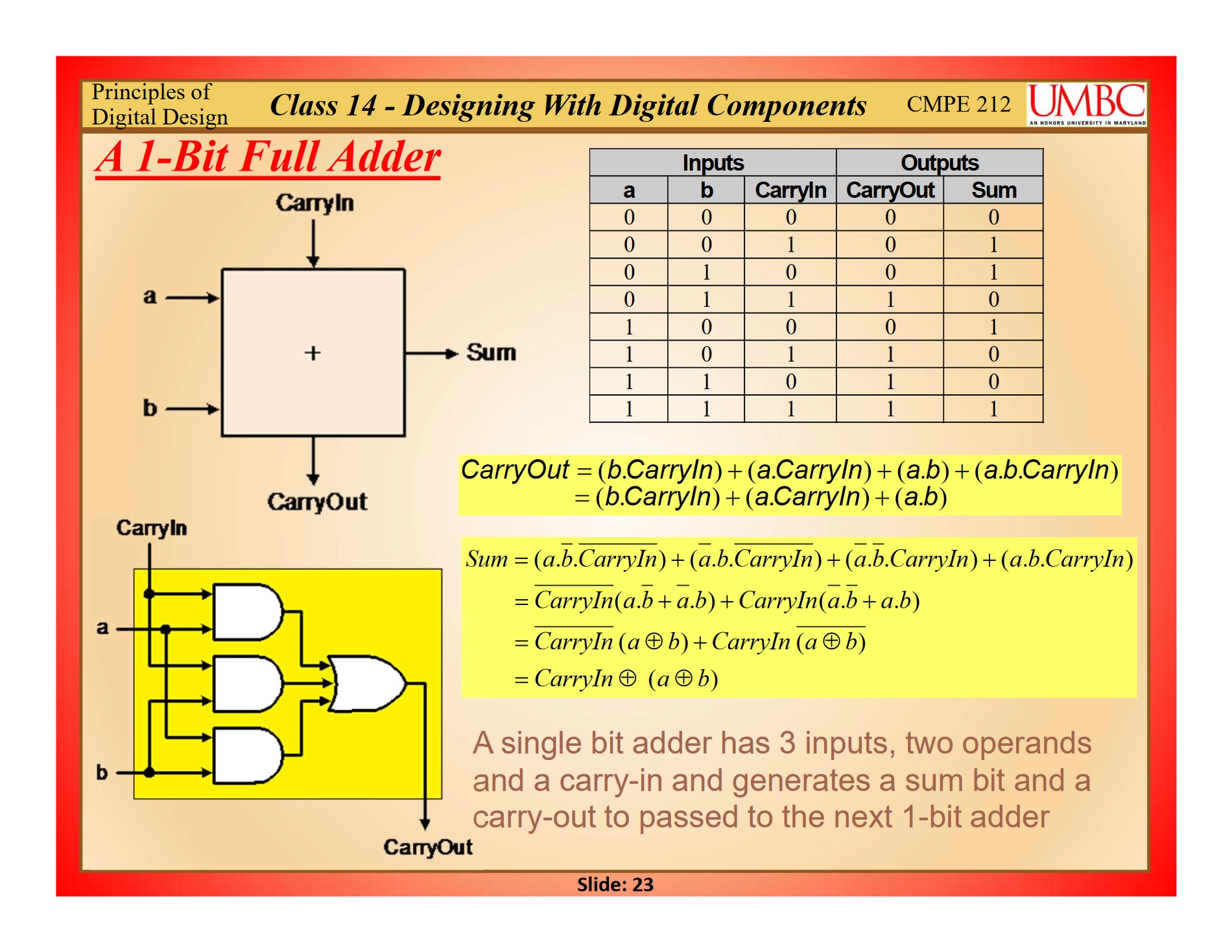

class: 14, slide: 22-23 → Full Adder

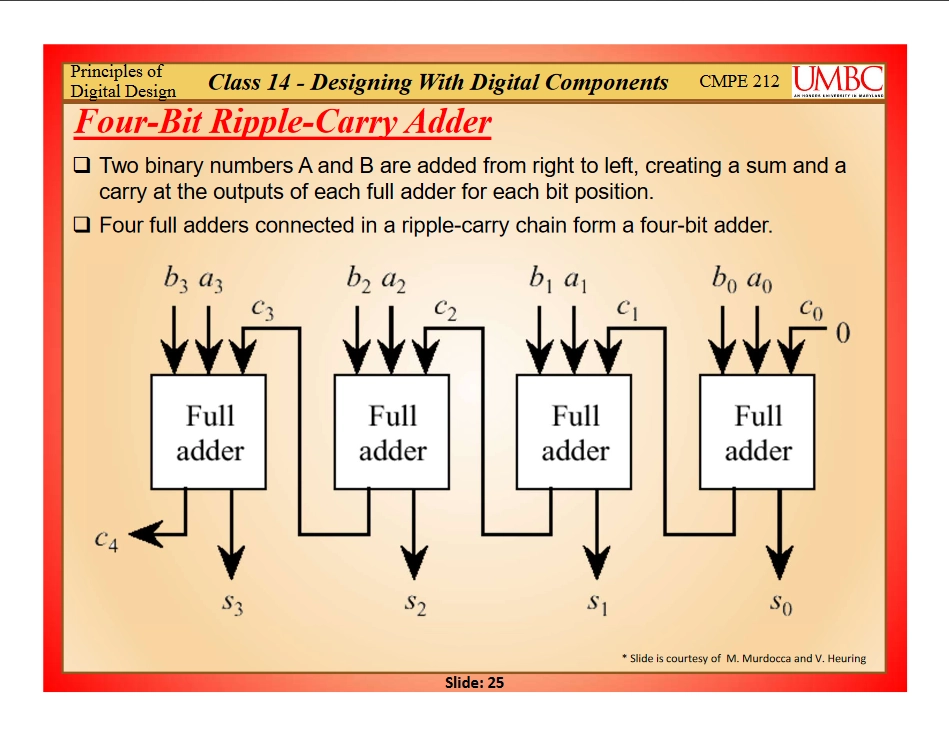

class: 14, slide: 25 → 4 bit ripple carry - adding two numbers

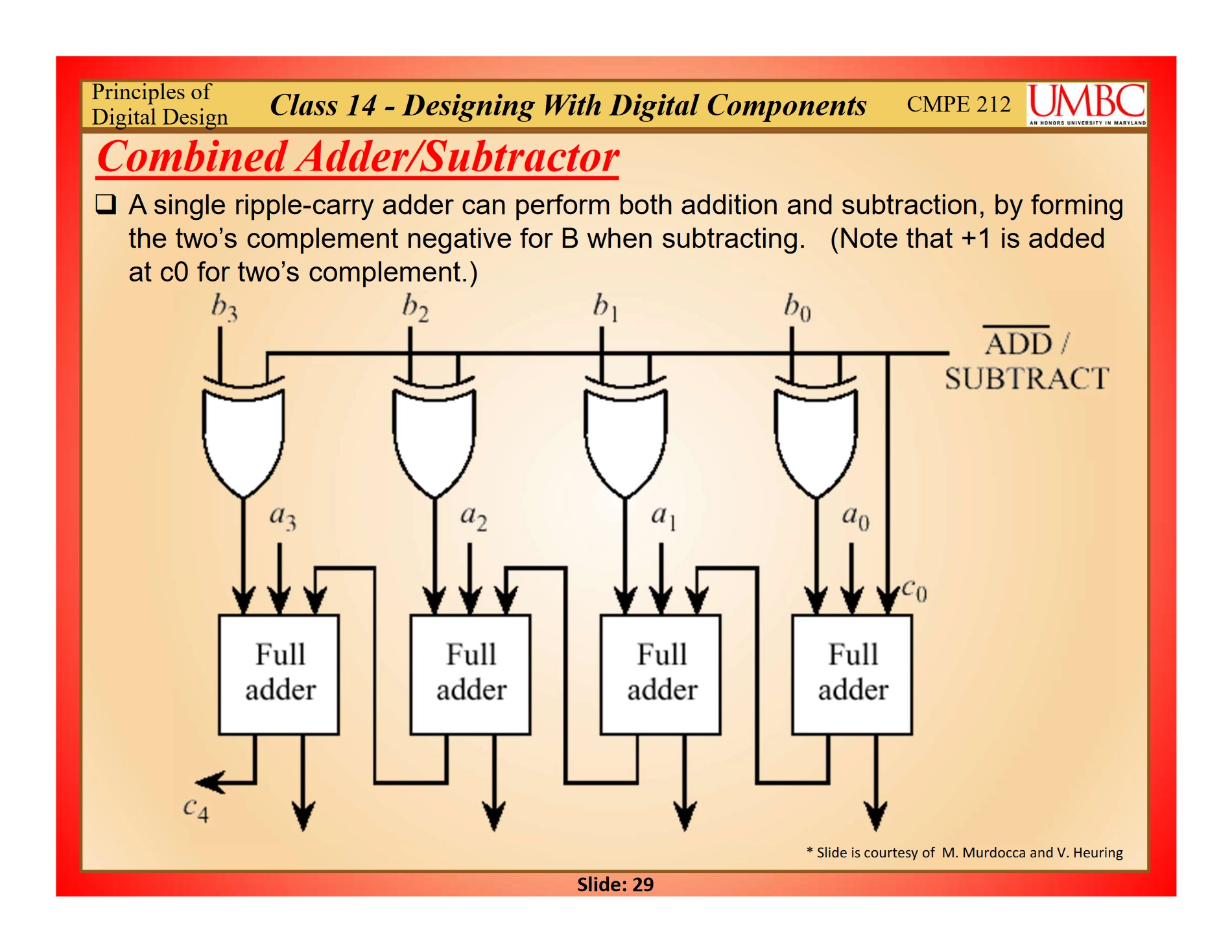

class: 14, slide: 29 → 4 bit combined Adder/Subtractor

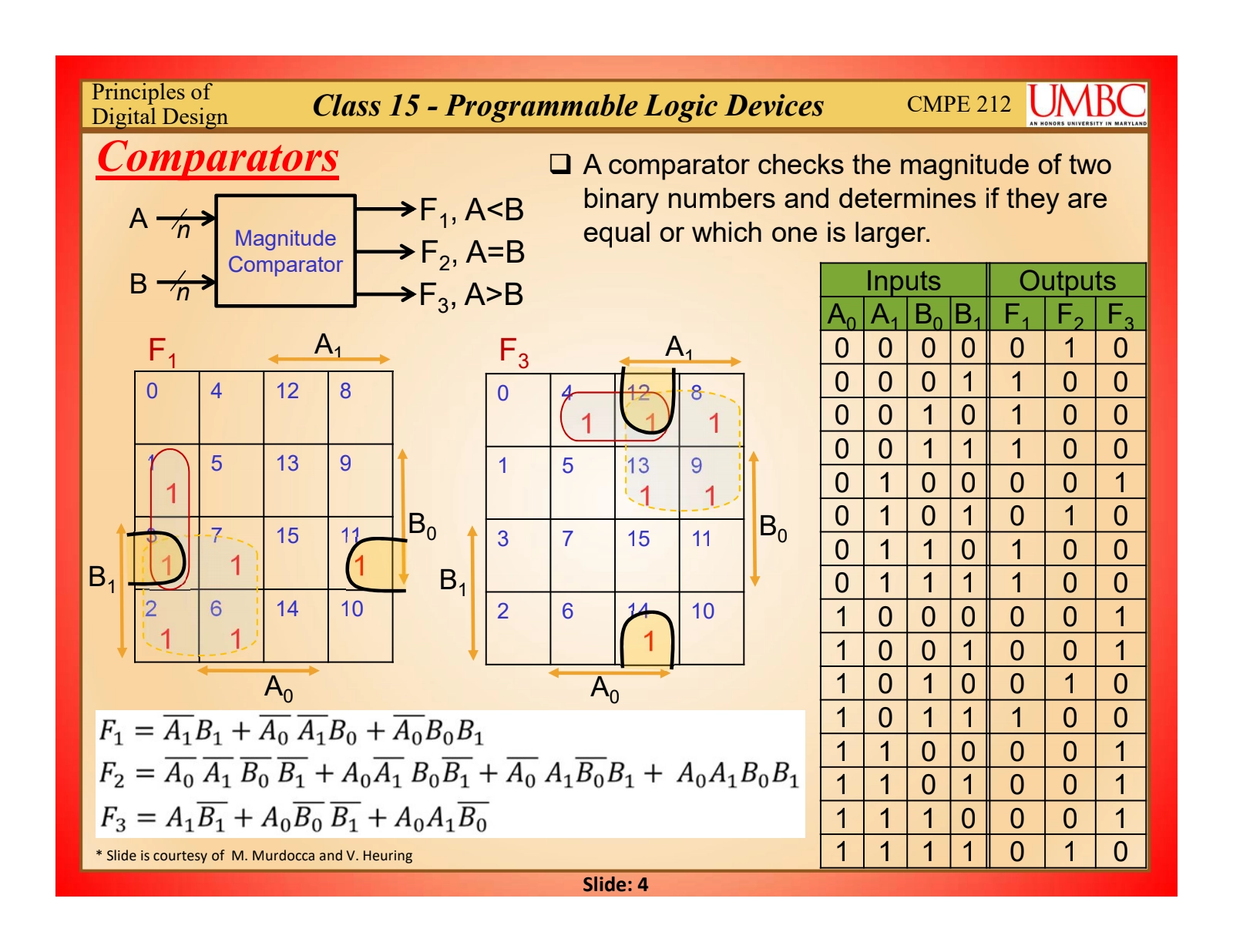

class: 15, slide: 4 → Comparators

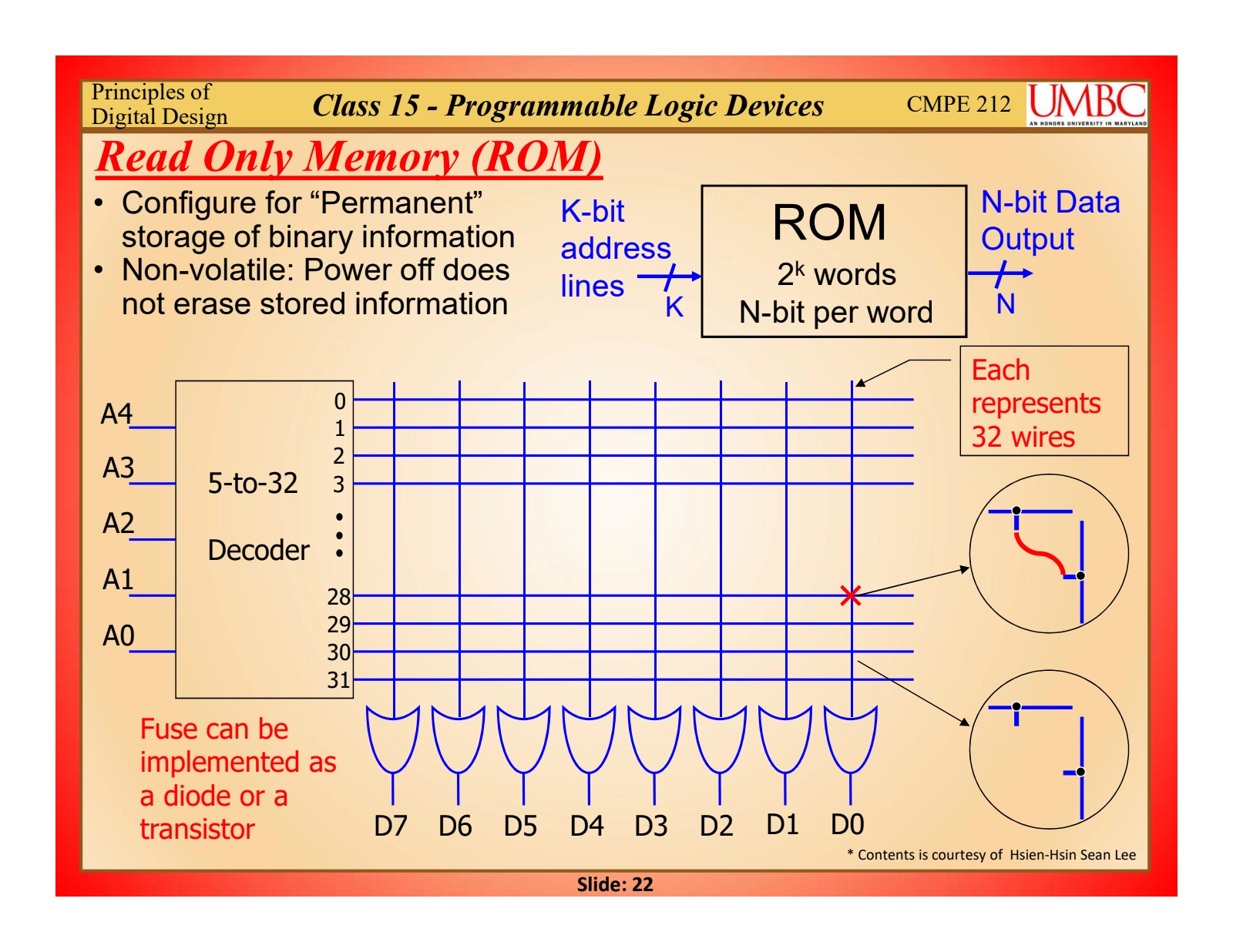

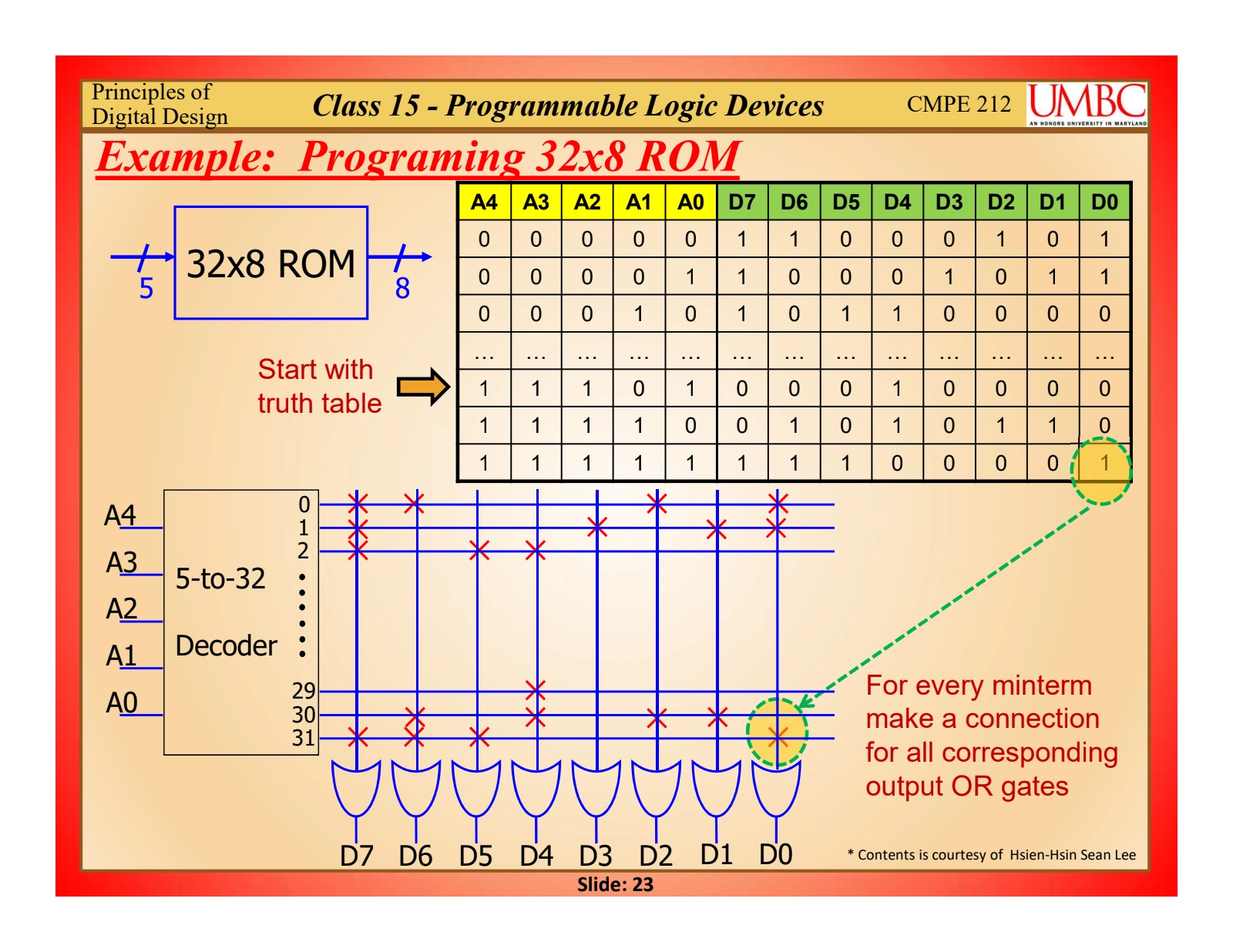

class: 15, slide: 22-23 → ROM - given a table bill in the connections

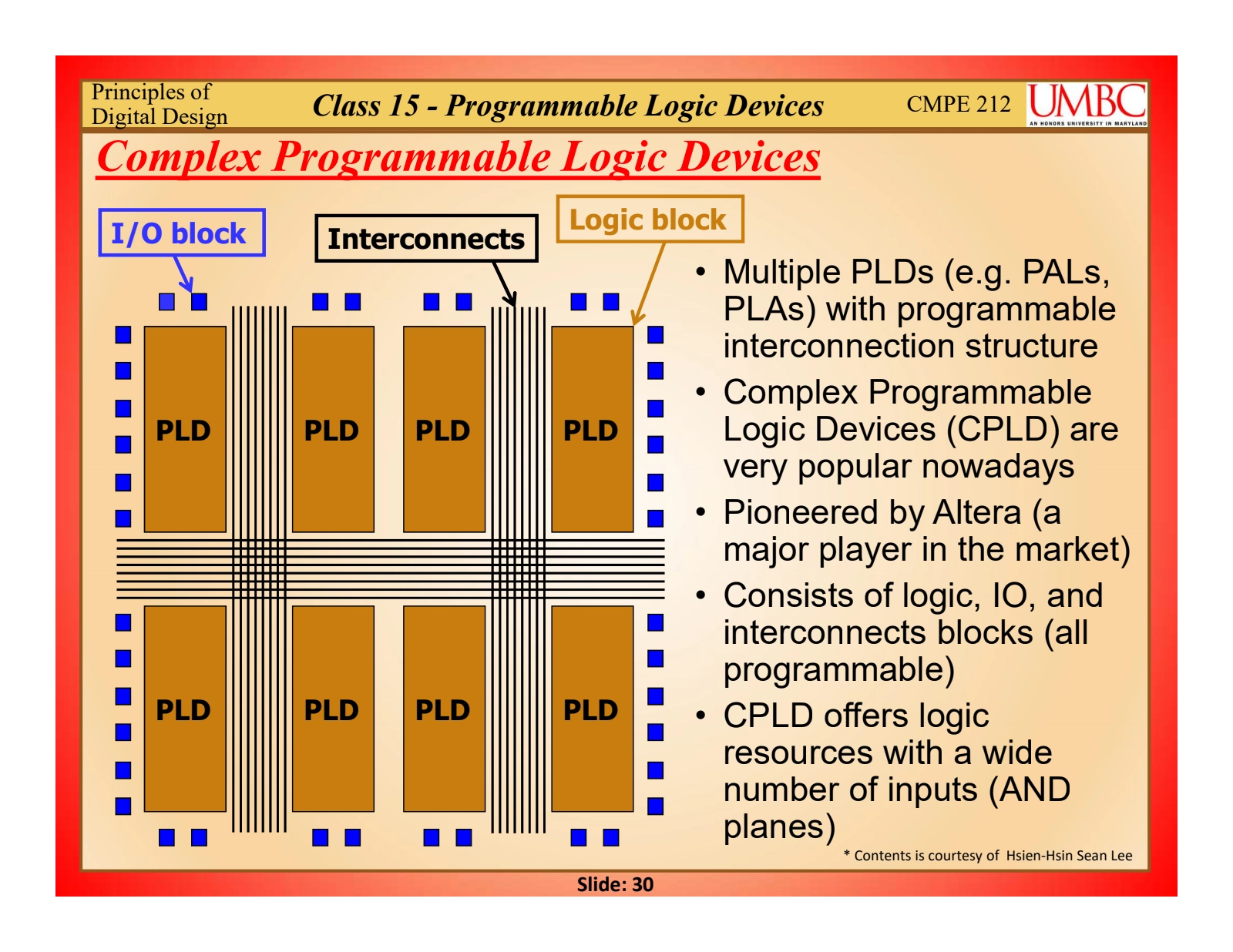

class: 15, slide: 30 → CPLD

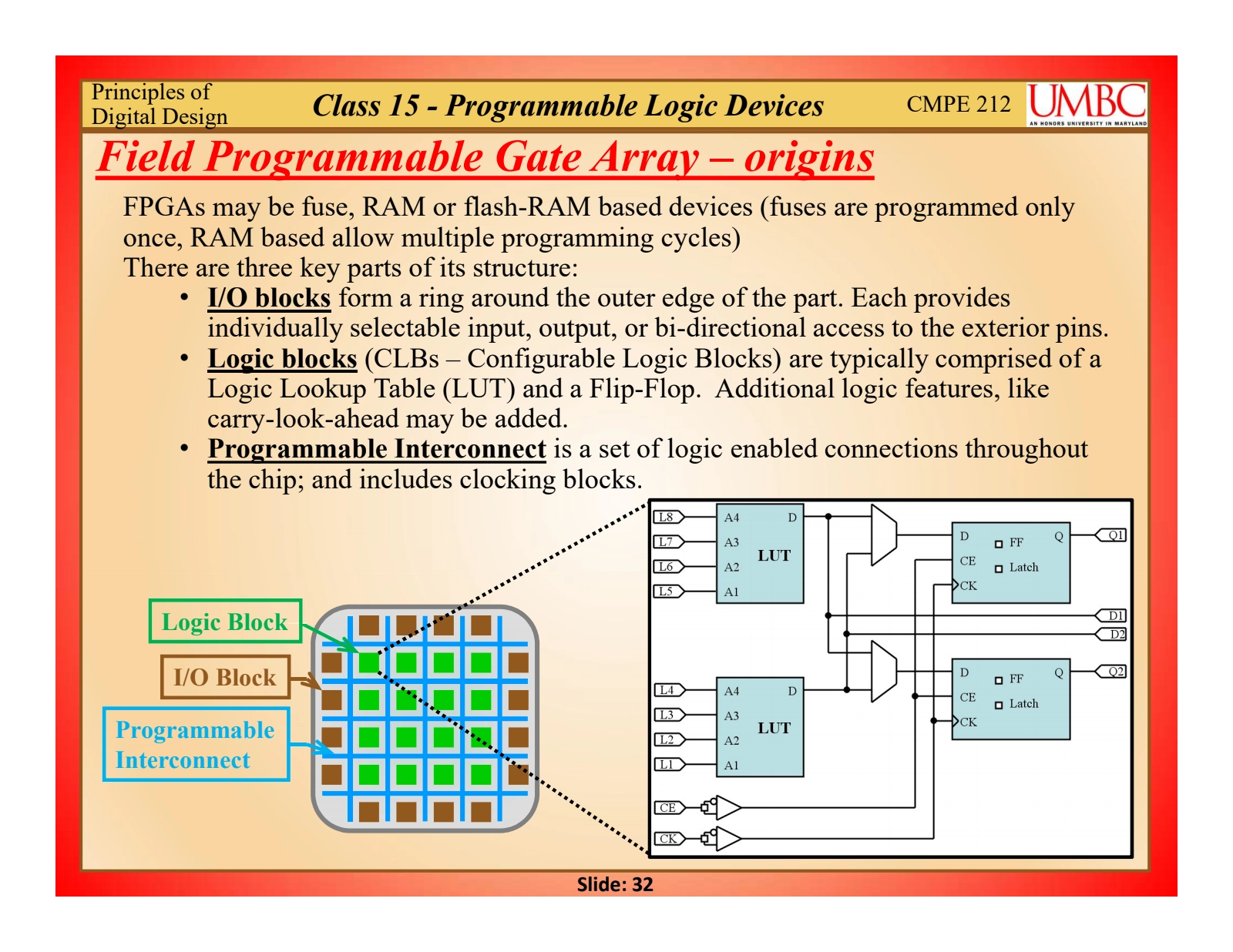

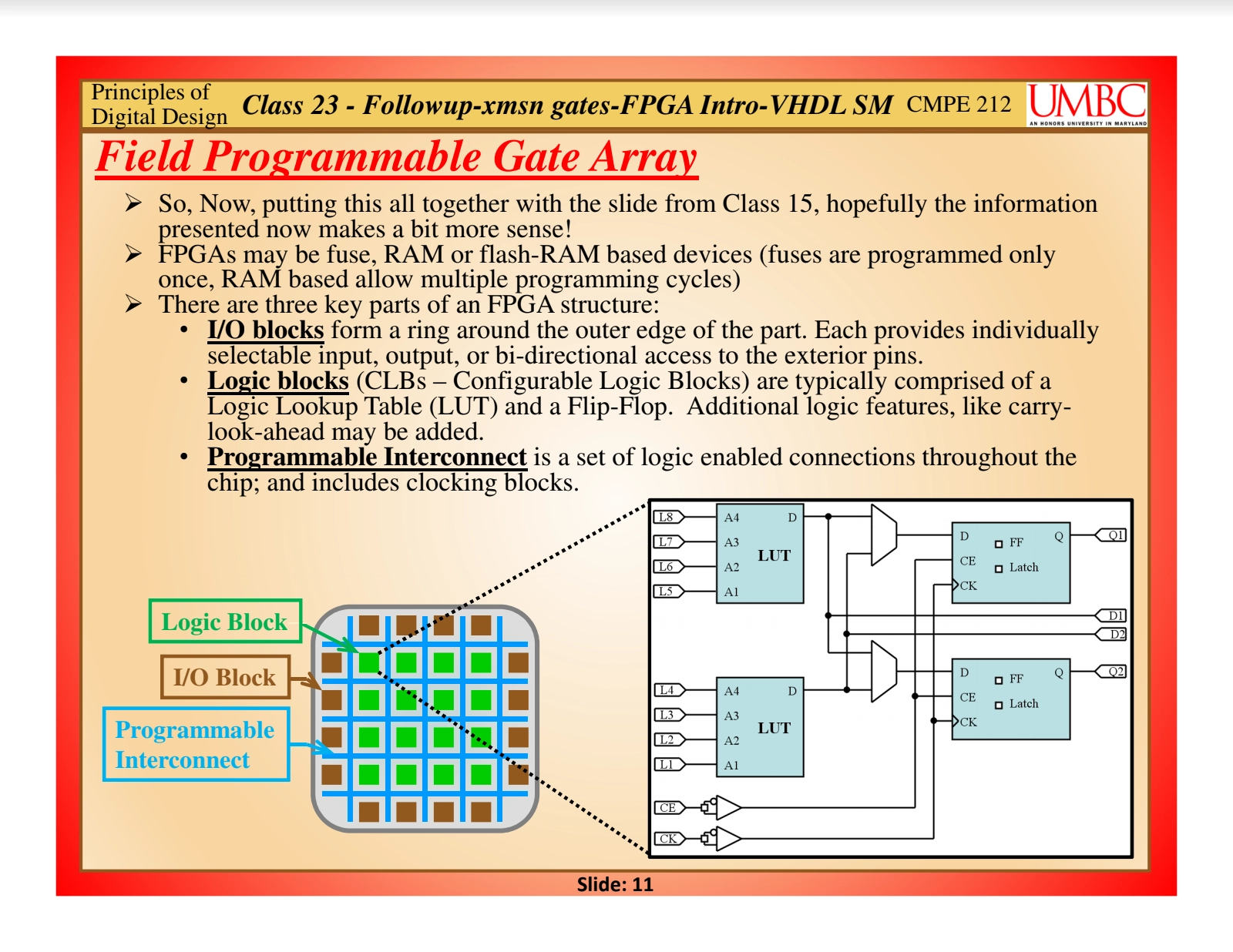

class: 15, slide: 32 → FPGA

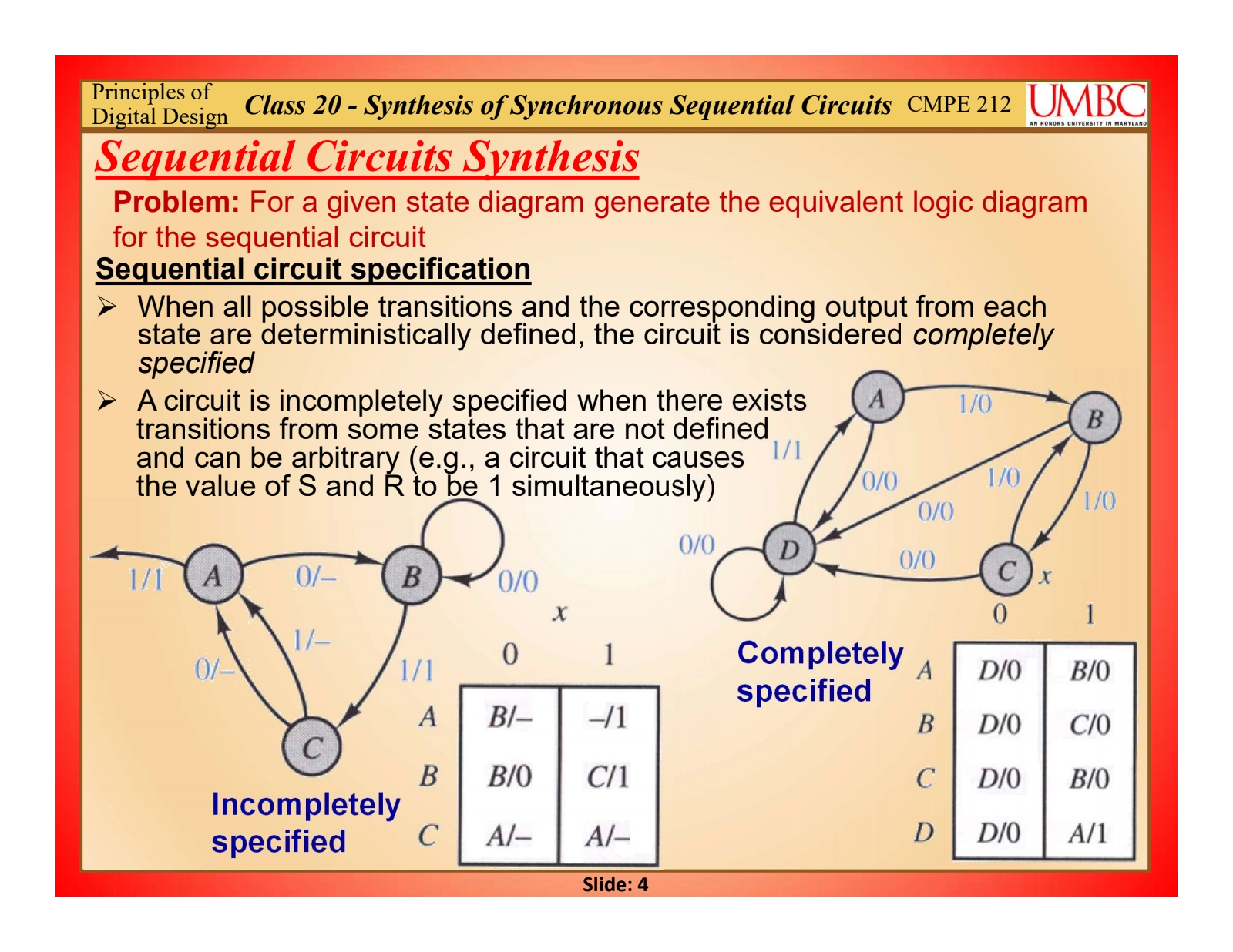

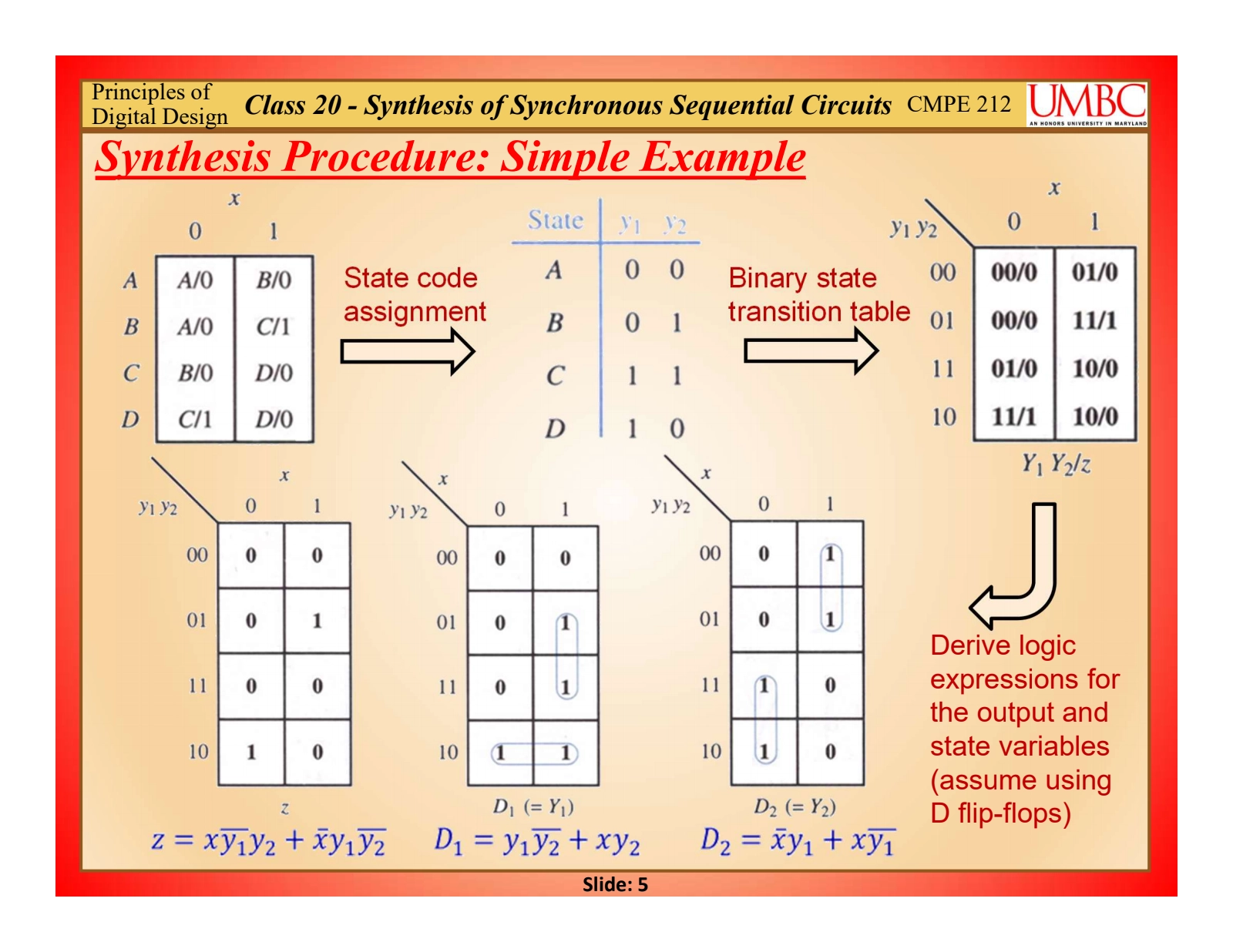

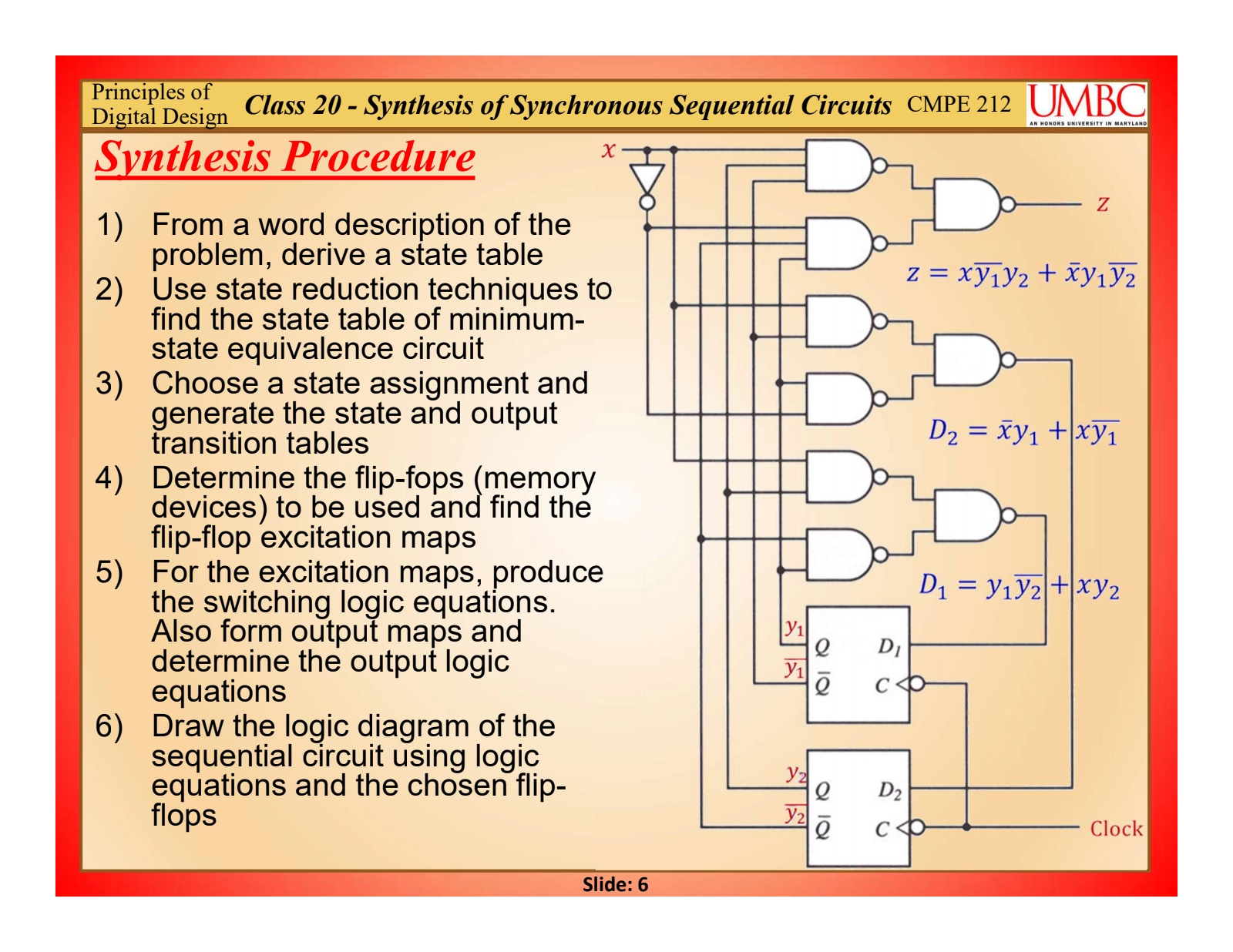

class: 20, slide: 4-6 → D-Type state machine logic design

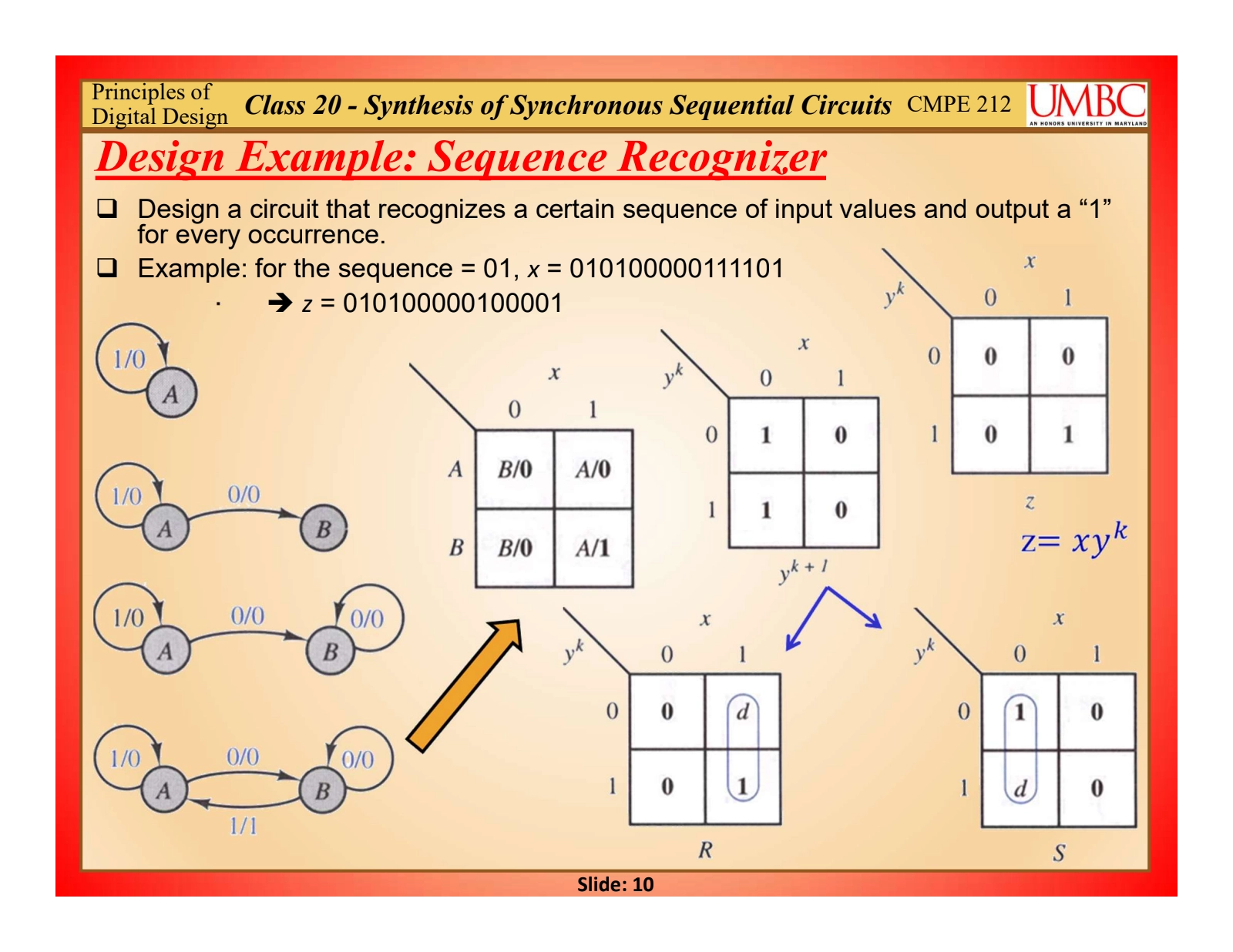

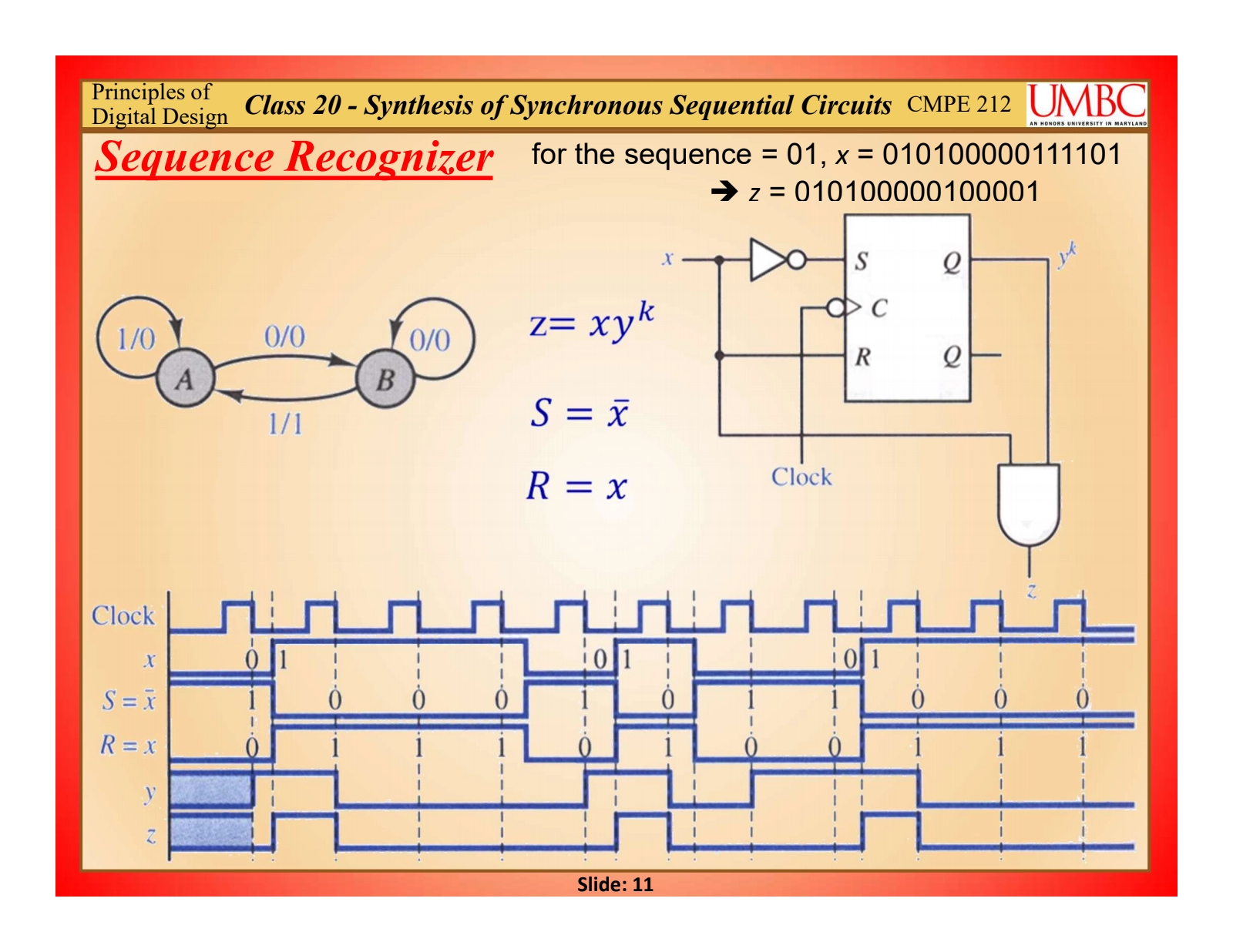

class: 20, slide: 10-11 → SR Type state machine logic design (2 state)

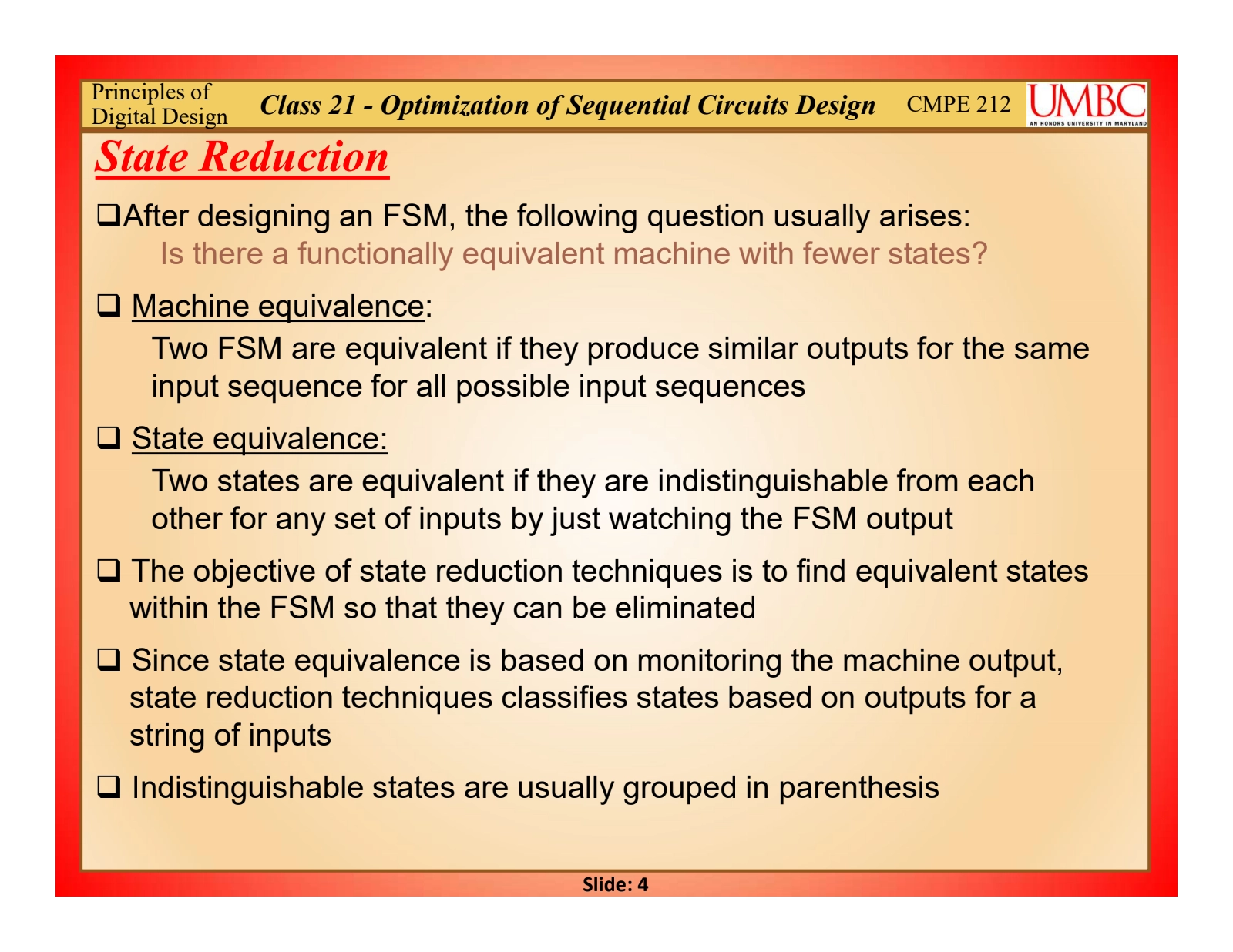

class: 21, slide: 4 → State Reduction Principals

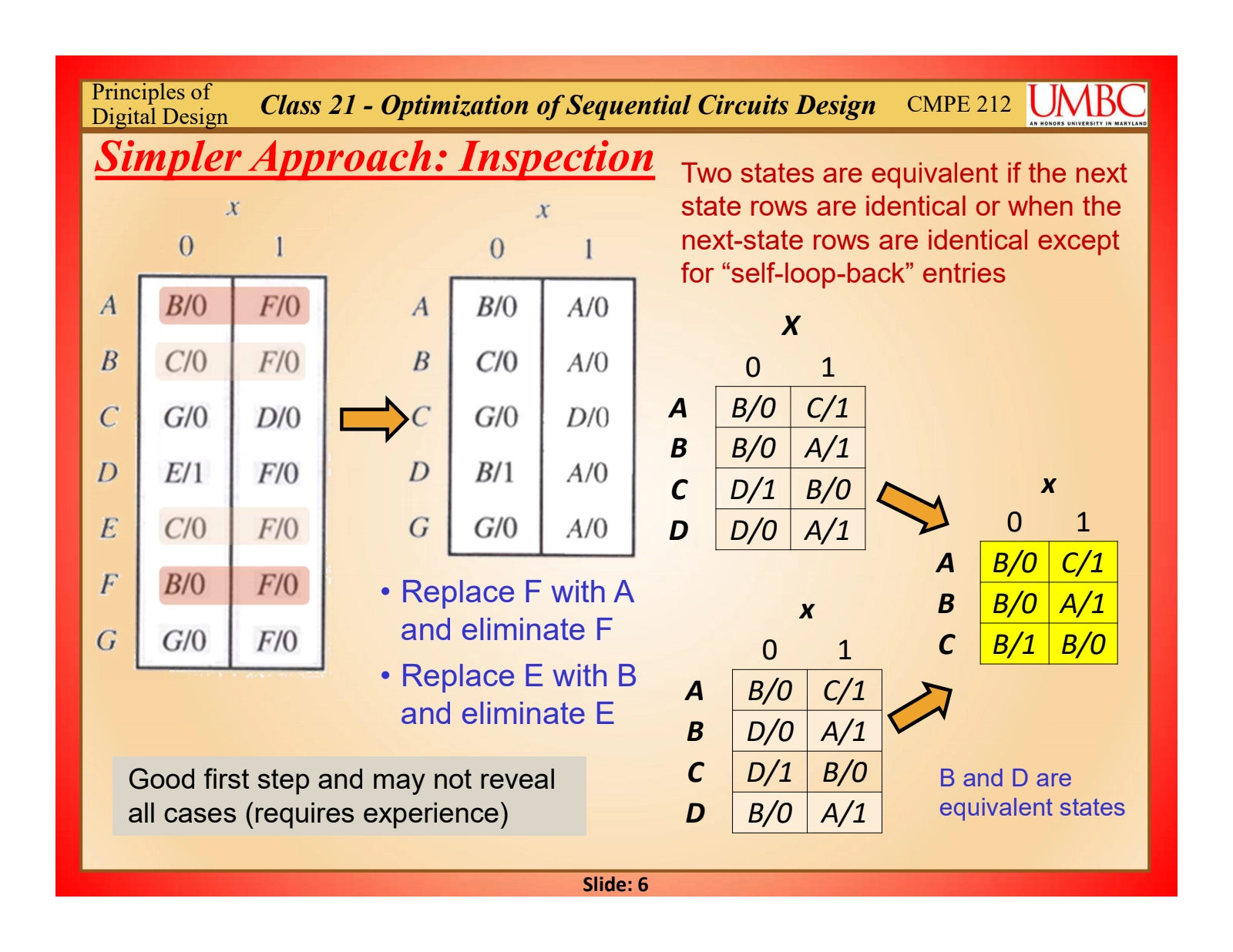

class: 21, slide: 6 → State Reduction by Inspection

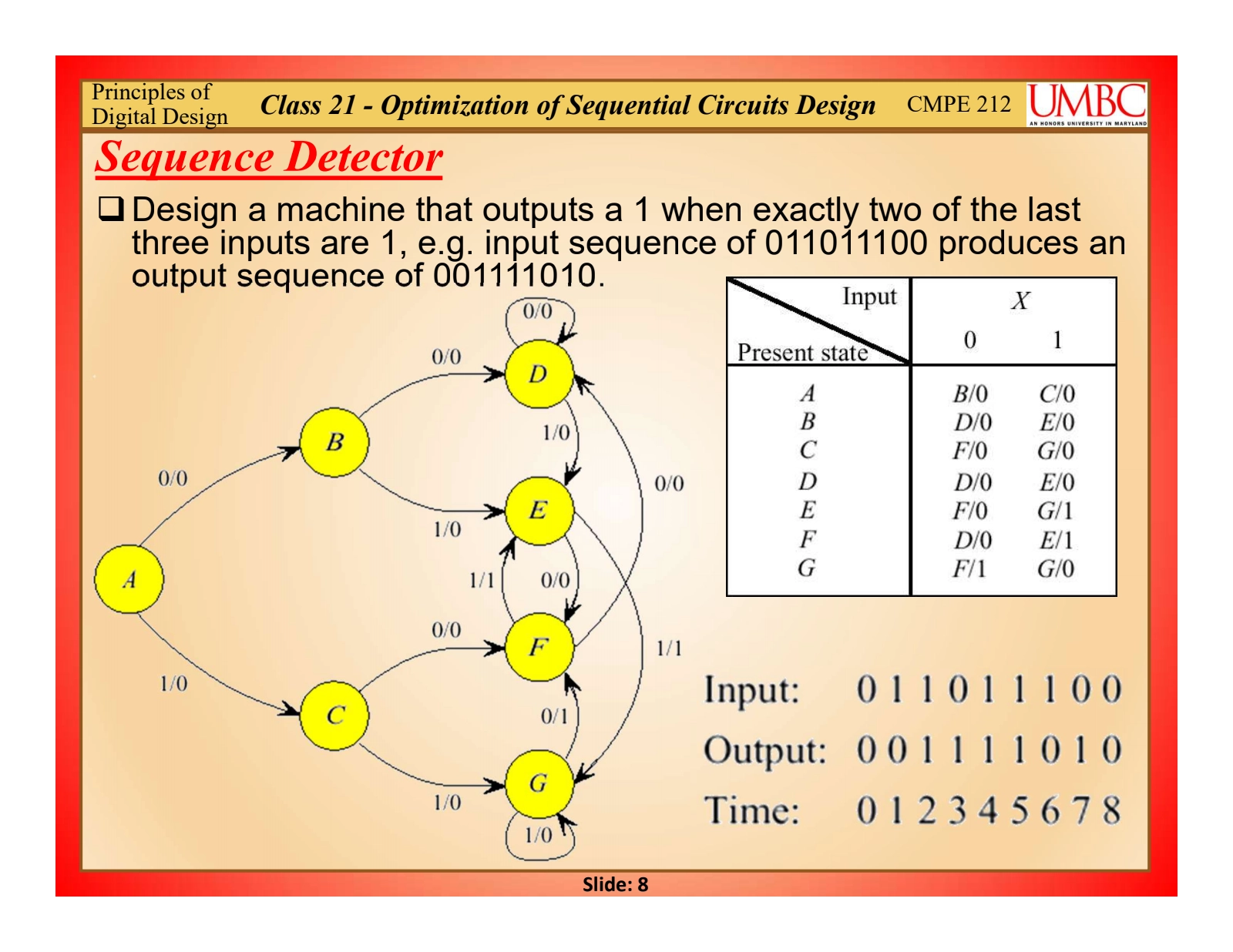

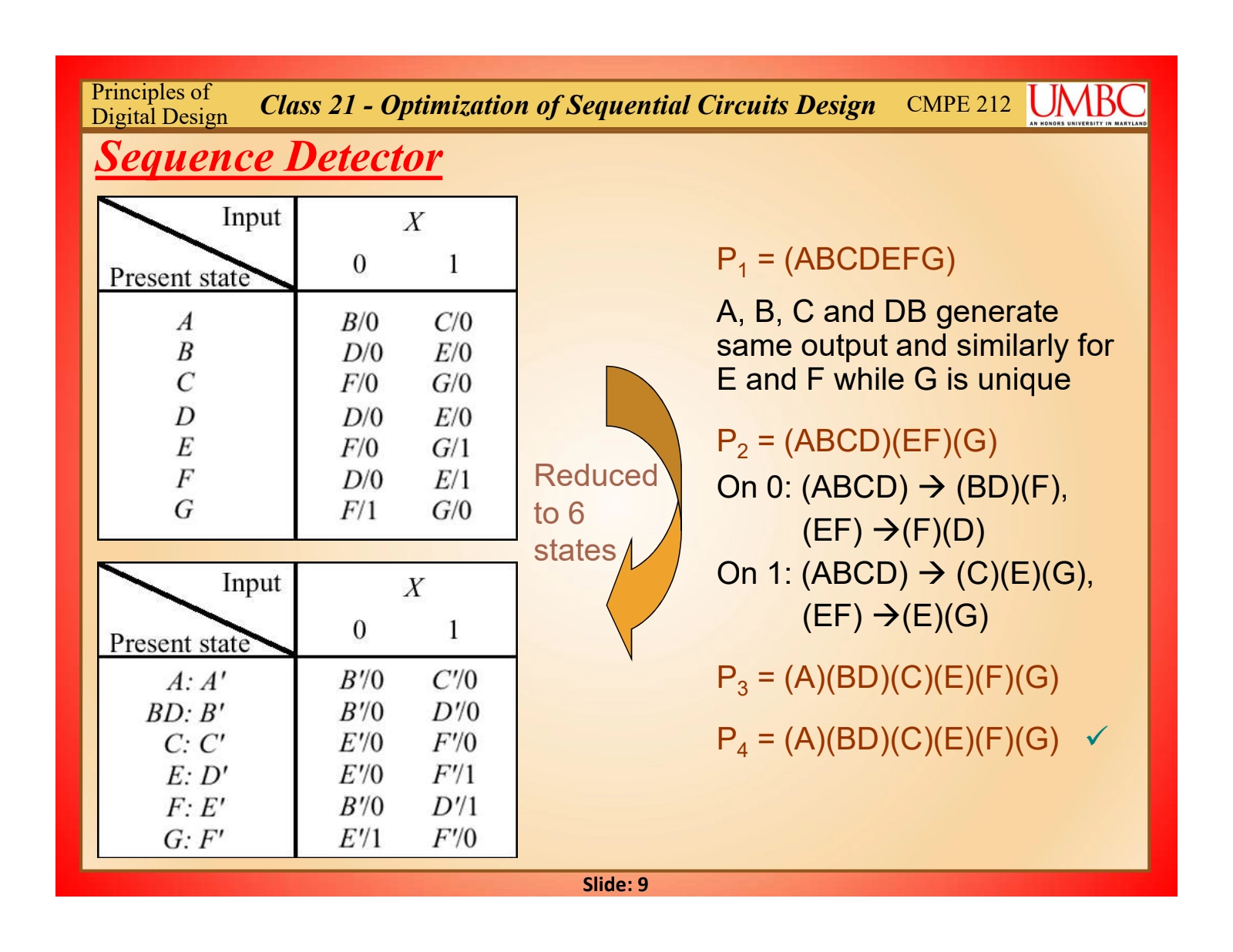

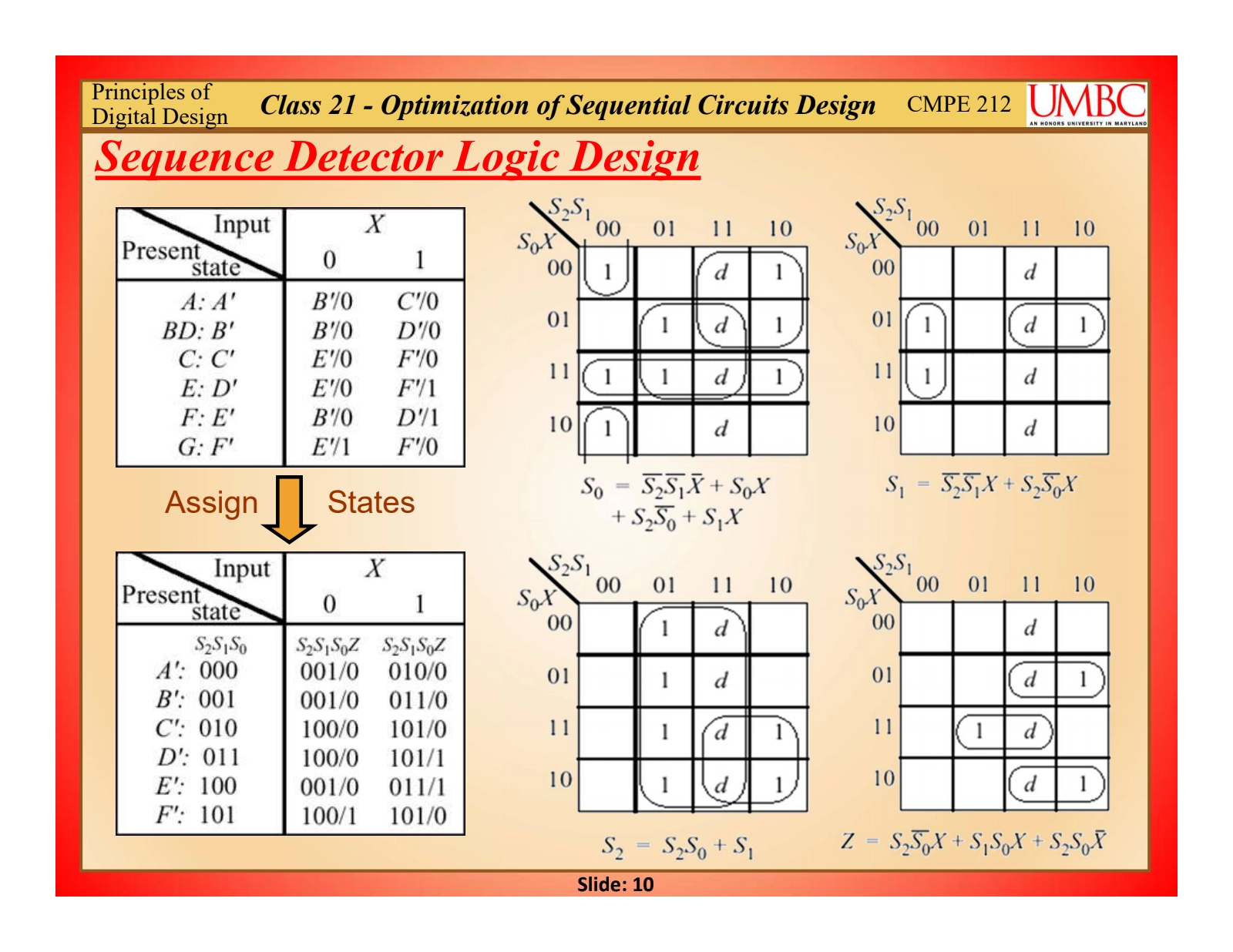

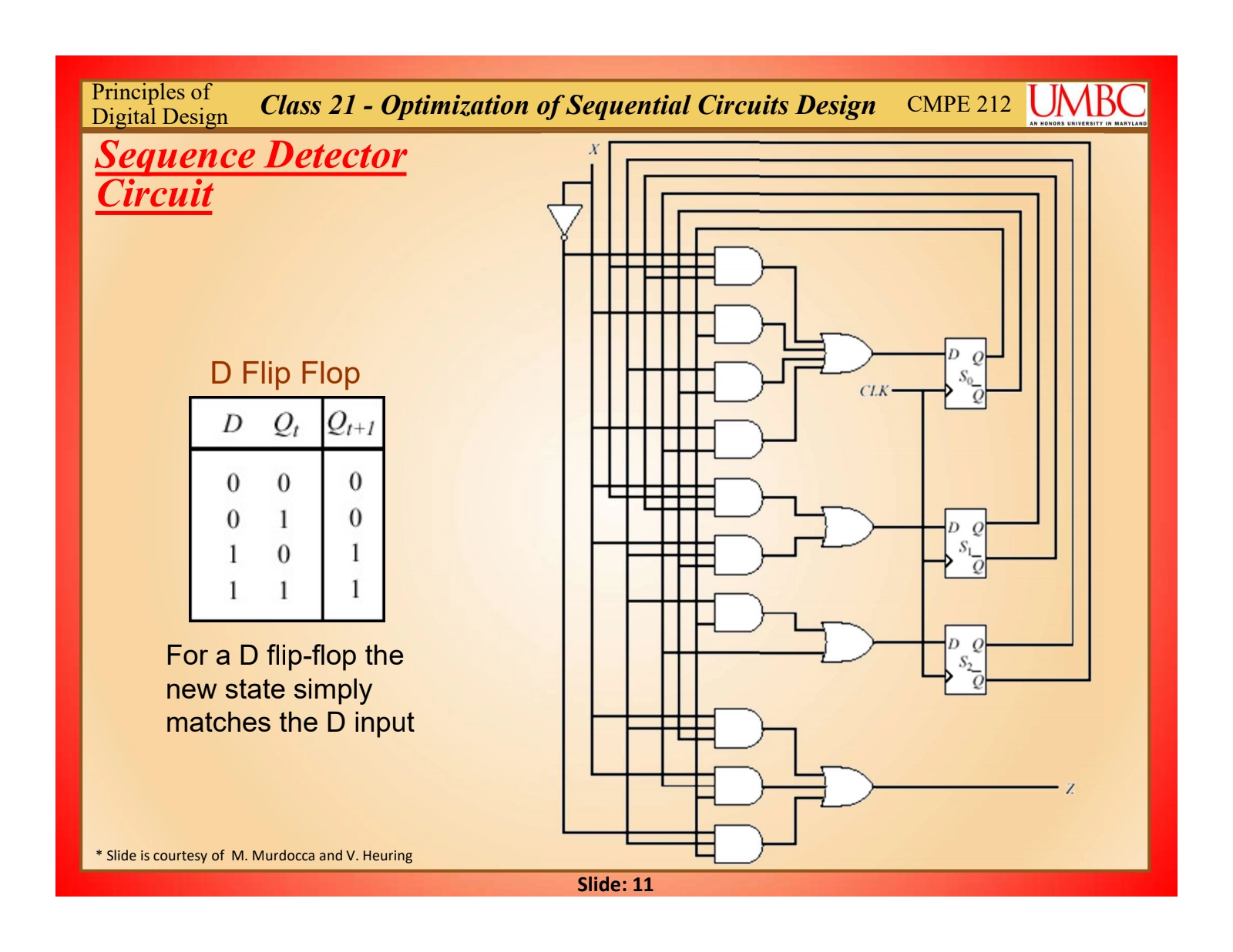

class: 21, slide: 8-11 → Sequence Detector example (thru Circuit Des)

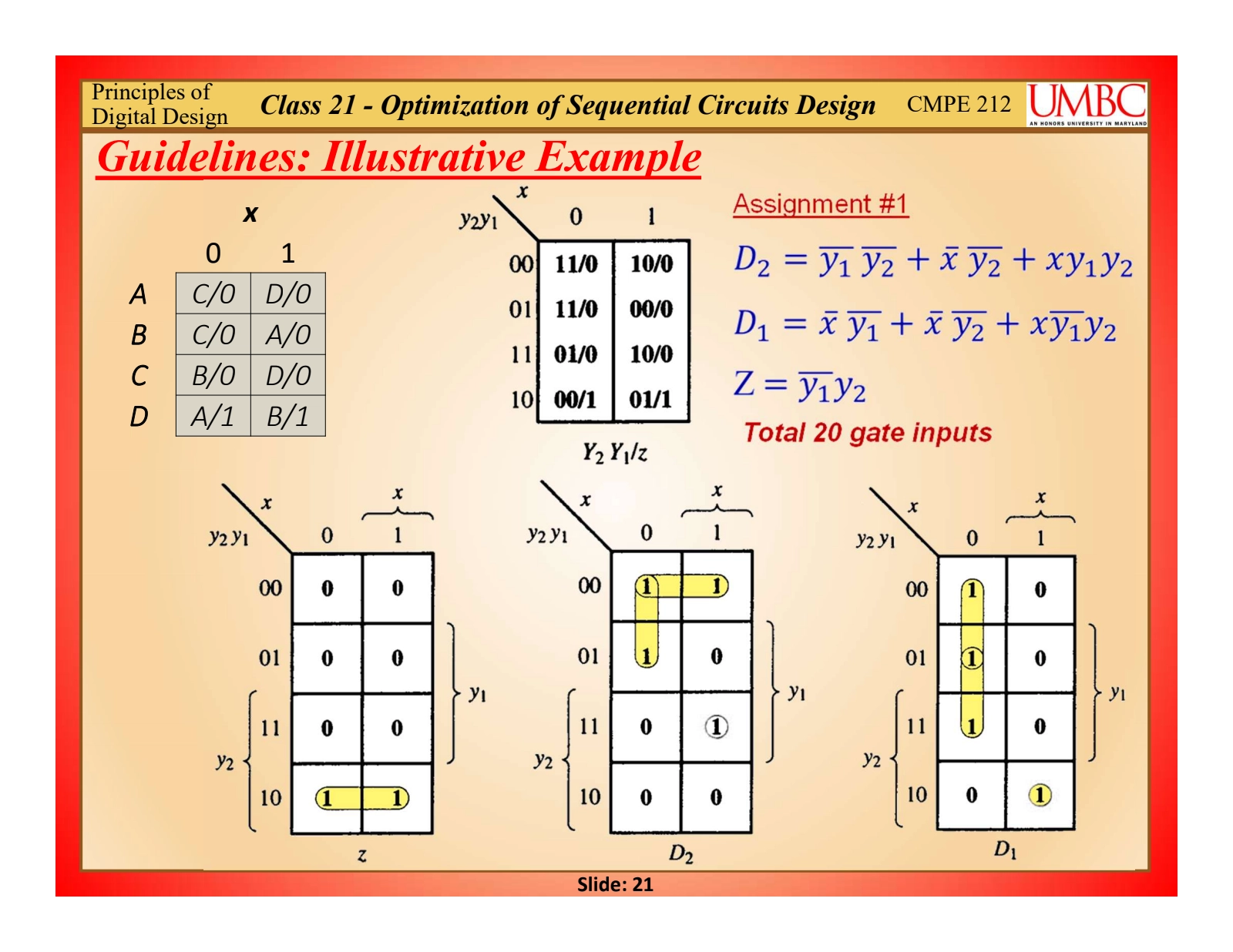

class: 21, slide: 21 → Optimal State Design Characteristics

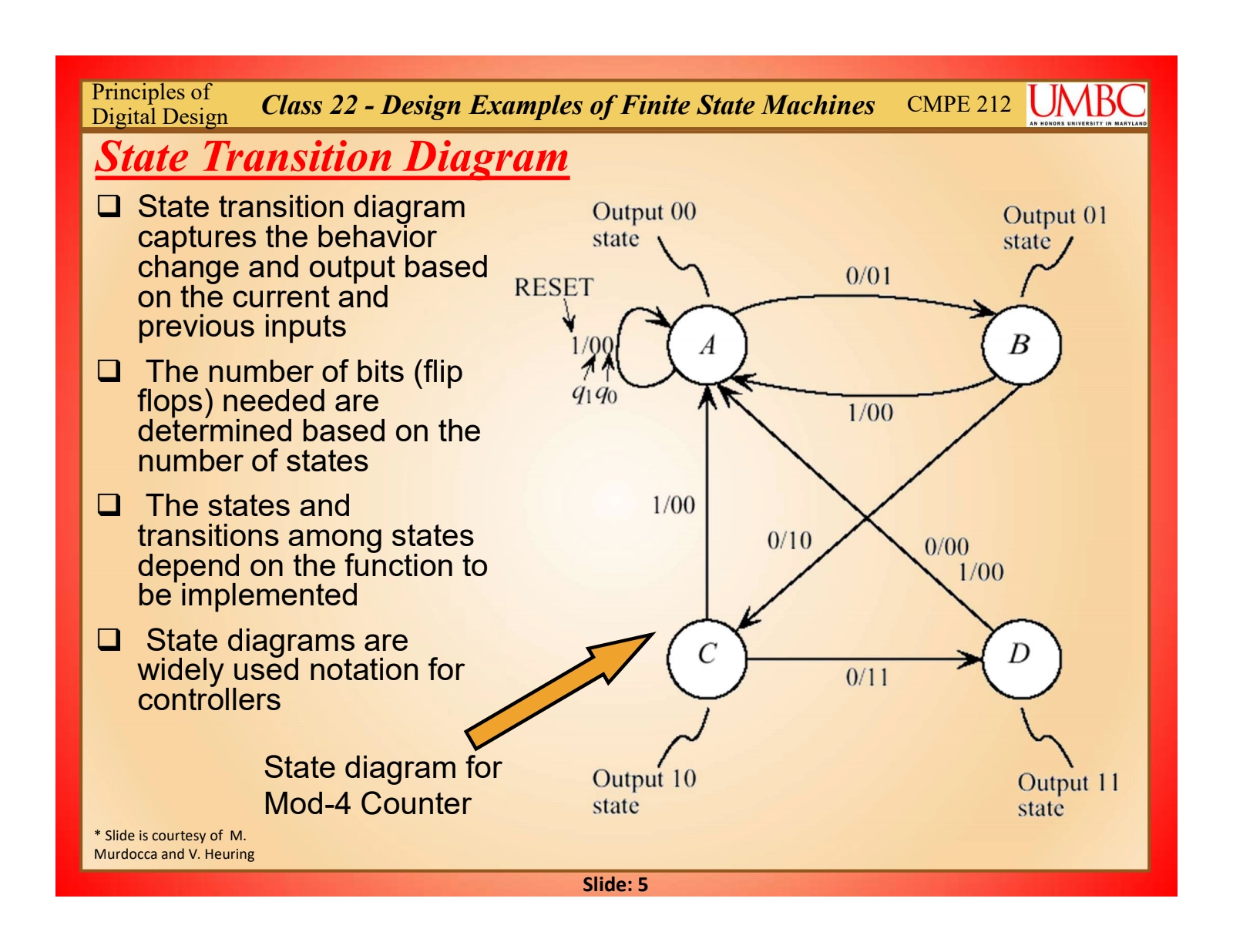

class: 22, slide: 21 → State Machine Example: Mod 4

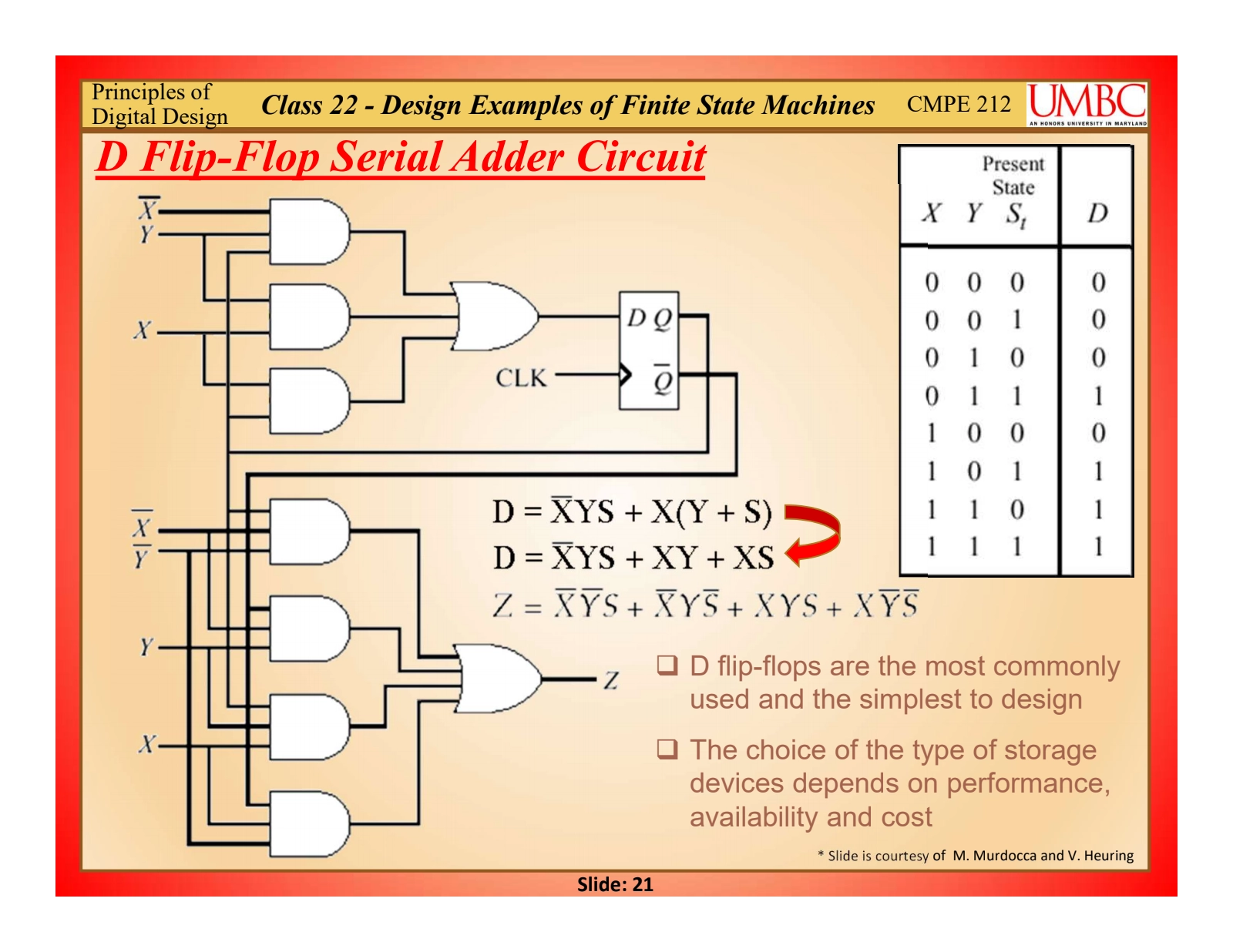

class: 22, slide: 5 → State Machine Example: Serial Adder (JK & D)

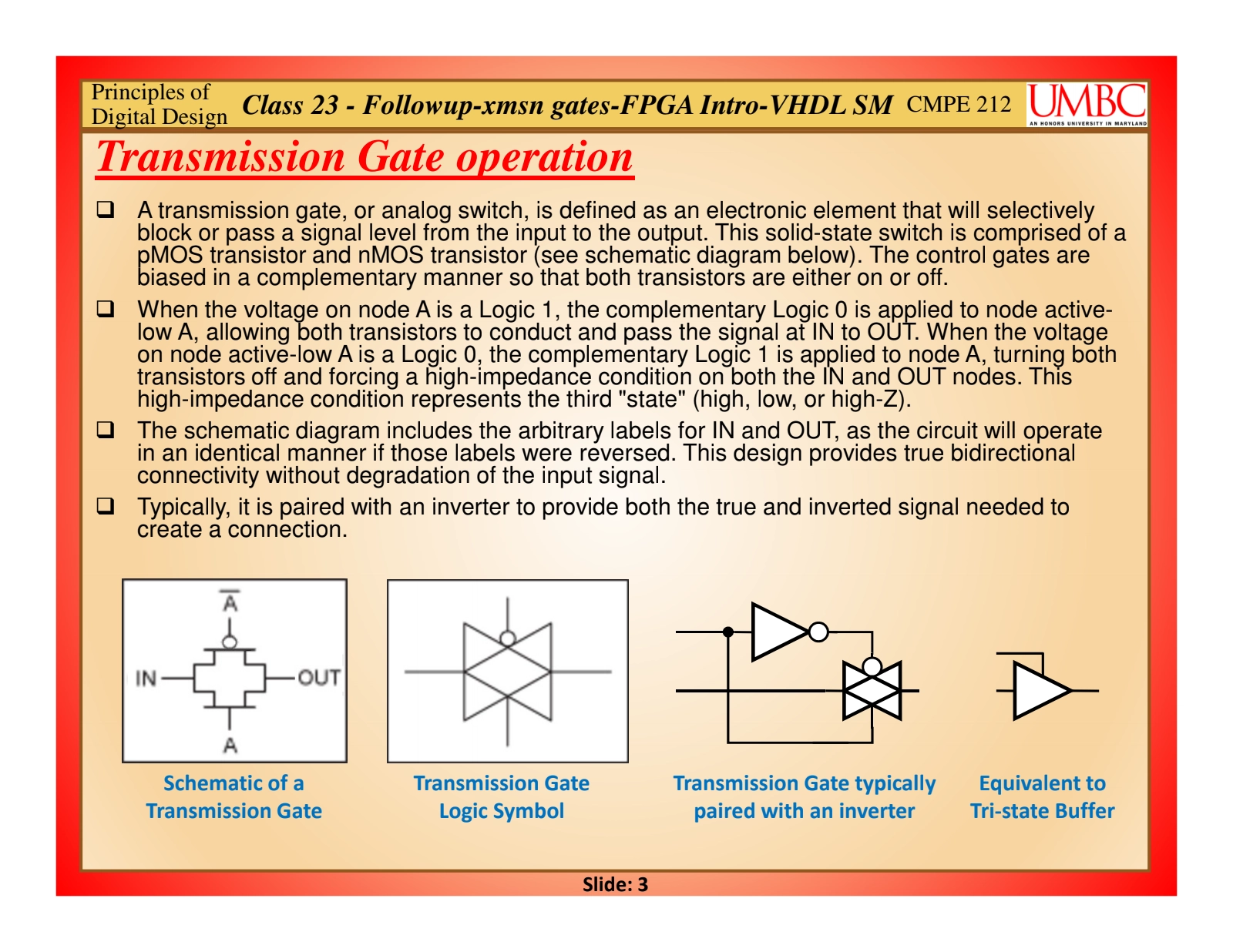

class: 23, slide: 3 → Transmission Gates

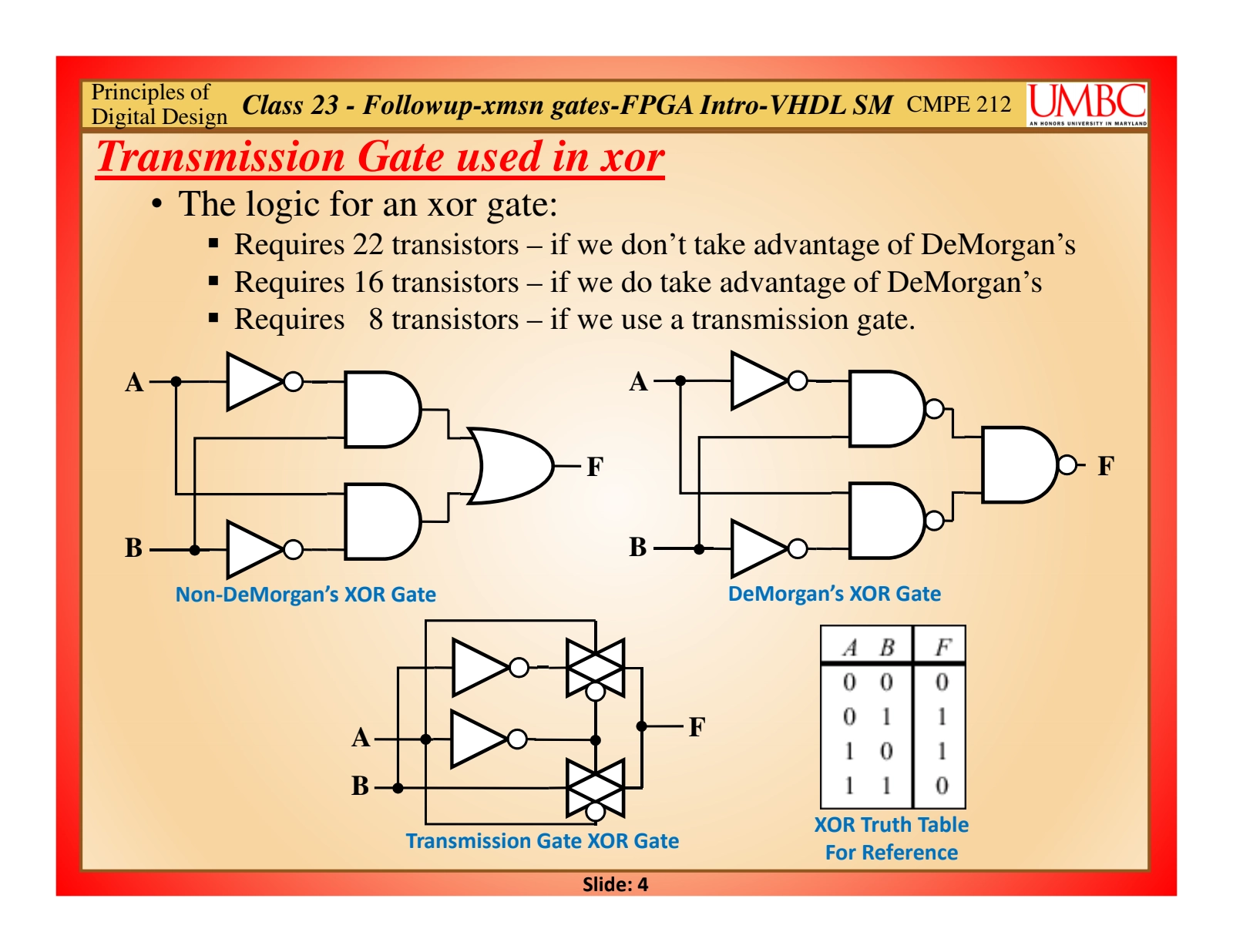

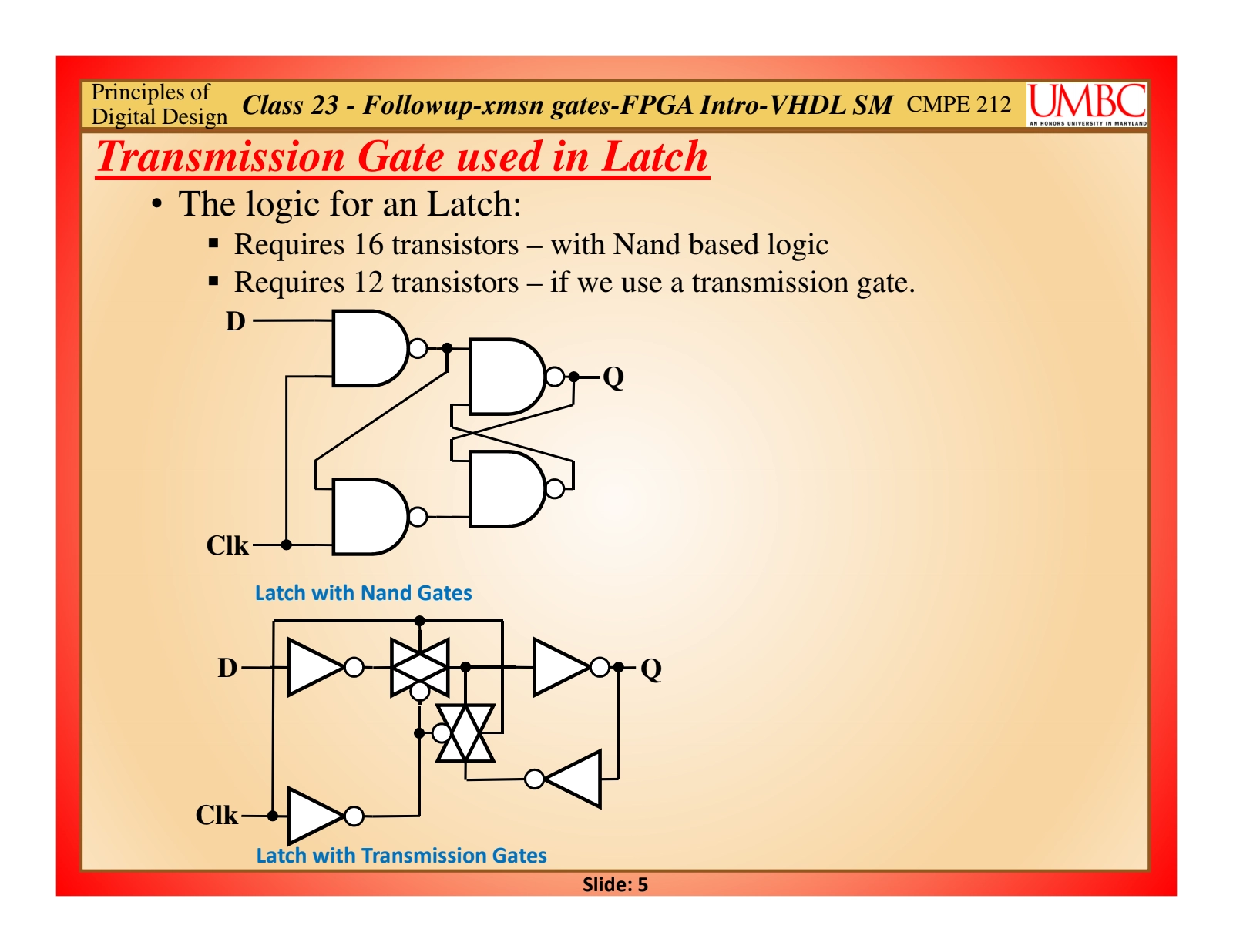

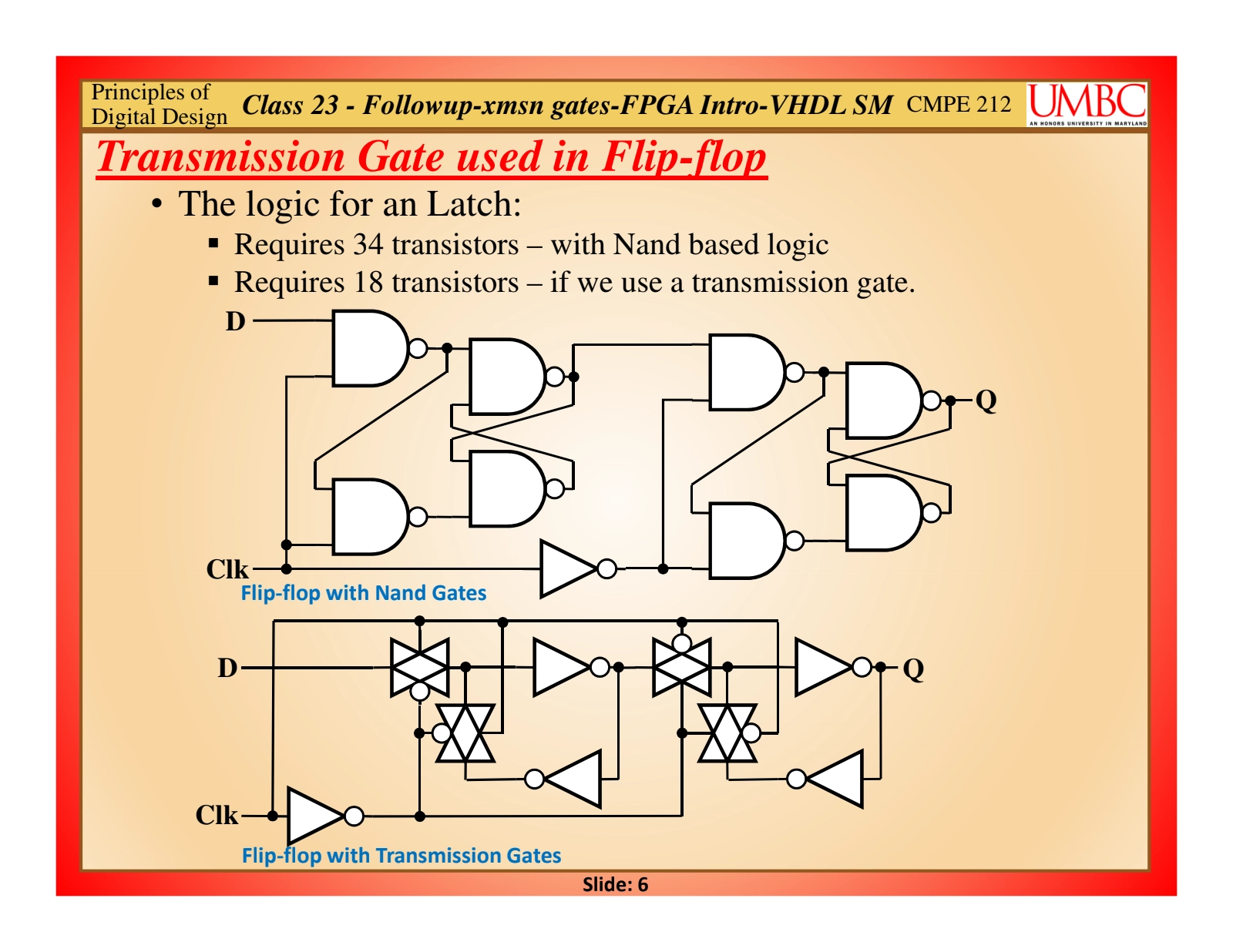

class: 23, slide: 4-6 → Transmission Gates used in Basic Logic

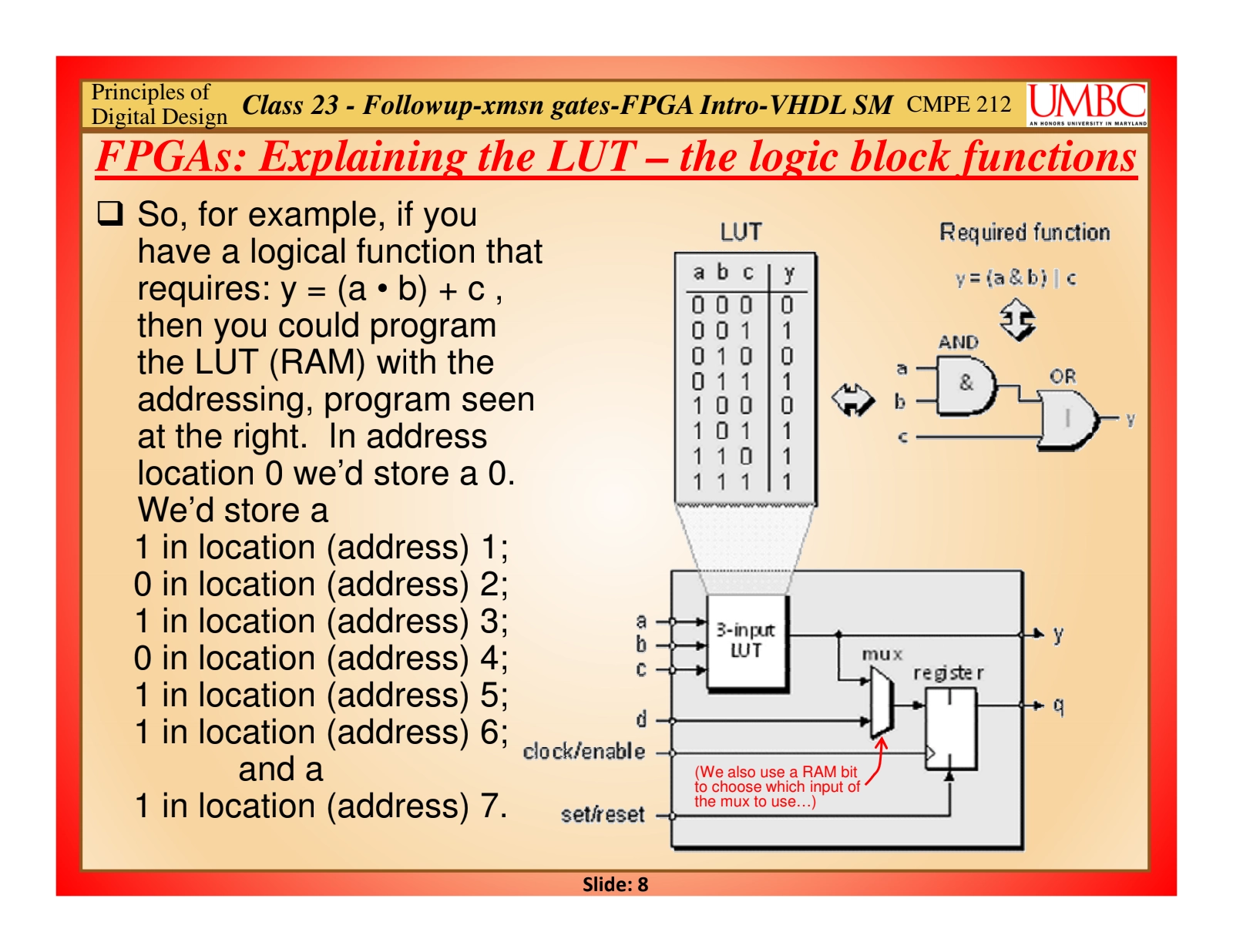

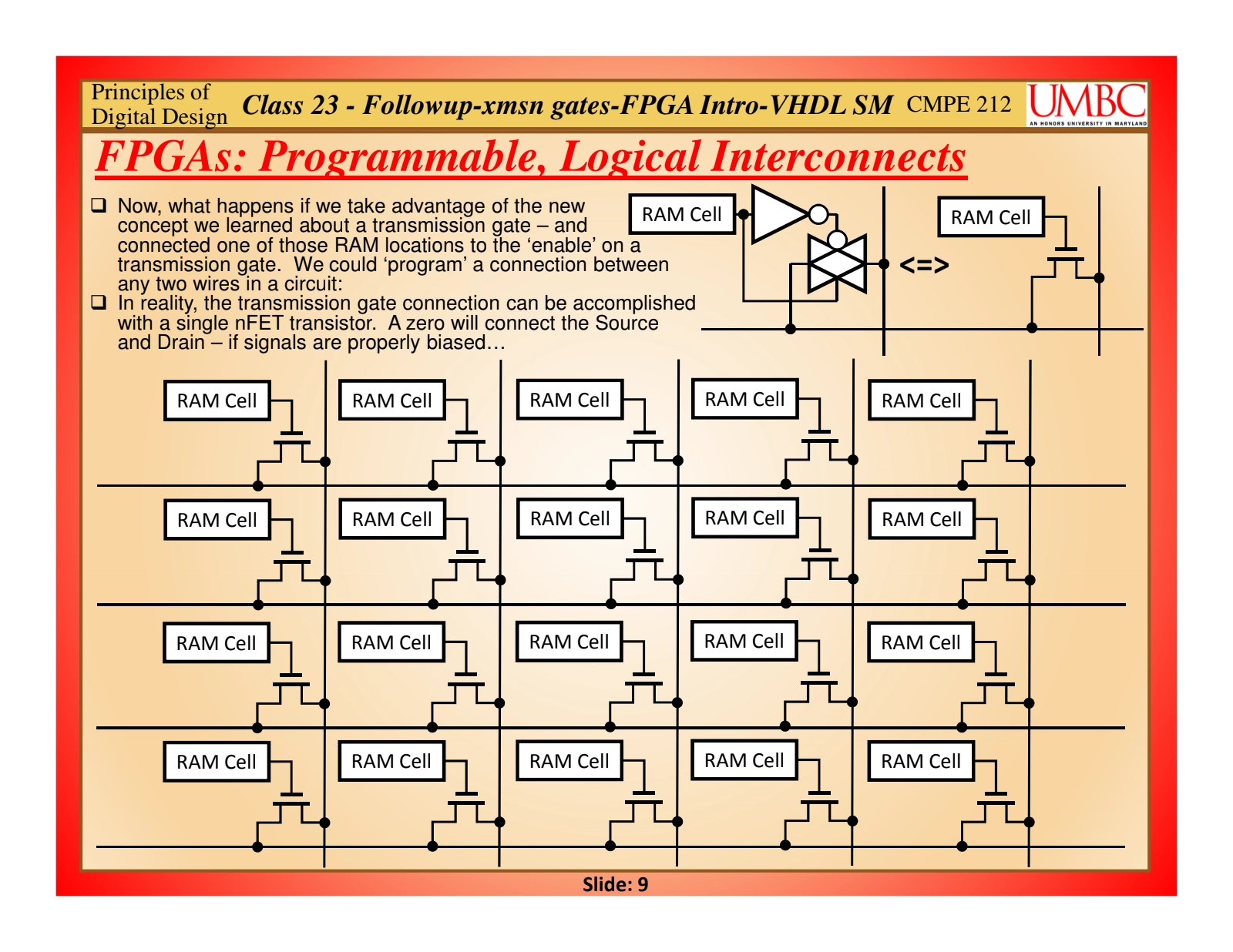

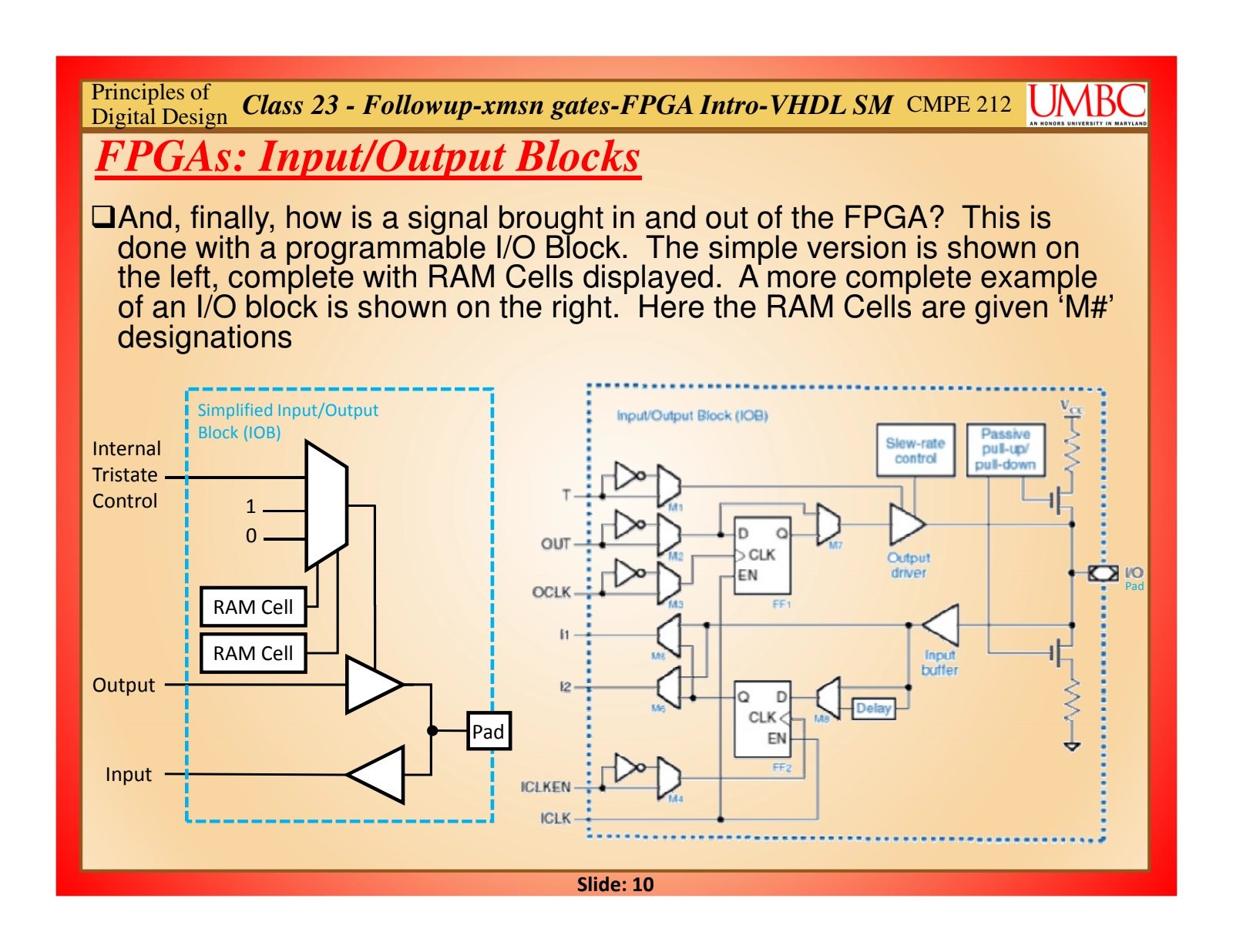

class: 23, slide: 8-11 → FPGA Basics, Expanded

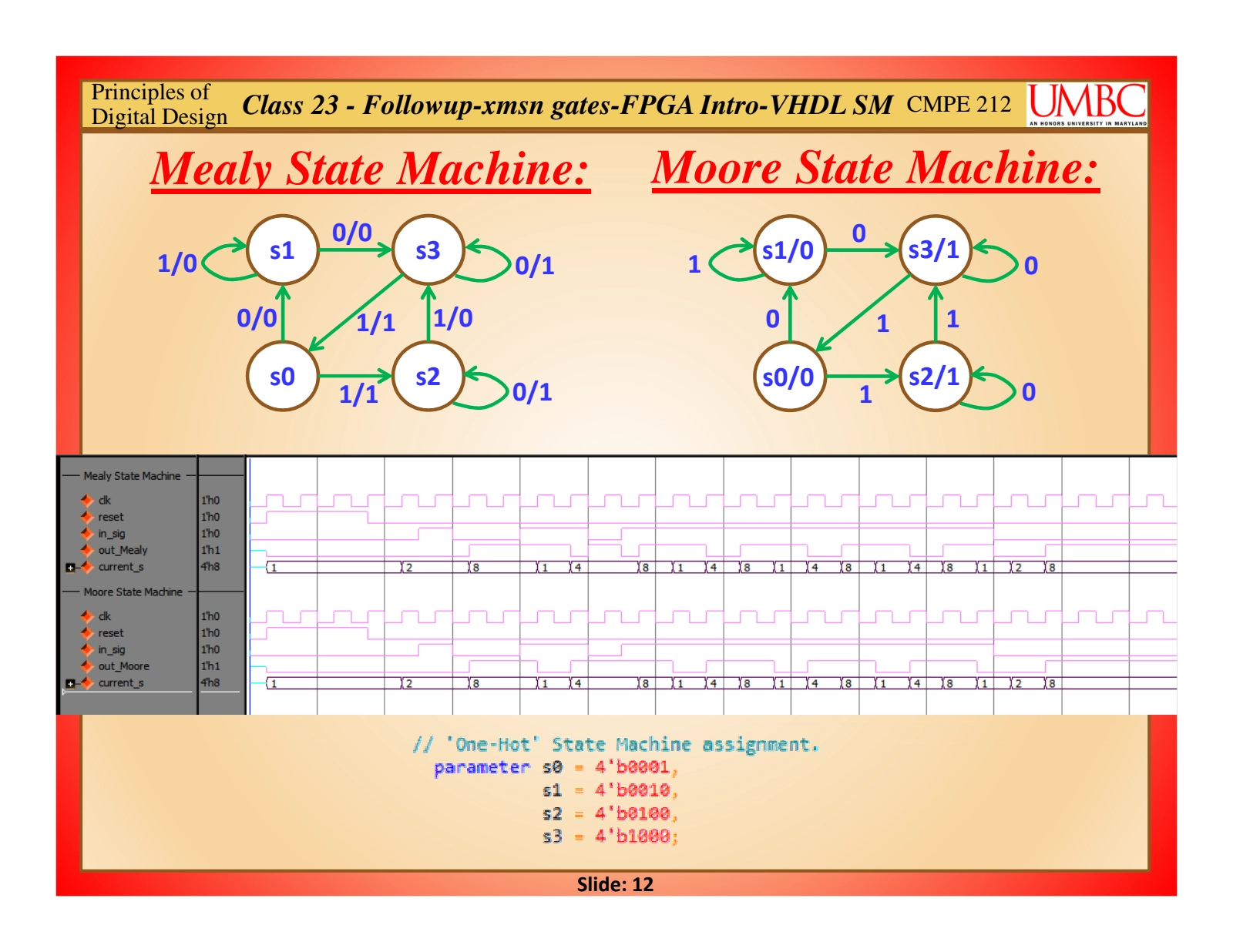

class: 23, slide: 12 → Mealey and Moore, yet again...